RAM (Random Access Memory)

온전한 8 bit latch 회로가 바로 RAM

- 3-to-8 decoder와 8-to-1 selector로 구성

- 3 Address가 있으면 8개 중 하나의 비트를 선택해서 쓰거나, 읽을 수 있음

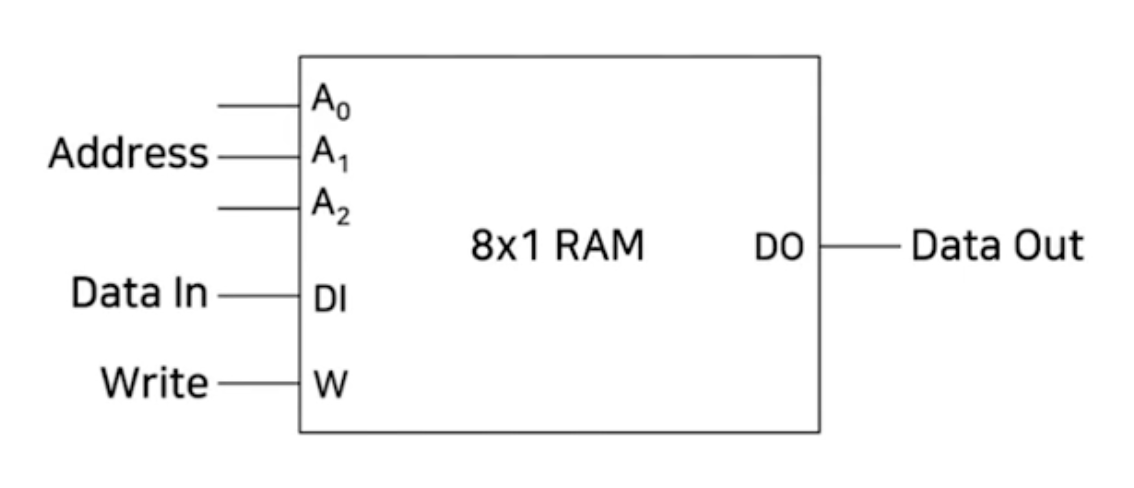

8 X 1 RAM

8개의 비트 중 1개의 특정 비트를 쓰고 읽을 수 있는 메모리

특징

- Memory : 데이터를 저장할 수 있음

- Read/Write : 특정 공간에 새로운 데이터 저장, 읽기 가능

- Random Access : Address 지정을 통해 특정 공간 값 접근 가능

- 반면 어떤 메모리는 순차 접근만 가능

- ex) 100주소를 읽기 위해 99를 읽어여함

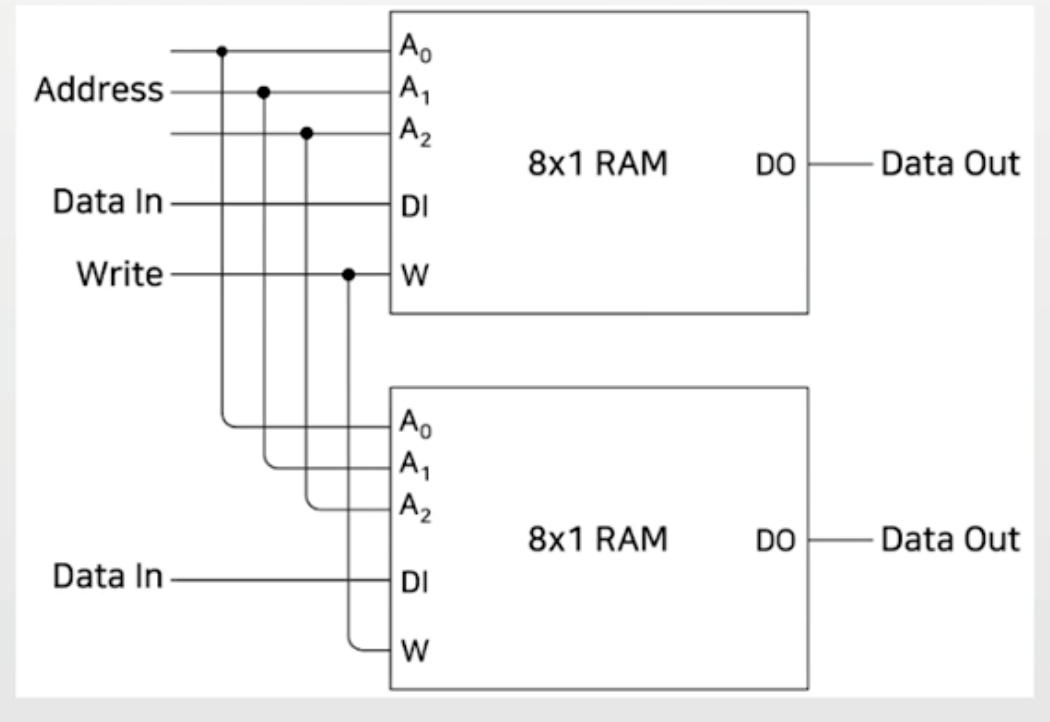

RAM array

RAM 을 여러 개를 추가했다는 의미

- Data In은 각 8 X 1 RAM에 별도로 입력이 들어감

- Address와 Write는 두 8 X 1 RAM에 동일하게 입력이 들어감

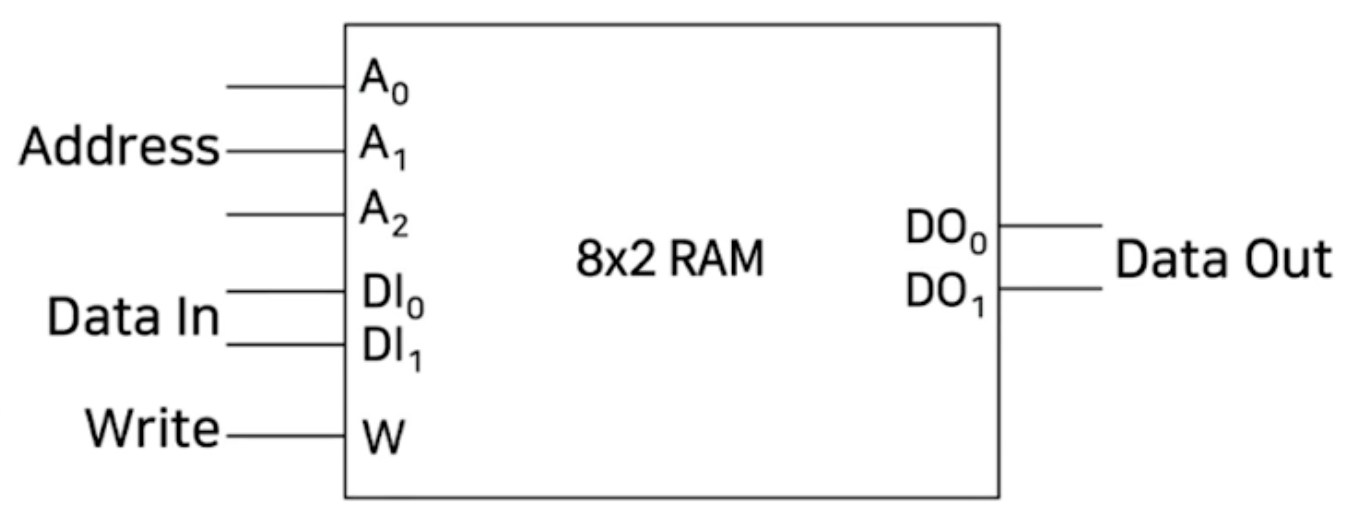

8 X 2 RAM

8 개의 데이터를 저장하고 읽는데, 각 데이터는 2 bits 이다.

- 8 × 1 RAM은 하나의 bit만 쓰고 읽을 수 있음

- 8 × 1 RAM을 두 개 연결하면 8 * 2 RAM array가 됨

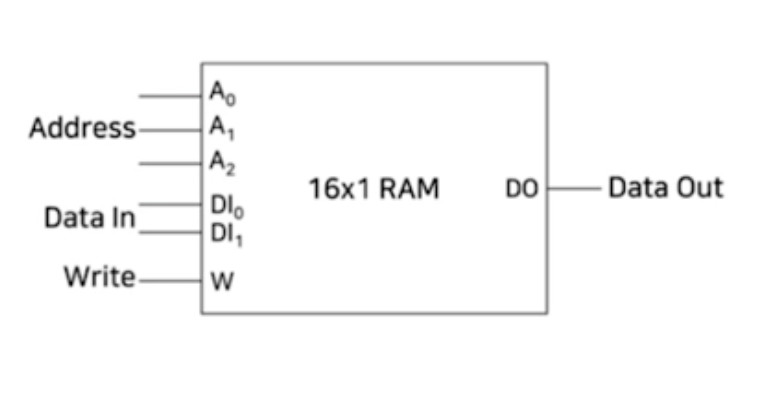

16 X 1 RAM array

- 8 X 2 RAM array 구조에, Select와 1-to-2 Decoder/2-to-1 Selecotor 추가

- Select는 4번 째 Address 역할을 함

- 16개의 데이터를 저장하고 읽는데, 각 데이터는 1 bit가 됨

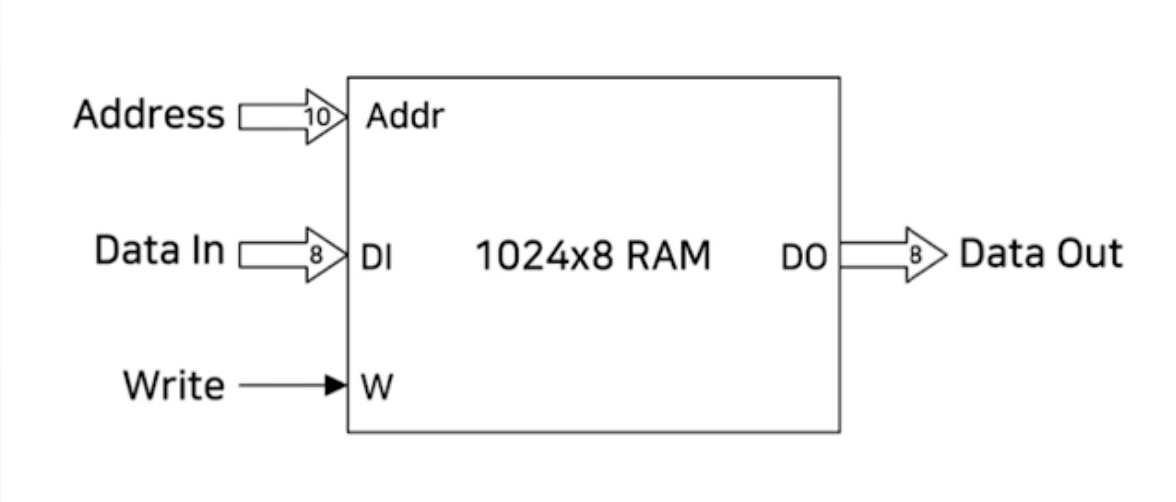

m * n RAM array

많은 데이터를 저장하는 RAM array

- 8 X 1 RAM을 여러개 연결하고, 여러 개의 Select로 Decoder/Selector를 구성하면 많은 데이터를 읽고, 저장할 수 있음

EX

- Address 10개 : 2의10승 -> 1024

- DI 8개 : 1 byte(8 bits)

- 1024 X 8 bits = 8196 bits를 다루는 RAM array

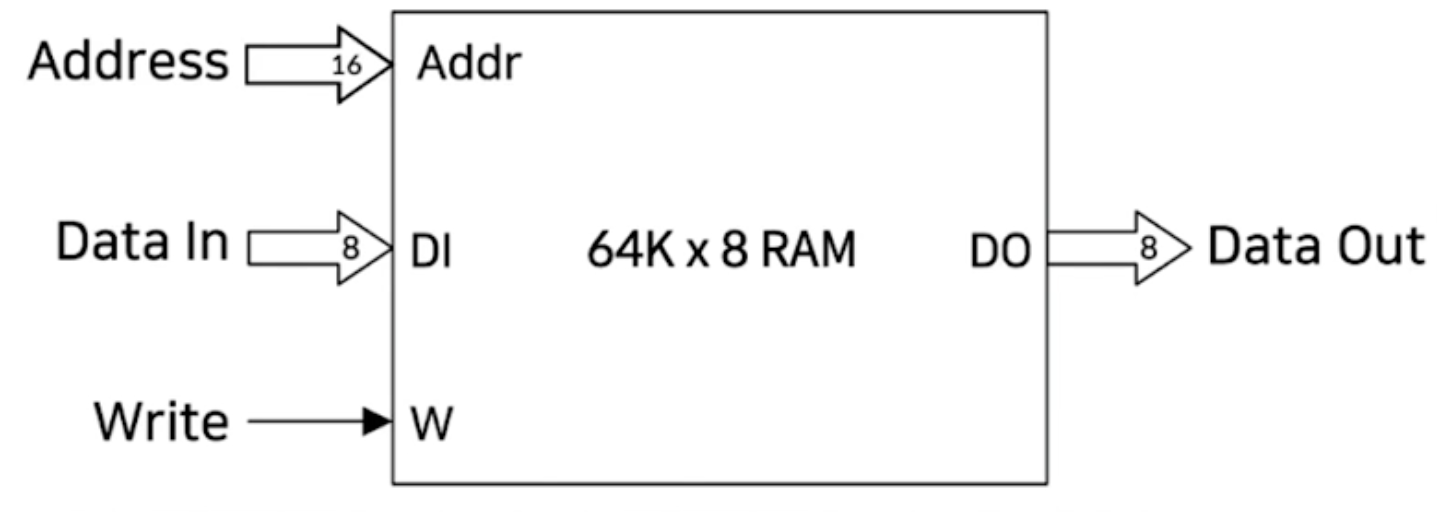

64K RAM

- Address 수 / Data In / Out 수 로 RAM array 만들기

- 65,536(2의16승) X 8 bits