Dataflow Descriptions

입력과 출력의 관계를 기술한 설계방식으로, 문장의 순서와는 무관하게 신호가 들어오는 대로 진행한다. 병행처리문(Concurrent Statement)에 주로 사용한다.

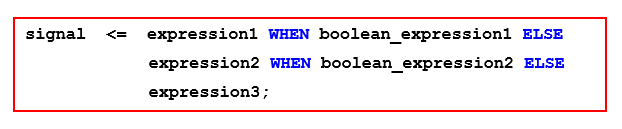

when / else

1) boolean_expression1 = 참(True)이면 signal <= expression1이 실행

2) boolean_expression2 = 참(True) 이면 signal <= expression2이 실행

3) 위의 2가지 조건이 모두 성립하지 않으면 signal <= expression3이 실행된다.

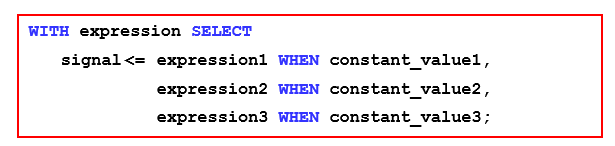

with select / when

1) expression = constant_value1 이면 signal <= expression1이 실행

2) expression = constant_value2 이면 signal <= expression2이 실행

3) expression = constant_value3 이면 signal <= expression3이 실행

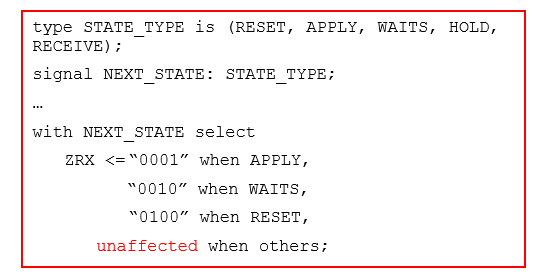

The Unaffected Value

type은 사용자가 직접 지정하는 변수로, 위 그림에서 (RESET, APPLY, WAITS, HOLD, RECEIVE)개 중 하나의 상태를 가질 수 있다. 여기서 APPLY, WAITS, RESET을 사용하면 값이 바뀌게 된다. 3개 이외의 값을 사용하면 Unaffected를 통해 기존에 값을 계속 사용하게 된다.

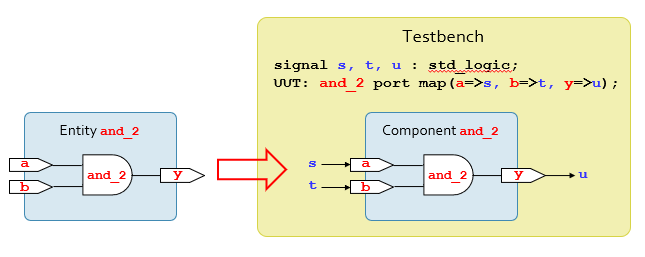

Design source와 Simulation source

Design source가 잘 짜여졌는지 확인하려면 simulation을 해야한다. 하는 방법은 다음과 같다.

- 시뮬레이션 소스(testbench) 내부에 디자인 소스를 부품(component)으로 불러와서 시뮬레이션 실행

- 시뮬레이션 소스 내부에서 사용할 signal들을 선언하여 디자인 소스의 입/출력 포트들과 port map 명령어를 통해 맵핑한 후, 입력 포트에 맵핑된 시그널에 입력 값을 설정하여 시뮬레이션 실행

예시에서는 a를 s에, b를 t에, y를 u에 할당(mapping)했다. 앞에 있는 것은 component port이고, 뒤에 있는 것은 signal이다. 순서가 바뀌면 안된다.

Structural Descriptions

구조적 표현은 우리가 만든 디자인을 하드웨어의 구조로 표현하는 방식이다. 우리가 design source를 simulation source로 실행할 때, simulation source가 structural descriptions이라고 할 수 있다. 아래와 같은 특성을 지닌다.

- 가장 하드웨어적 표현에 가까움

- 구성 요소 및 연결까지 표현

- Graphic Editor를 이용한 고전적인 schematic 설계방식과 동일.

- component 문을 이용하여 선언

- port map 문을 이용하여 핀들을 서로 연결

- 위치결합(positional association)

- port map 내의 signal의 위치순서대로 나열

- 이름결합(named association)

- port map 내의 signal의 위치순서와는 상관없이(port 의 형식이름 => 실제 이름) 의 방식으로 결합

- 대부분의 경우 이름결합을 많이 사용함

- 위치결합(positional association)