latch

- s,r을 통해 결과값 q를 도출

- gated-latch: clock이 특정한 값을 유지하고 있는 경우 값이 변함

sr latch(nor latch)

- set, reset을 통해 q값을 정함

- clock 0: q(t) - hold

- clock 1

- 00 --> hold: 이전 값 유지

- 01 --> reset

- 10 --> set

- 11 --> 불안정한 상태, 입력 금지

- q, q' 둘다 0이 나옴 --> q, q'는 서로 반대 값이 나와야 함

- sr:11 --> 00으로 바꾸는 경우 어느쪽 부터 바꾸냐에 따라 결과 값이 다르게 나오므로 불안정함

- nand로 만드는 경우

- sr 다 반대임

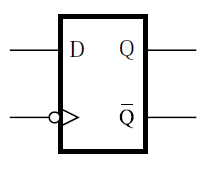

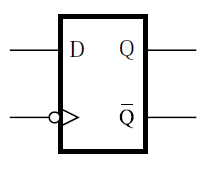

d latch

- sr latch에서 불안정한 1,1의 상태를 예방하기 위해, 인풋을 하나로 놓으면서 아예 막아버린 회로

- clock 1인 경우: d값을 그대로 출력

- clock 0: q(t) - 이전의 값 유지

latch timing problem

- clk 1인 경우 입력 상태가 변하면 출력 상태도 계속 변하는 문제 존재

- shift register의 경우 한 clk당 한 비트가 옮겨지는 것이 아니라 clk가 1인 동안 계속 값이 이동하는 문제 발생

flip-flops

- latch는 clock이 1인 경우 입력상태가 변하면 출력 상태도 계속 변하는 문제점 존재

- clock-edge에서 값이 변함

sr flip-flops

d flip-flops

- d latch 2개 연결(D값 그대로 나옴)

- positive-edge: 0 --> 1 로 바뀔 때 d값 반영

- negative-edge: 1 --> 0 으로 바뀔 때 d값

- 기호에서는 삼각형이 있으면 flip-flop이고, clk가 있으면 latch임

- positive-edge: 삼각형

- negative-edge: 삼각형 + 버블

jk flip-flops

- d, t flip-flops 두가지 모두를 가진 것

- 값

- 0 0: q(t) - hold

- 0 1: 0 - reset

- 1 0: 1 - set

- 1 1: q(t)' - toggle

t flip-flops(toggle)

- t 0: q(t) - hold

- t 1: q(t)' - toggle

- d, j, k 보다 우선 순위가 높음(우선순위 가장 높음)

- preset/set: q --> 1 ==> preset 0으로 만드는 것 아님, 헷갈리지 않기!

- clear/reset: q--> 0

- synchronous vs asynchronous

- asyn: 게이트에 바로 연결 해서 clk에 관계없이 작동

- syn: 게이트 인풋과 연결하여 clk에 따라 작동 됨

flip-flop equation

- 카르노 맵을 통해 식을 추론 해낼 수 있음

- jk ff

- q* = JQ' + QK'