i/o

- cpu/메모리와 외부 장치간 정보를 주고 받는 것

- 특징

- behavoir: input(Read only), output(writre only), storage

- partner: 인간, 기계

- data rate: 주어진 시간 내에 옮겨진 데이터의 량

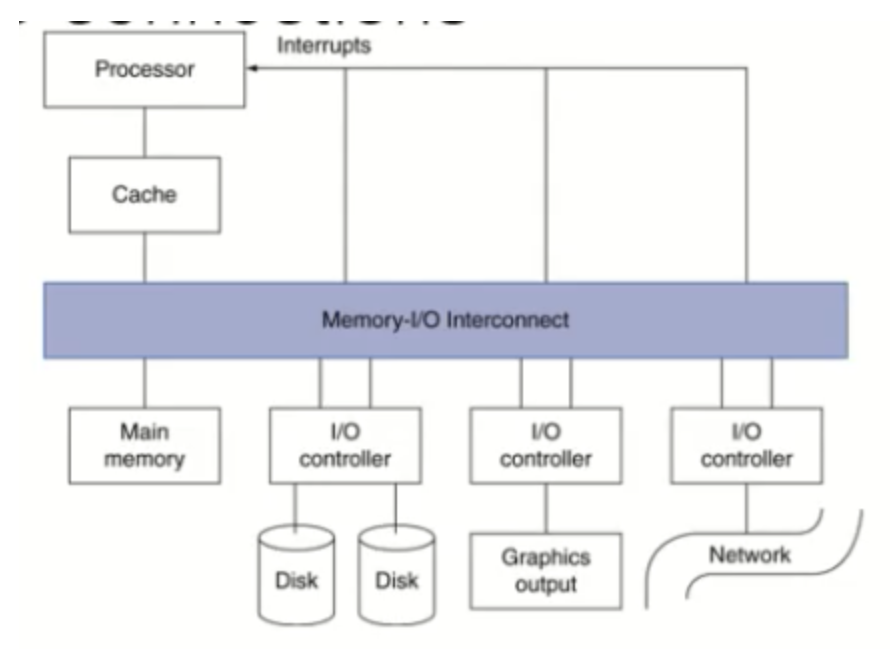

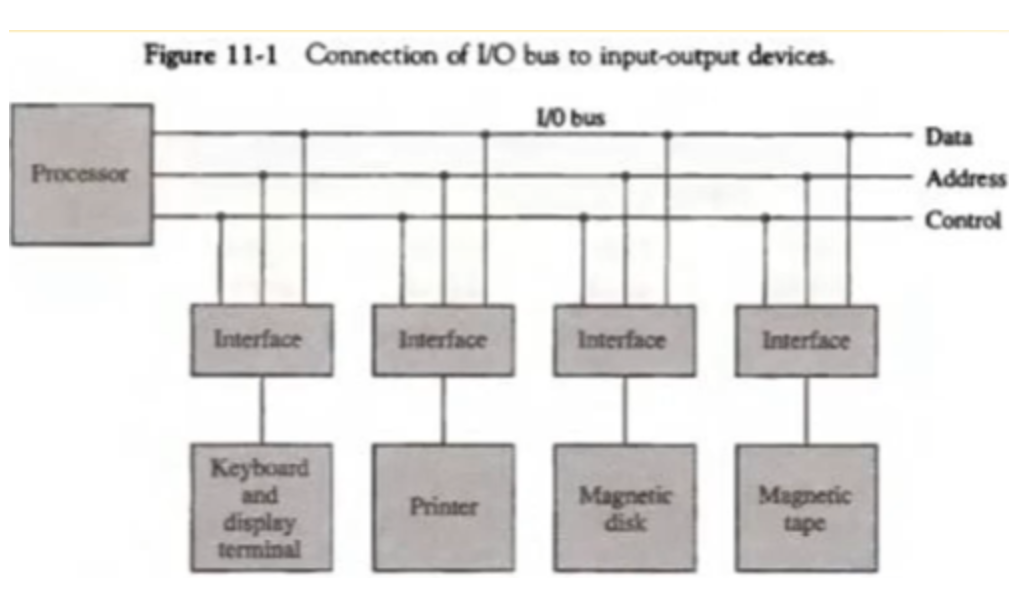

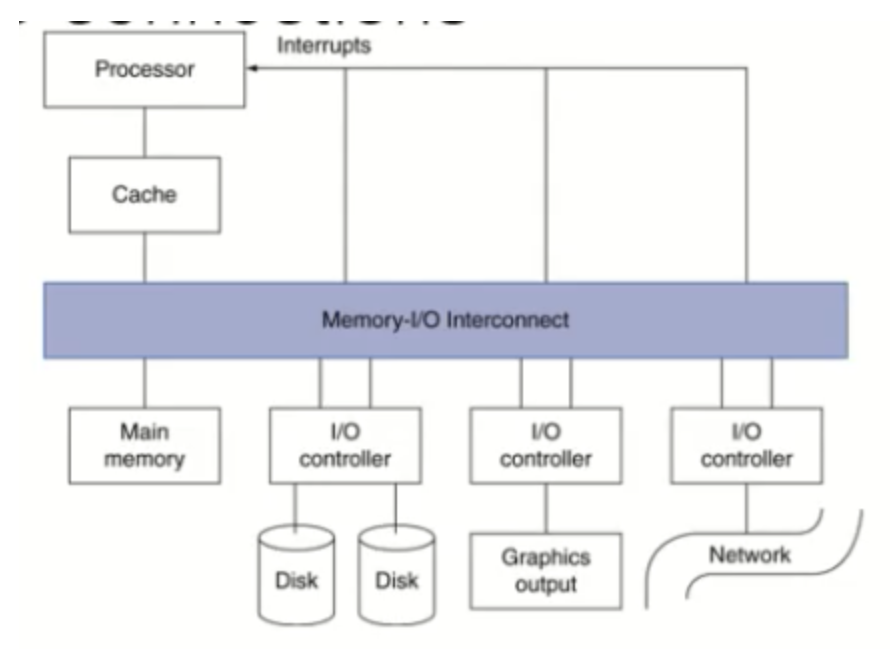

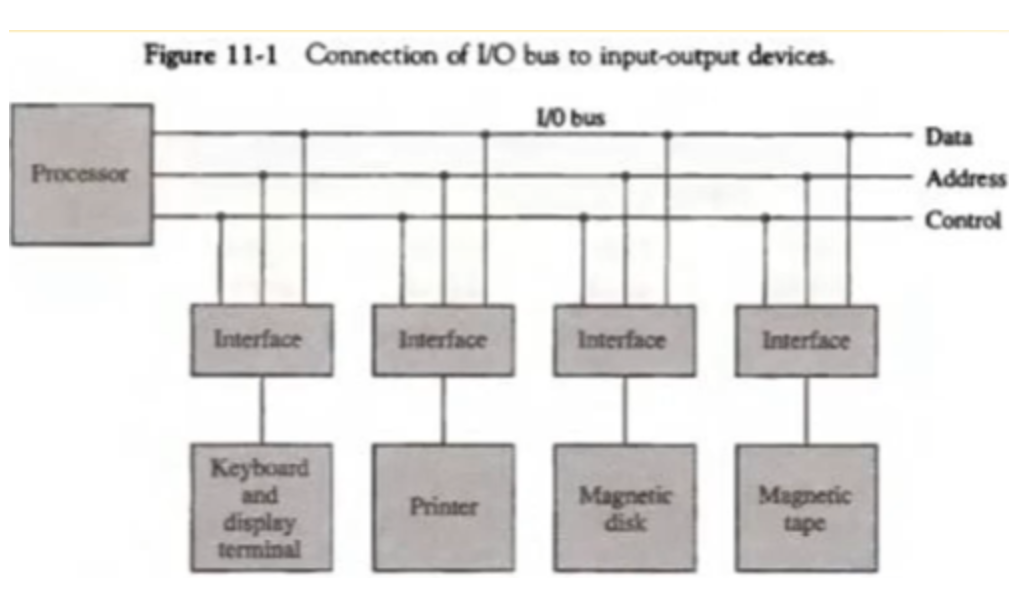

- i/o bus connection

- cpu와 i/o 디바이스는 Memory-I/O Interconnect로 연결

- 디바이스는 cpu에 interrupt를 걸어 요청을 처리

disk

- 자기적인 성질을 이용한 보조기억 장치

- 목적

- 비휘발성

- 크고 값싸고 느림

- 메모리 가장 낮은 계층

- 종류

- 하드디스크

- 개념

- 금속 원판의 표면에 자성 입힘

- 저장 용량 크며 고속으로 작동

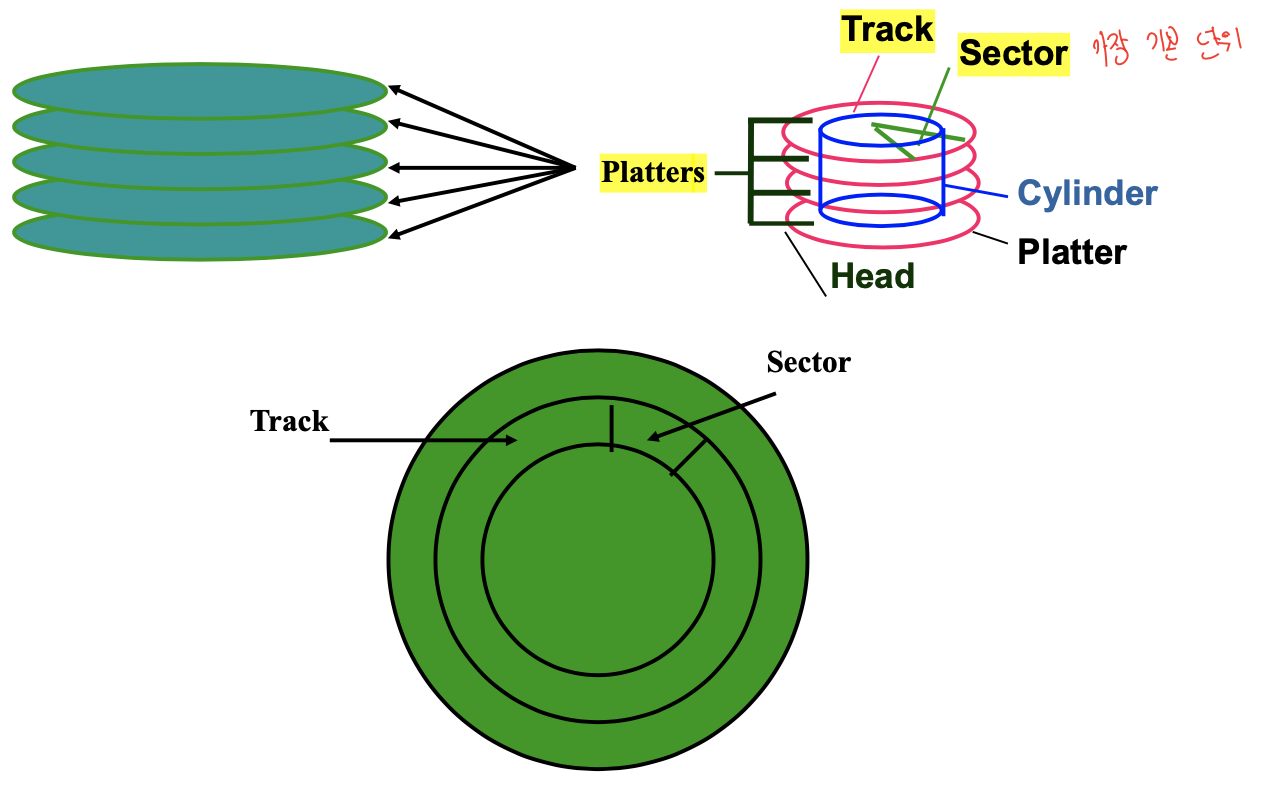

- 구성

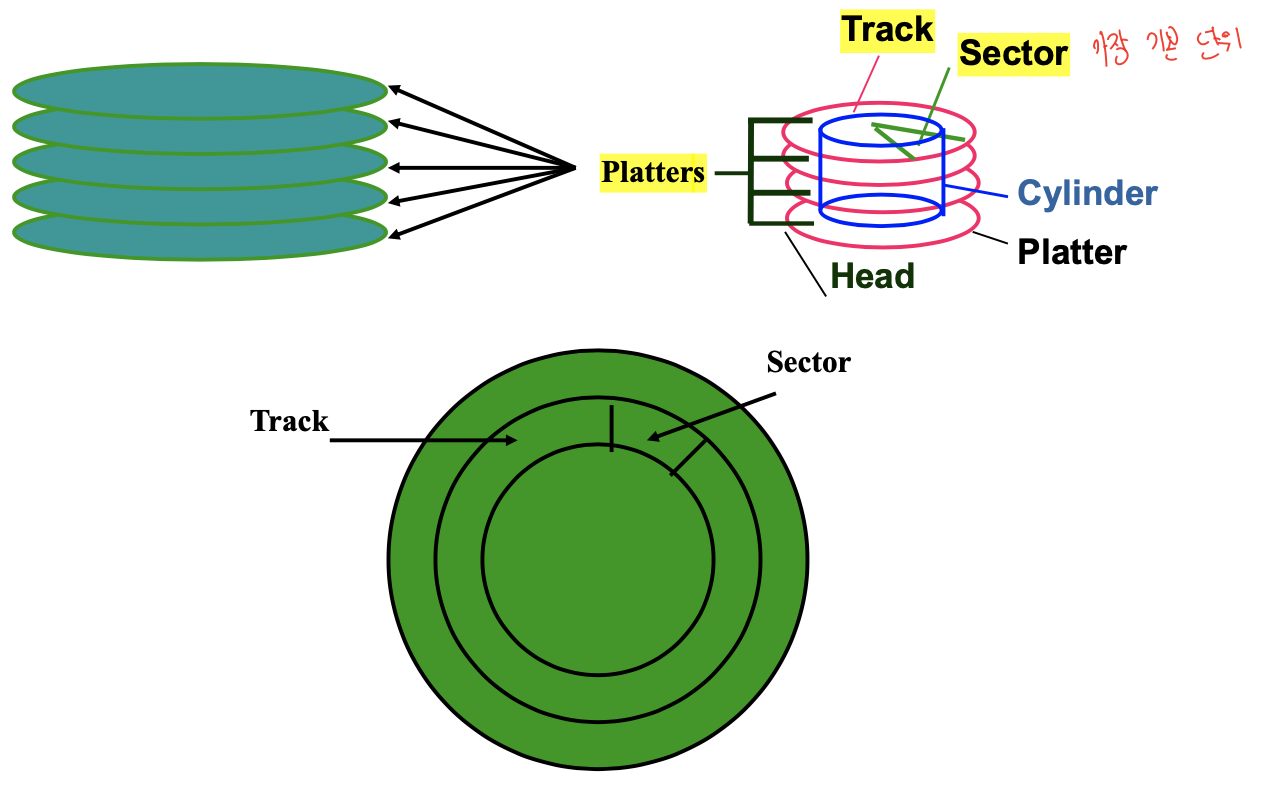

- 트랙

- 하나의 원으로 구성된 기억 공간

- 표면 당 500 ~ 2000 트랙 구성

- 섹터

- 원주 방향의 트랙을 구성하는 기억 공간 단위

- 트랙 당 32 ~ 128 섹터로 구성

- 읽고 쓸 수 있는 가장 작은 단위

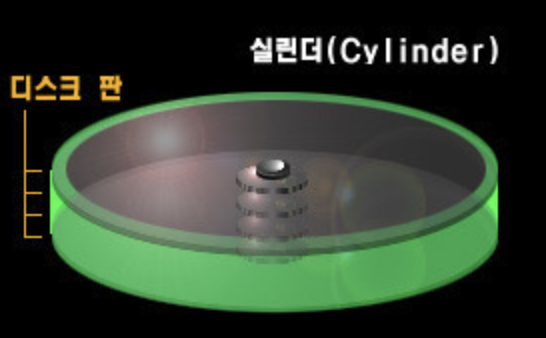

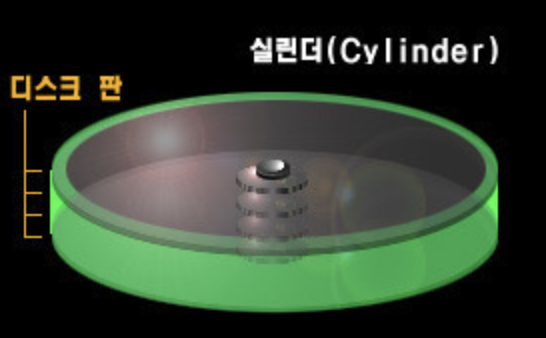

- 실린더: 동일한 틀번호를 가지고 있는 트랙

- 클러스터: 운영체제의 의하여 할당되는 디스크 공간의 단위

- dos에서 하드 디스크 --> 보통 4개 또는 8개의 섹터가 하나의 클러스터 구성

- 디스크 접근 시간 3가지 요소

- seek time: 적절한 트랙에 head를 놓는 시간

- rotational latency: 원하는 섹터까지 기다리는 시간

- transfer: 데이터 grab

- 디스크 어레이

- 하드디스크를 엮어 하나의 논리 드라이브로 구성

- raid(Redundant Array of Inexpensive Disks)

- 여분의 디스크 추가한 디스크 어레이

- mttr: 수리하는데 걸리는 시간

- mttf: 고장나는데 걸리는 시간

- 플래시 메모리

- 개념

- 전기적으로 데이터를 지우고 다시 기록할 수 있는 비휘발성 컴퓨터 기억장치

- 디스크 대체 후보임 --> 지연 시간 100 ~ 1000배 디스크보다 빠름

- 장점

- 비휘발성: 전원을 꺼도 데이터가 남음

- 작고 가벼우며 충격에 강함

- 하드디스크와 달리 물리적으로 움직일 필요x --> 검색 시간 짧음

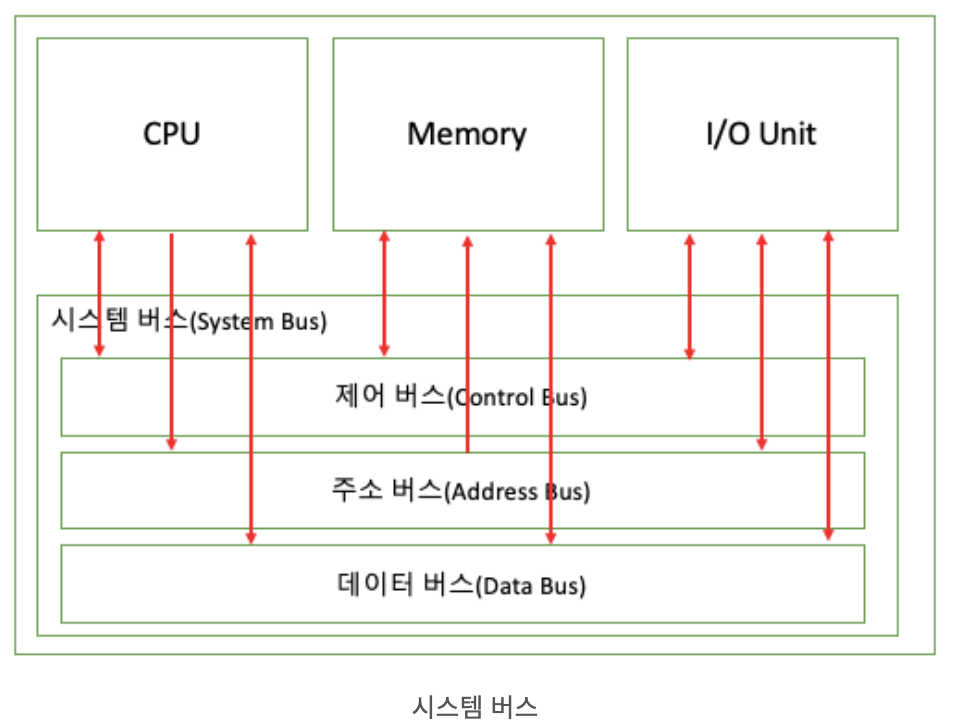

bus

- 개념

- 컴퓨터 시스템 내 하드웨어들 간에 정보 전달을 위한 통로

- 전기를 신호를 전달하는 금속 선의 묶음 형태

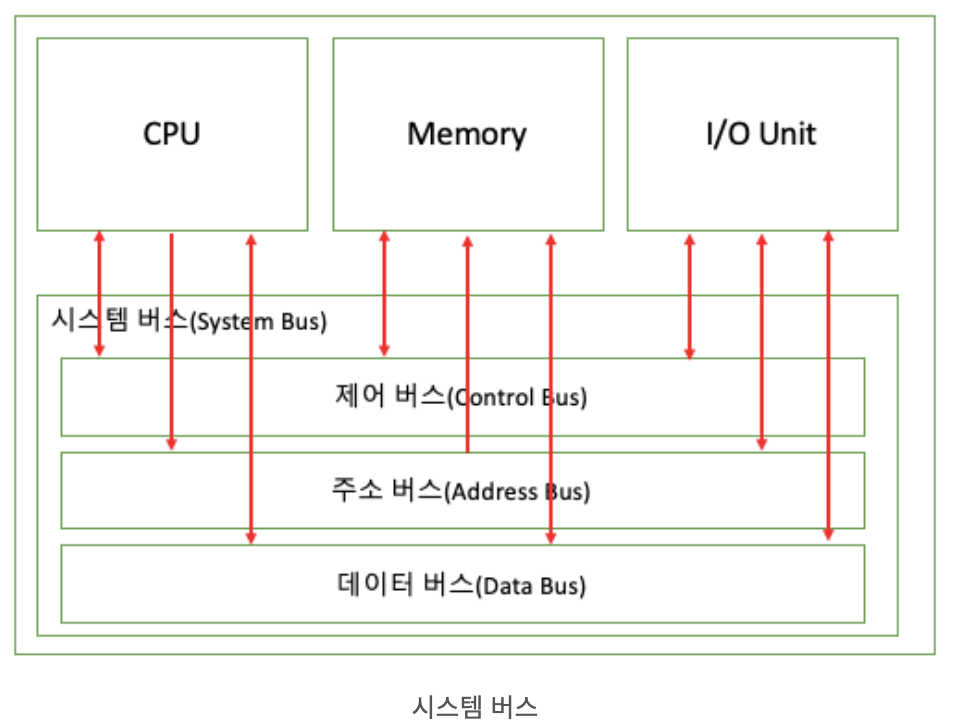

- 종류

- 데이터 버스

- 데이터 전달

- 각 구성요소(cpu, memory, i/o unit)는 양방향으로 데이터 전달 가능한 버스 사용

- 주소 버스

- 메모리 주소, i/o unit의 포트 번호 전달

- cpu와 memory는 단방향으로 데이터 전달이 가능한 버스 이용 --> 주소 전달은 cpu에서 메모리로만 가능

- cpu, memory는 i/o unit과 양뱡항으로 데이터 전달이 가능한 버스 사용

- 제어 버스

- 제어 신호 전달

- read와 write 신호 전달

- 각 구성요소는 양방향으로 데이터 전달 가능한 버스 사용

- 버스 마스터와 중재(Bus arbitration)

- 버스 마스터: 시스템 버스를 사용하는 주체

- 중재: 버스를 이용하려는 마스터 둘 이상인 경우 --> 우선순위가 높은 마스터 선정

- 시스템 버스는 한 번에 하나의 마스터만이 이용 가능

- 버스 중재기: 버스 중재를 전담하는 장치

- 중재 버스

- 버스 중재기와 버스 마스터 간에 버스 중재를 위한 신호 --> 제어버스 통해 전송

- 제어 버스 중 버스 중재에 사용되는 선들의 집합

- 중재 방식

- 유의 사항

- bus priority:높은 우선 순위가 먼저 서비스 받도록

- fairness: 낮은 우선 순위 장치가 기회가 오도록

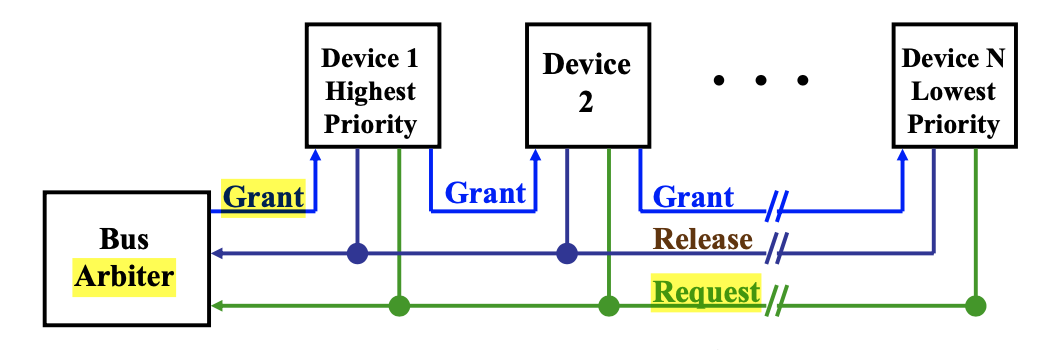

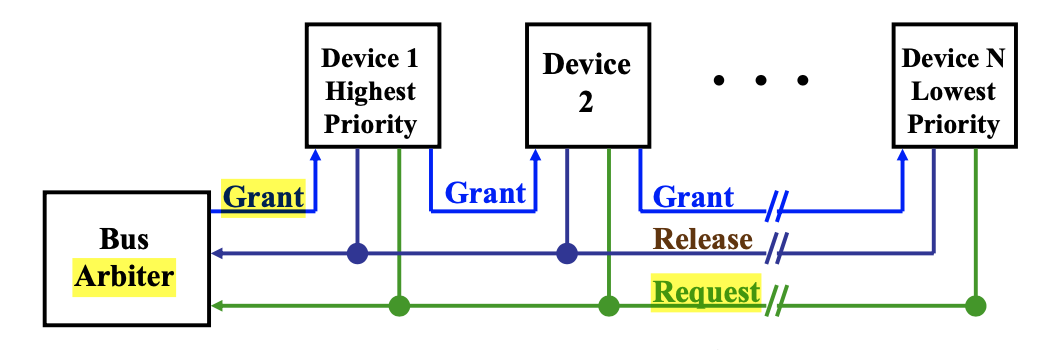

- daisy chain

- 1개의 request line 존재

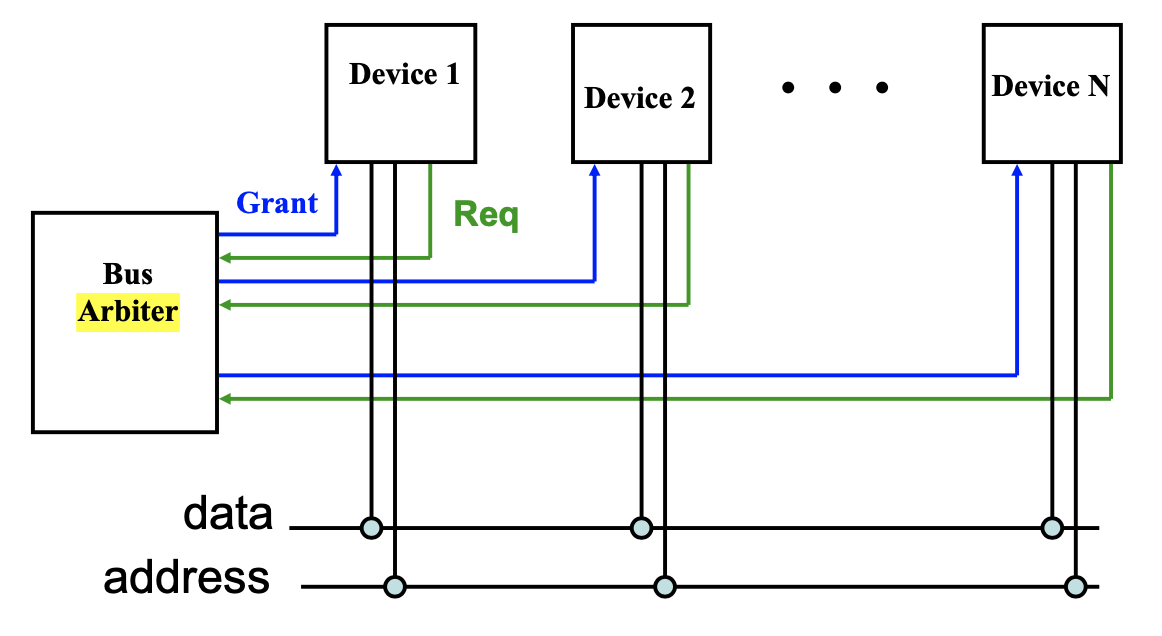

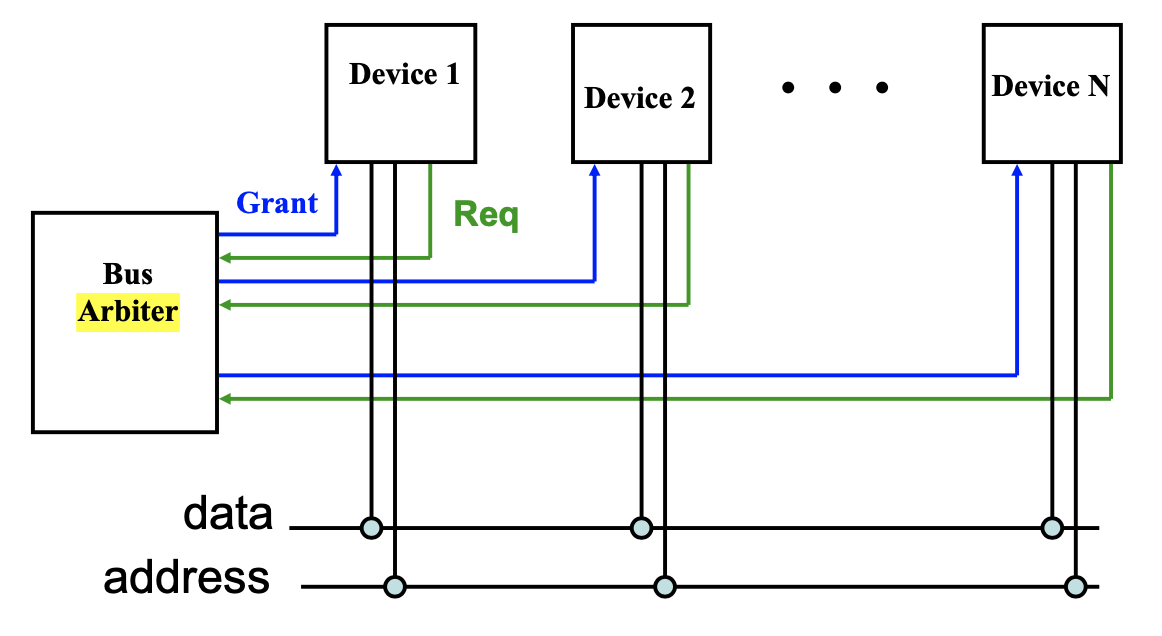

- centralized, parallel

- 여러개의 request lines 존재

- self-selection arbitration

- device 본인 우선 순위 따라 선택

- collision detection arbitation

- 여러개 버스에서 request 보내 충돌 --> 잠시 wait 후 다시 request

- 중재 종류

- 버스 요구(bus request, breq)

- 임의의 버스 마스터가 중재기에 버스 사용을 요구하는 신호

- 버스 승인(grant)

- 중재기가 breq 신호 받았을 때 마스터에게 요구 승인을 알리는 신호

- 버스 사용 종료(release)

- 버스 사용이 끝난 후 중재기에게 신호를 보내야함

- 버스 사용중

- 임의의 버스 마스터가 사용을 요구 했을 때 이미 다른 버스 마스터가 버스를 사용중임을 알리는 신호

- 인터럽트 버스

- 제어 버스 중 인터럽트를 위한 버스선들

- 종류

- 인터럽트 요구

- 인터럽트 확인

- 동기식 버스와 비동기식 버스

- 동기식 버스(synchronous bus)

- 버스의 공통 클럭에 따라 모든 버스 동작들 발생

- 비동기식 버스(asynchronous)

- 버스의 공통 클러과 상관없이 다른 버스 동작의 발생 여부에 따라 동작들 발생

입출력 구조

- 입출력 인터페이스 기능

- 모든 디바이스는 인터페이수 가짐 --> bus를 통해 cpu와 통신

- cpu는 빠르고 io장치는 느림 --> 이를 연결 하는 것이 인터페이스

- 입출력 방식

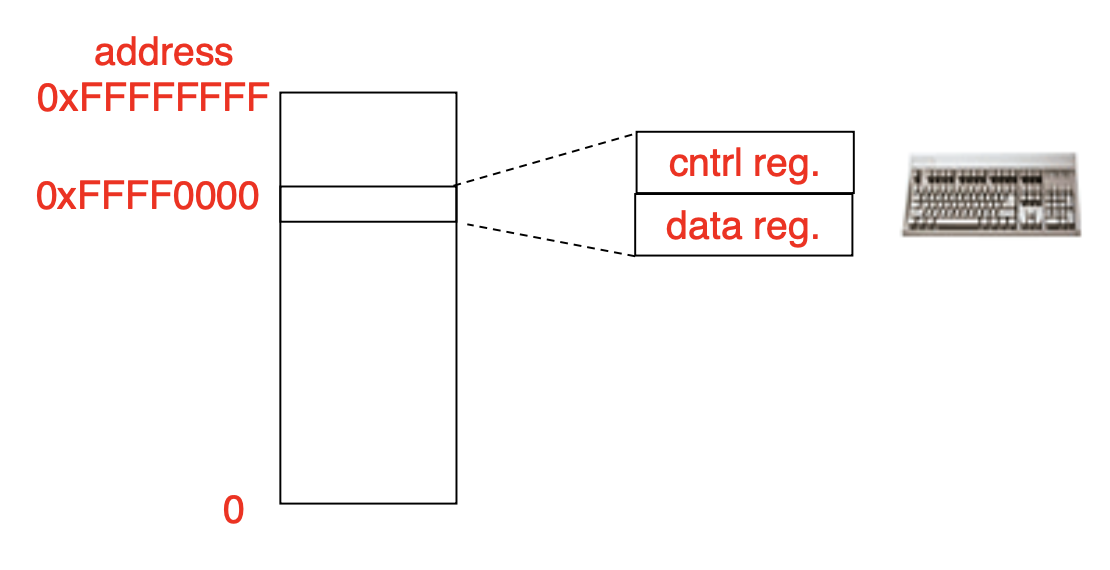

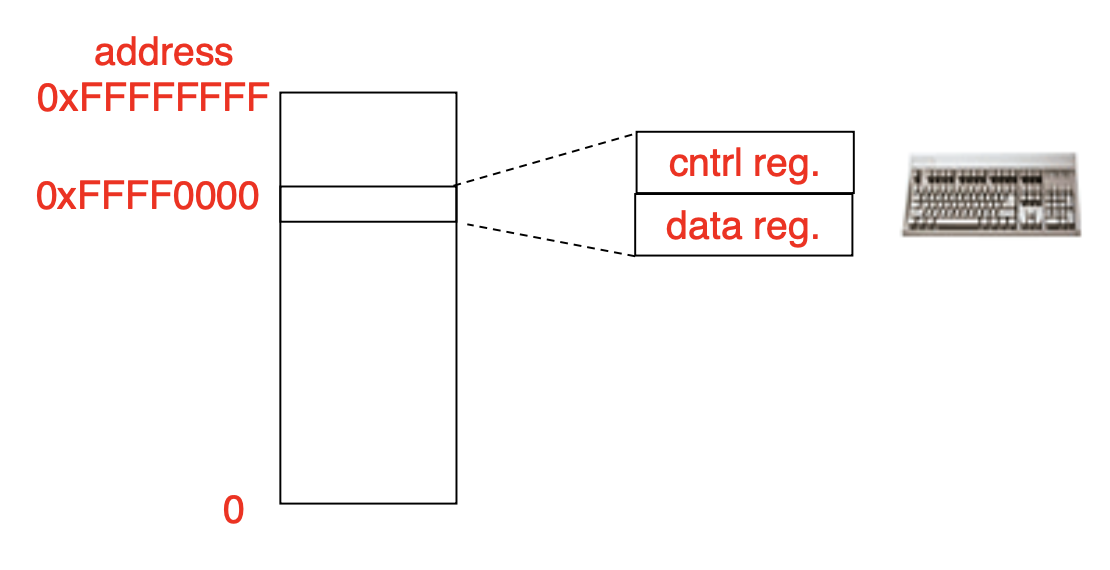

- memory mapped i/o

- cpu가 입출력 장치 접근시, 입출력과 메모리 주소 공간을 분리하지 않고 하나의 메모리 공간에 취급하여 배치하는 방식

- disk block을 메모리의 페이지에 매핑 --> read(), write()와 같은 system call 대신 메모리에 데이터를 읽고 쓰는 것처럼 사용 가능

- 폴링(polling)

- cpu가 작업을 진행하다가 입출력 명령을 만나면 --> 직접 입출력 장치에서 데이터를 가져옴

- cpu가 직접 일을 하기 때문에 입출력을 하는 동안 다른 일을 못함 --> 입출력 처리 동안 기다려야 하므로 효율이 떨어져 현재느 사용x

- 인터럽트(i/o interrupt)

- 입출력, 하드웨어 문제 또는 프로그램 예외 등이 발생 했을 때 --> cpu에게 알려주는 방식

- 신호가 들어오면 인터럽프 소스를 실행하고 다시 원래 코드로 돌아옴

- 장점: 정확한 타이밍을 알 수 있음

- 단점: 구현이 복잡함

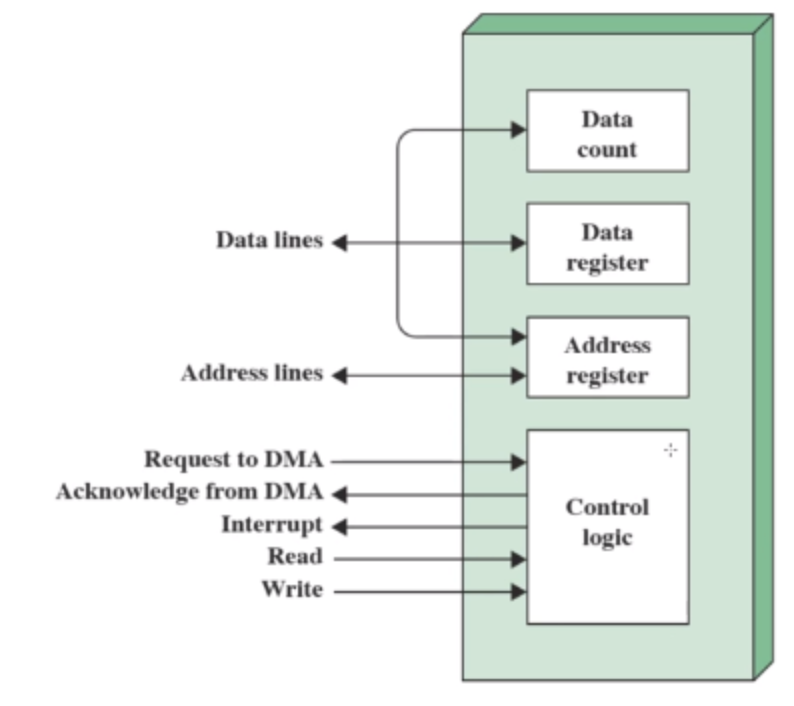

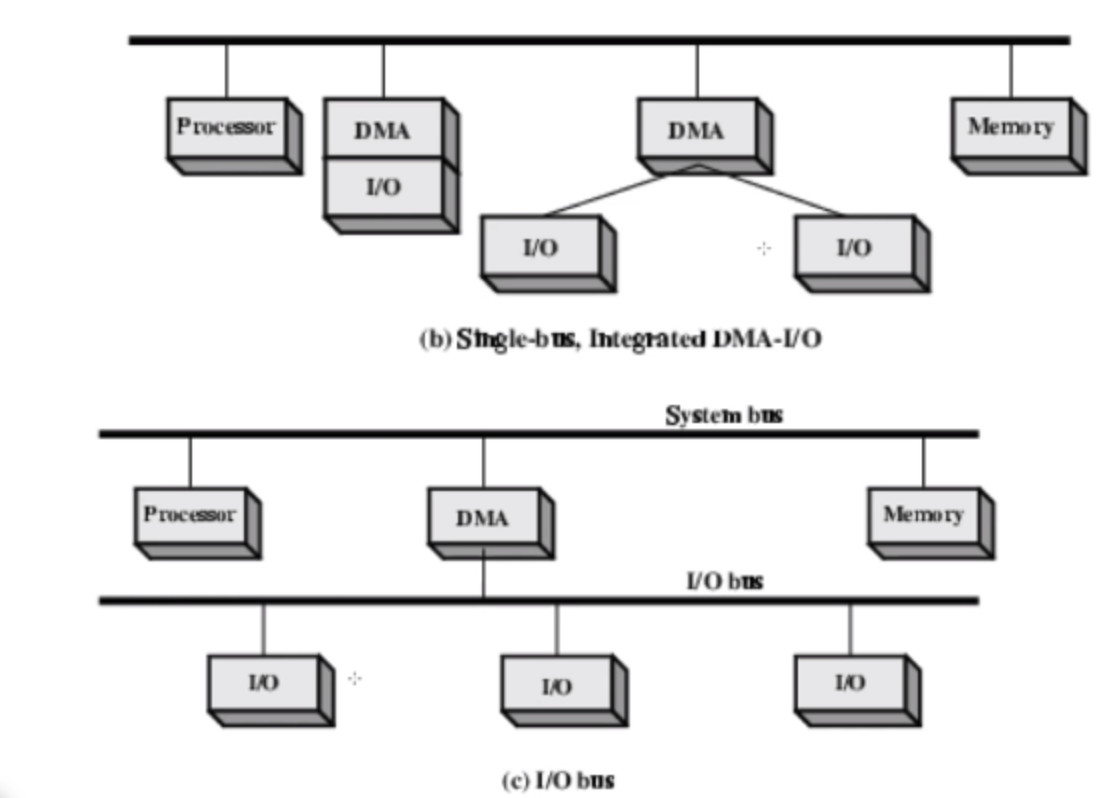

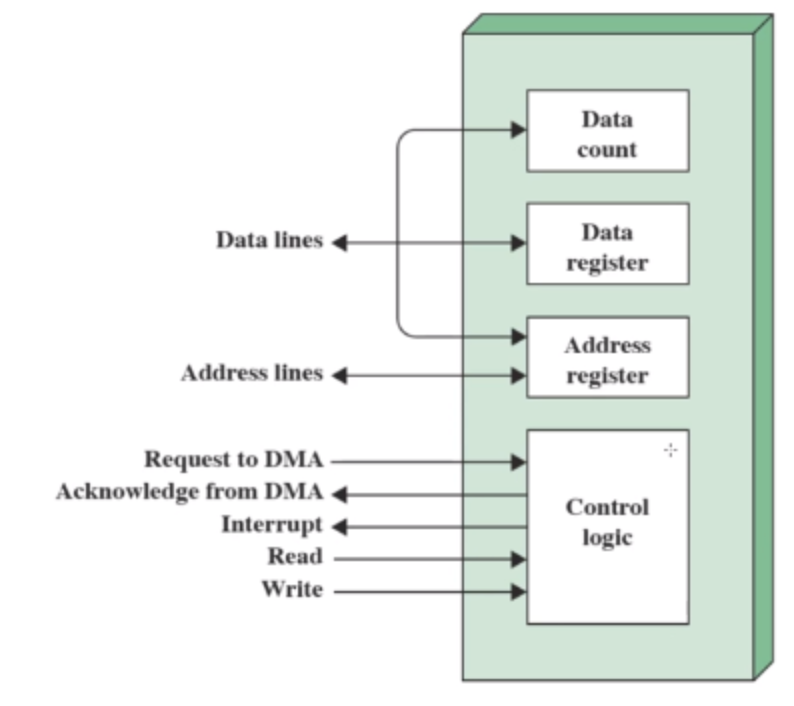

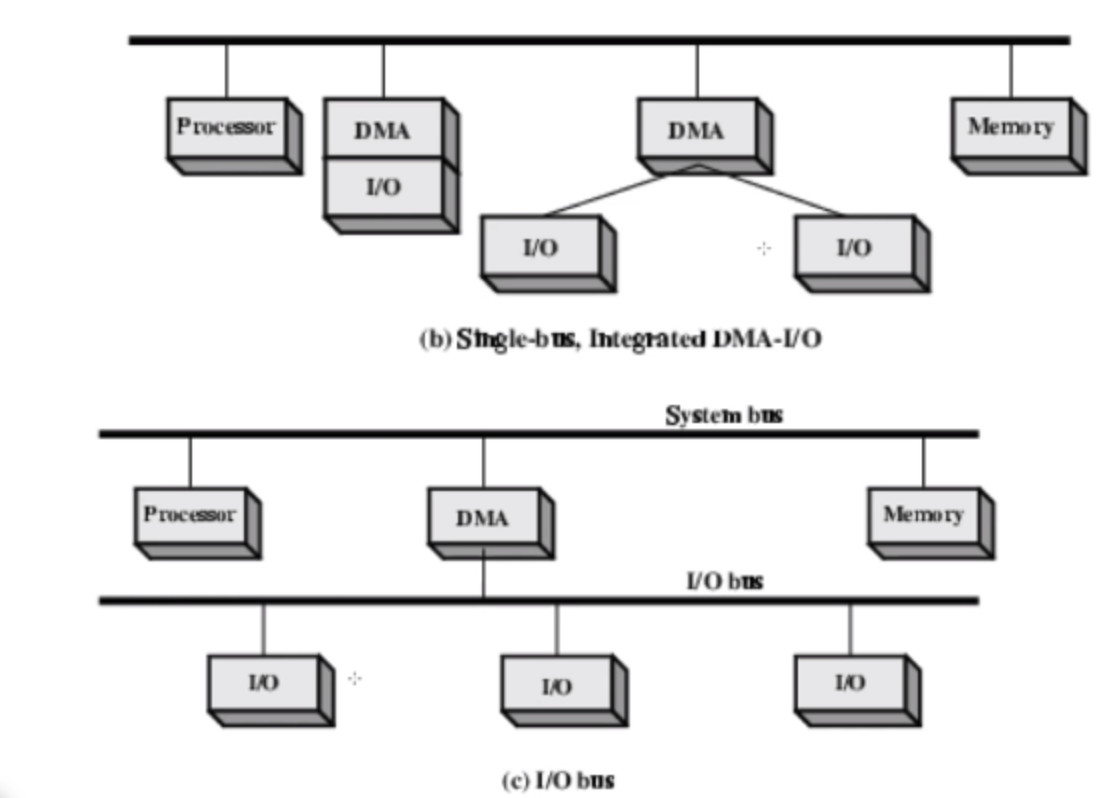

- dma

- i/o가 직접 메모리에 쓰는 방식

- 원래 메모리 접근은 cpu가 주관

- 특징

- cpu에 외부에 있음

- cpu 개입 없이 메모리나 데이터 블럭을 옮겨줌

- 데이터 크기가 큰 경우에 효과적임(데이터 크기 작은 경우는 효율적x)

- dma module과 controller 필요

- cpu가 dma controller에게 다음과 같은 정보 줌 --> dma가 cpu의 역할을 하기 때문에

- read/write

- device address

- Starting address of memory block for data

- Amount of data to be transferred

- dma 내부 구조

- data count: 얼마나 많은 데이터 전송

- data register: 실제 전송되는 데이터 저장되는 장소

- adrress register: 메모리의 어떤 주소 영역인지

- control logic

- dma 외부구조

- dma 작동 방식

- disk controller(입출력 장치) 요청 보냄