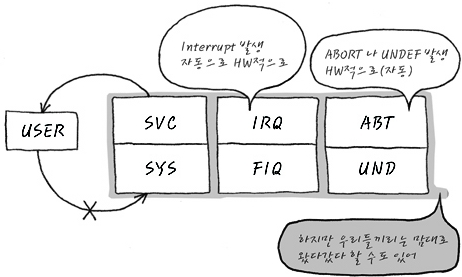

ARM Mode에서 Privileged Mode는 자기 마음대로 mode를 바꿀 수 있지만,

그 이외에 Hardware적으로 자동으로 특정 Mode에 진입할 수 있습니다.

그럼 Mode 진입 유발자가 Exception 입니다.

(Exception는 Interrupt를 포함한 더 큰 사건을 의미)

이런 Exception이 일어났을 때 jump하는 Address들을 모아 Exception Vector Table 이라고 합니다.

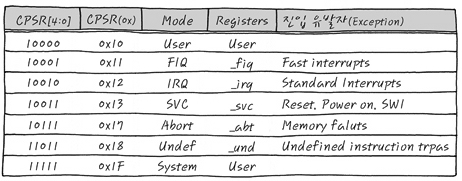

각각의 exception은 아래와 같이 발생 조건을 가지고 있습니다.

1.SVC Mode : SVC mode는 Power on이나 reset이 일어난 경우에 SVC mode 진입합니다.

2.IRQ Mode : Hardware적인 Interruput가 발생하여 ARM Core에 알려주면, IRQ Mode로 진입합니다.

3.FIQ Mode : Interrupt 중 Fast Interrupt가 발생하면 진입합니다.

4.ABT Mode : Abort moe는 Access 하려는 주소가 Access 할 수 없는 주소이거나, Instruction fetch를 해오려는데 못해 온 경우에 진입합니다.

(MMU나, MPU를 사용하는 예에서는 Access Protection이 걸려 있는 주소를 함부로 Access하려고 했을 때 ABT exception이 발생합니다.

5.UND Mode : Undefined Mode는 Instruction을 decode했는데 ARM이 모르는 것일 경우에 진입하게 되며, Memory Corruption이 났을 때 발생합니다. ARM이 사용하지 않는 코드를 일부로 삽입하게 되어, UND vector 주소로 jump하게 만들어 디버깅 Code등의 의도된 일을 행하게 할 수 있습니다.

Exception에도 우선순위가 존재합니다.

(Exception 우선순위)

1. reset

2. Abort

3 ~ 4. FIQ ~ IRQ

5. Prefetch Abort

6. Undefined instruction

7. SWI

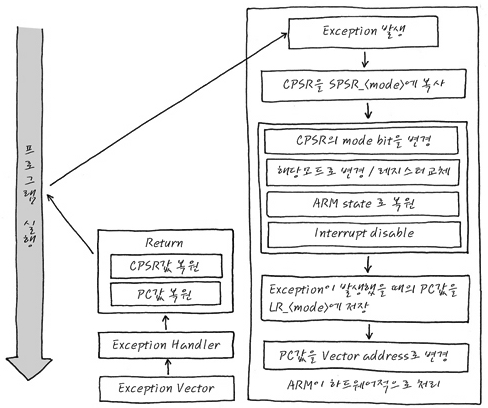

(Exception 발생 후 과정)

1. Exception가 발생 한 후, 이전 mode로 돌아갈 수 있어야 한다.

2. 지금 쓰던 Register 값들을 다시 사용할 수 있어야 한다.

다시 말해, 이전에 쓰던 Context를 다시 복원할 수 있어야 한다.

3. 이전 mode로 돌아갔을 때 원래 수행 하던 곳으로 돌아 갈 수 있어야 한다.

4. 그리고 자동으로 해당 Exception Vector로 점프

위에 네가지를 만족하기 위하여

- CPSR을 저장할 수 있어야 한다. CPSR에는 현재 Mode가 어떤 Mode였는지에 대한 정보를 가지고 있다.

- Context를 Stack에 저장. Banked Register를 제외한 나머지 Register를 R0 ~ R12에 저장해야 한다.

- 원래 수행하던 곳으로 돌아가려면, 해당 주소를 저장해야한다.

- Exception Vector로 점프

(IRQ Exception 발생 시 예시)

1. CPSR을 SPSR_irq에 복사

2. CPSR의 mode를 IRQ로 변경, 결과적으로 stack pointer도 IRQ mode의 stack pointer로 변경

3. IRQ disable 함, ARM mode로 변경

4. R14_irq := 현재 PC

5. IRQ Exception Vector 주소가 0x18이므로, PC = 0x18로 변경

(여기까지는 Hardware 적으로 다 알아서 처리)

6, R0 ~ R12를 R13_irq (stack pointer)가 가리키는 stack에 저장

7. 돌아갈 주소 보정 필요 -> R14_irq(LR) = PC를 위에 넣었죠?

interrupt가 걸린 순간에는 pipe line에 의해서 2개 opcode가 이미 진행되었으므로, LR = LR - 4 로 보정 (sub lr,lr,#4)

출처 : 임베디드 레시피