MCU가 자기보다 느린 메모리 장치를 다룰 때 Wait State라는 방법을 사용한다.

예를들어, Clock에 따라서 MCU가 특정 주소를 Access하여 값을 읽기 위해 Address Bus 신호를 흘려준 후, RD/를 Low로 구동시킨 후에, Data linㅇ의 값을 읽는다.

이때, Timing만 보면, RD/를 구동시킨 후에 일정 시간이 지나야 제대로 된 DATA 값을 돌려준다고 가정하고 그 시간이 지난 후에야 Data를 읽어 들이기 시작합니다.

제대로 된 값을 돌려주기로 기대되는 시간이 Wait State라고 불리는 구간이며, 보통 Clock에 대비하여 몇 Clock후에 제대로 된 DATA가 나온다~ 하는 Device Specification이 있습니다.

Wait State 때문에 빠른 CPU가 느린 외부장치와 통신할 때 쉬는 시간이 늘어 나는 경향이 있습니다

어쨋든 간에 이런 Wait State를 제대로 설정해 주지 못하면 엉뚱한 순간에 Data값이라고 생각하고 Dataㄹㄹ 가져오기 때문에 문제 발생 소지가 있습니다.

보통 처음 Power up이 되자 마자, 보통 최대 개수의 Wait state 상태를 기다리고요. Device Configuration을 시작하면 이 Wait state를 Setting하곤 하죠. 이 Wait State는 Register를 이용해서 설정 할 수 있는데, 최소 Wait State를 잘 맞추어서 설정을 해줘어야 Memory가 최대 Performence를 낼 수 있습니다.

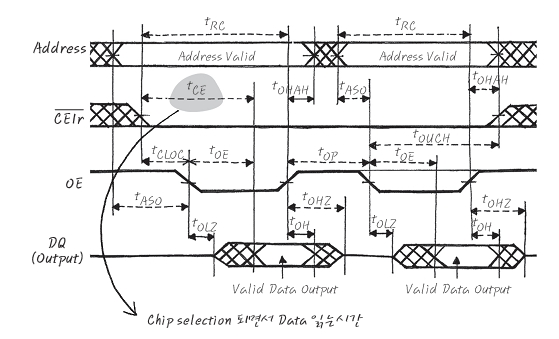

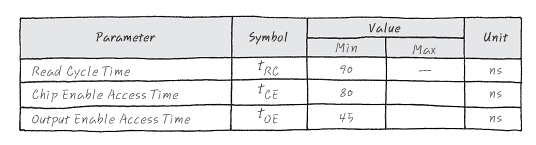

아래 그림은 NOR Memory의 Device Spec의 일부입니다.

우리가 관심을 가져야 할 부분은 tCE입니다.

tCE는 Min 80ns라고 되어 있죠. 80ns 후에는 Data가 확실하게 나온다는 이야기입니다.

사용할 MCU의 Device Spc은 아래와 같습니다.

그림 중에 보면 CS_N이 내려가고 나서 Data를 채 갈 수 있는 시간 까지가 tACSDV라고 표시되어 있지요. 요게 우리가 관심 가져야 하는 Timing이겠네요. Spec을 더 자세히 보면,

tACSDV는 (T-21) + WT 라고 되어 있죠. 그런 거에요. 우리는 최소한 80nS를 기다려야 하고 그건 (T-21)+WT가 최소한 80nS가 되어야 한다는 말인 게죠. T는 CPU Clock 주파수의 주기이고요, 여기에서 만일 우리의 System이 50MHz짜리 System이다.. 치면 T = 1/40MHz = 0.2510^-7 = 2510^-9 = 25nS 이고요.

여기에 근거해서

(T-21) + WT > 80nS 인 것을 만족해야 해요.

그러니까

(25-21) + W25 > 80

W25 > 80-4

W*25 > 76

인 셈이죠. 여기에서 Wait State라는 건 정수여야 하는 거고요. 그러니까 W가 3인 경우에도 fail, W가 4인 경우에는 pass가 되겠네요. 아슬아슬하게도. 참내. 이런 경우에 Wait State (W) = 4이라는 얘기는 4개의 Main clock을 기다려야 한다는 말이랑 똑같아요.

이런 억울한 경우라면 차라리 Wait State가 75nS짜리를 사용하게 되면,

(T-21) + WT > 75nS 인 것을 만족하면 되니까.

(25-21) + W25 > 75

W25 >7 5-4

W*25 > 71 → W= 3

이러면 5nS 차이인데, Wait State는 1 MCU Clock이 줄어 들었어요. 훨씬 성능이 좋아지겠죠. 25nS씩 더 잡아 먹던걸 덜 잡아먹게 했으니까요. 여기서는 한가지 예만 들었는데, Table보면 다른 것도 많이 있죠. 이런 거 다 따져 보고서 Wait State를 결정해 줘야 해요. Control하는 방법은 MCU의 Memory Controller 쪽 Register나, Bus Sizer Register들을 찾아보면 이런 값을 설정해 줘야 하는 부분이 있으니까 잊지 말고 꼭 해주세요!