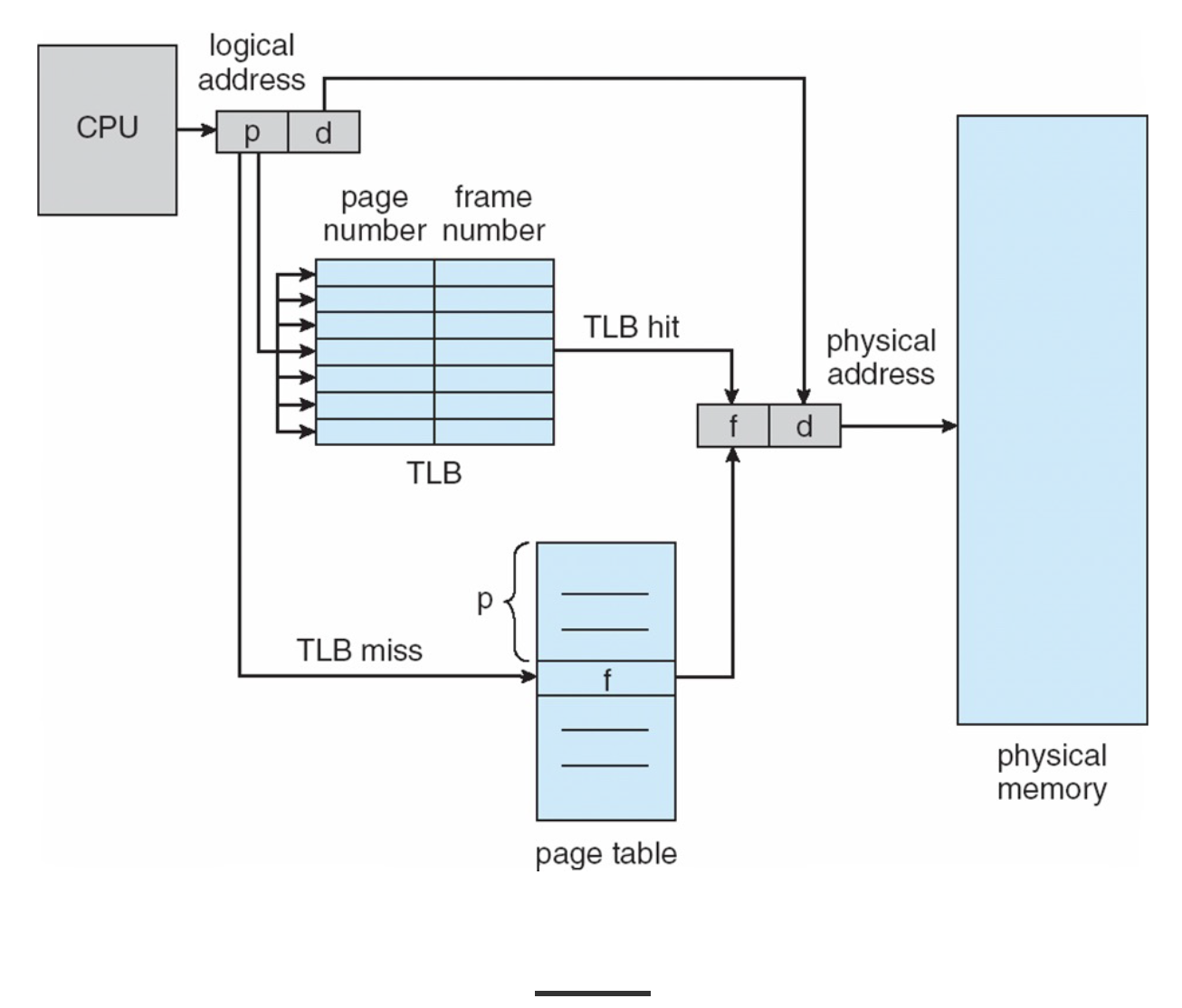

페이지 테이블은 메인 메모리에 존재해서 CPU는 메인 메모리에 최소 2번은 접근해야 원하는 데이터를 얻을 수 있음

1. 페이지 테이블에 접근

2. 페이지 테이블을 기반으로 실제 메모리로 접근

이 접근을 줄이고자 TLB 사용

🍳 Translation Lookaside Buffer

TLB(Translation Lookaside Buffer, 페이지 정보 캐쉬)

-

가상 메모리 주소를 물리적 주소로 변환하는 속도를 높이기 위해 사용하는 캐시

-

최근에 일어난 가상 메모리와 물리 주소의 변환 테이블 저장

-

CPU가 가상 주소로 메모리에 접근하려고 할 때 우선 TLB에 접근하여 가상 주소에 해당되는 물리주소를 찾고 TBL에 매핑이 존재하지 않으면 MMU가 페이지 테이블에서 해당되는 물리 주소로 변환한 후 메모리에 접근

-

MMU에 포함되어있는 작은 캐시

-

굉장히 작음: 64~1024 entry

- TLB에 있는 캐시면 메모리에 접근하기 전에 막아야 하기 때문에 크기를 줄여 속도 높음

-

이점: 물리주소를 갖고 있으면 메모리에 두번 들릴 필요없이 바로 해당 물리주소를 찾아갈 수 있음

-

CPU 레지스터로 구현하면 너무 비쌈

-

메모리 내에 두면 너무 느려짐

-

그래서 별도의 칩으로 만듬

동작 원리

1. CPU에서의 정보로 TLB 탐색

2. TLB에 있으면 바로 물리 주소에 접근

3. TLB에 없으면 page table로 들어감

문제: 컨텍스트 스위칭

🍳 TLB를 쓰는 이유

CPU의 MMU 안에서 해결돼서 속도가 빠름

🍳 MMU

MMU:

- CPU 코어 안에 탑재

- 가상주소를 물리주소로 변환 & 메모리 보호

- MMU 사용하면:

- CPU가 각 메모리에 접근하기 전에 메모리 주소 번역 작업 수행

- 메모리를 일일이 가상 주소에서 물리적 주소로 번역하면 작업 부하

- MMU는 RAM을 여러 페이지로 나눠 각 페이지를 하나의 독립된 항목으로 처리

이점:

- 모든 프로세스마다 같은 주소 사용 가능

- CPU는 프로세스 관리 쉬워짐

- 서로 떨어진 데이터를 연속적으로 표현 가능

🍳 TLB와 MMU의 위치

CPU에 탑재

참고: