운영체제- Computer System2

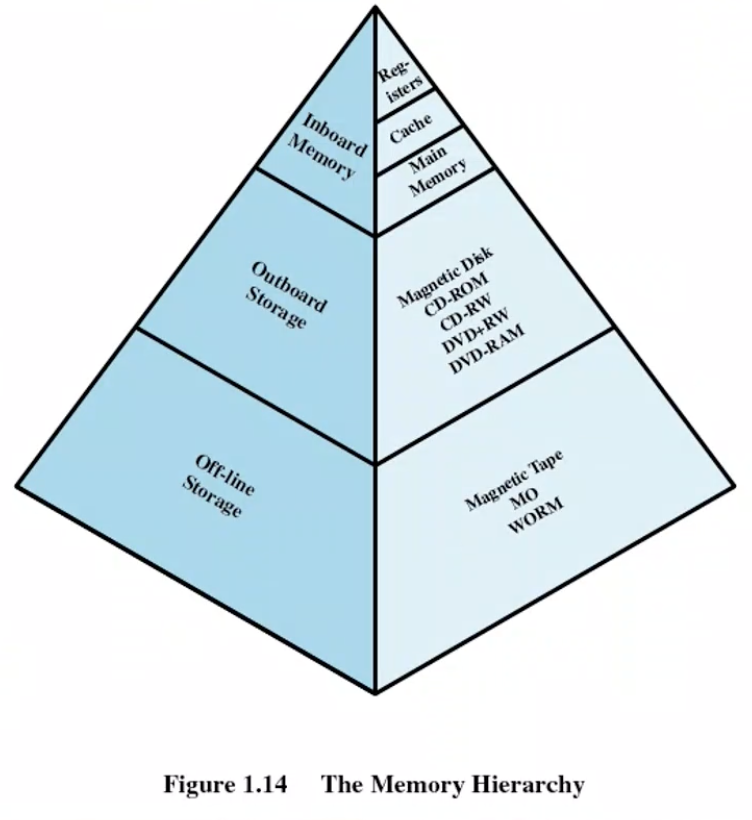

Memory Hierarchy

- 컴퓨터 시스템의 가장 빠른 저장 장치를 피라미드 구조로 나타냄

- Inboard Memory

- 메인 보드에 내장 - Outboard Storage

- 컴퓨터를 키면 같이 켜짐 online storage- 메인 보드 밖에 있어서 outboard

- Off-line Storage

- 백업 장치- 필요할 때만 킴

올라갈수록 빠르지만 용량은 줄어들고 접근하는 횟수가 늘고 비싸진다

Locality of reference (참조지역성)

- CPU가 일을 할때 모든 데이터와 명령어를 균일하게 접근하지 않는다

- 특정 데이터와 명령어가 더 자주 접근한다 ex) loop안 데이터는 loop밖보다 더 많이 접근된다

- 따라서 접근 빈도가 높은건 피라미드 꼭대기 빠른 메모리에 저장

- 접근 빈도가 낮은건 피라미드 밑쪽 느린 메모리에 저장

Cache

- Cache 왜 필요한가?

-

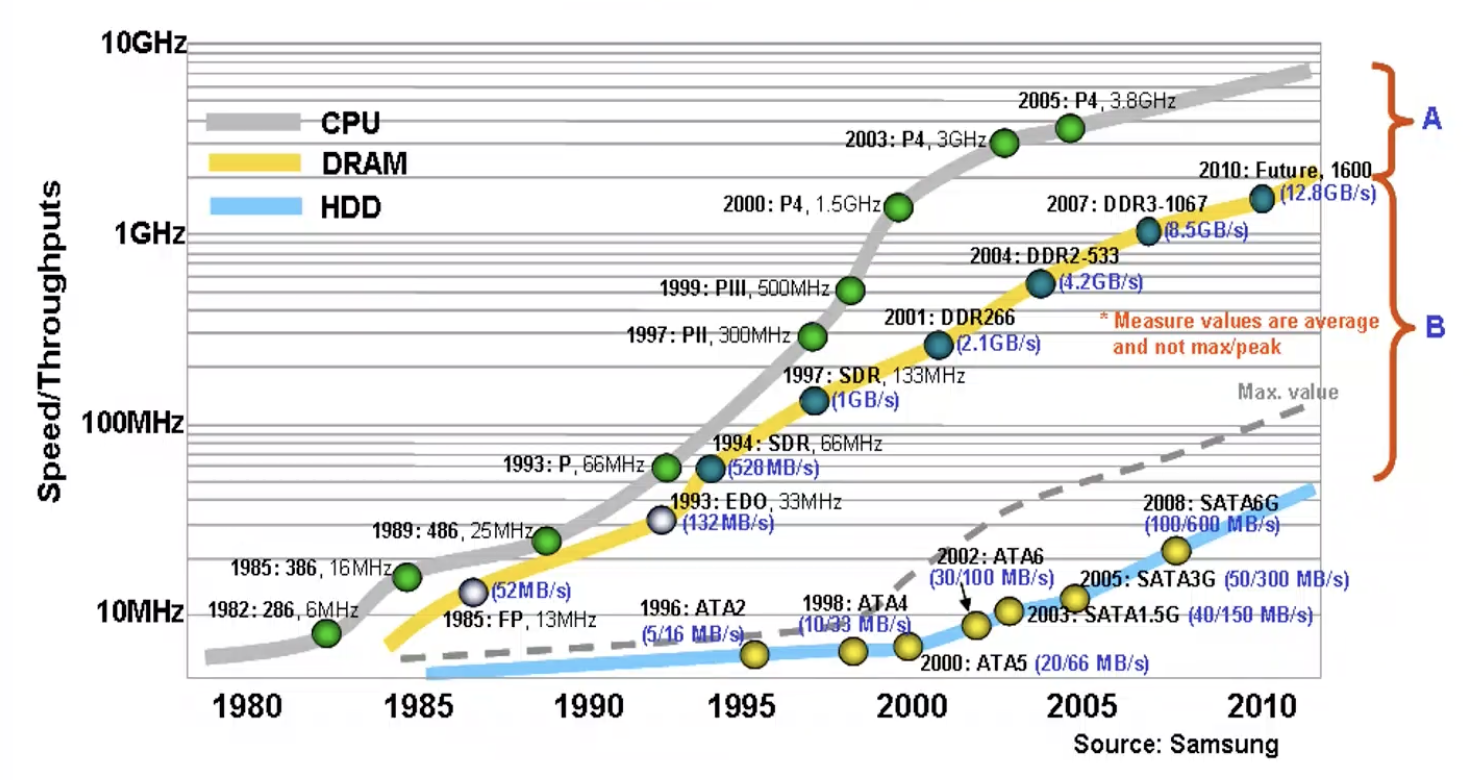

연도별 cpu, 메모리, 하드 속도 발전 동향 그래프

-

y축은 log scale

- A가 B보다 훨씬 크다 -

하드 IO 발생할때

- cpu 입장에서 하드가 병목 -

하드 IO 발생시 안할때

- cpu 입장에서 메모리가 병목cpu와 메모리 속도차를 개선하자! Cache

-

Memory cycle time (메모리 속도) 때문에 CPU가 수행하는 명령의 속도가 제한되는 것을 해결해야한다

- CPU와 main memory 사이에 빠른 메모리 Cache를 둔다

- Cache는 주로 dram보다 빠른 sram 사용

- sram이 더 비싸지만 빠르다 (피라미드 상위) - Main memory에서 자주 접근되는 일부 데이터를 cache에 두면 CPU는 cache에서 가져오게된다 -> 메모리 접근 속도 향상

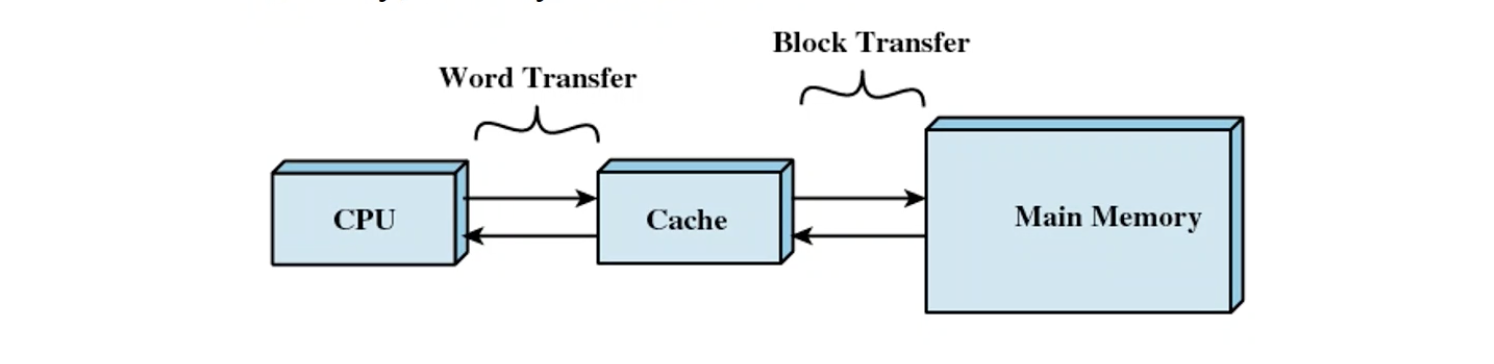

- CPU는 memory에서 데이터 혹은 명령어를 가져올 때 1 word씩 가져온다

- Cache와 main memory 사이에서는 1 block씩 가져온다

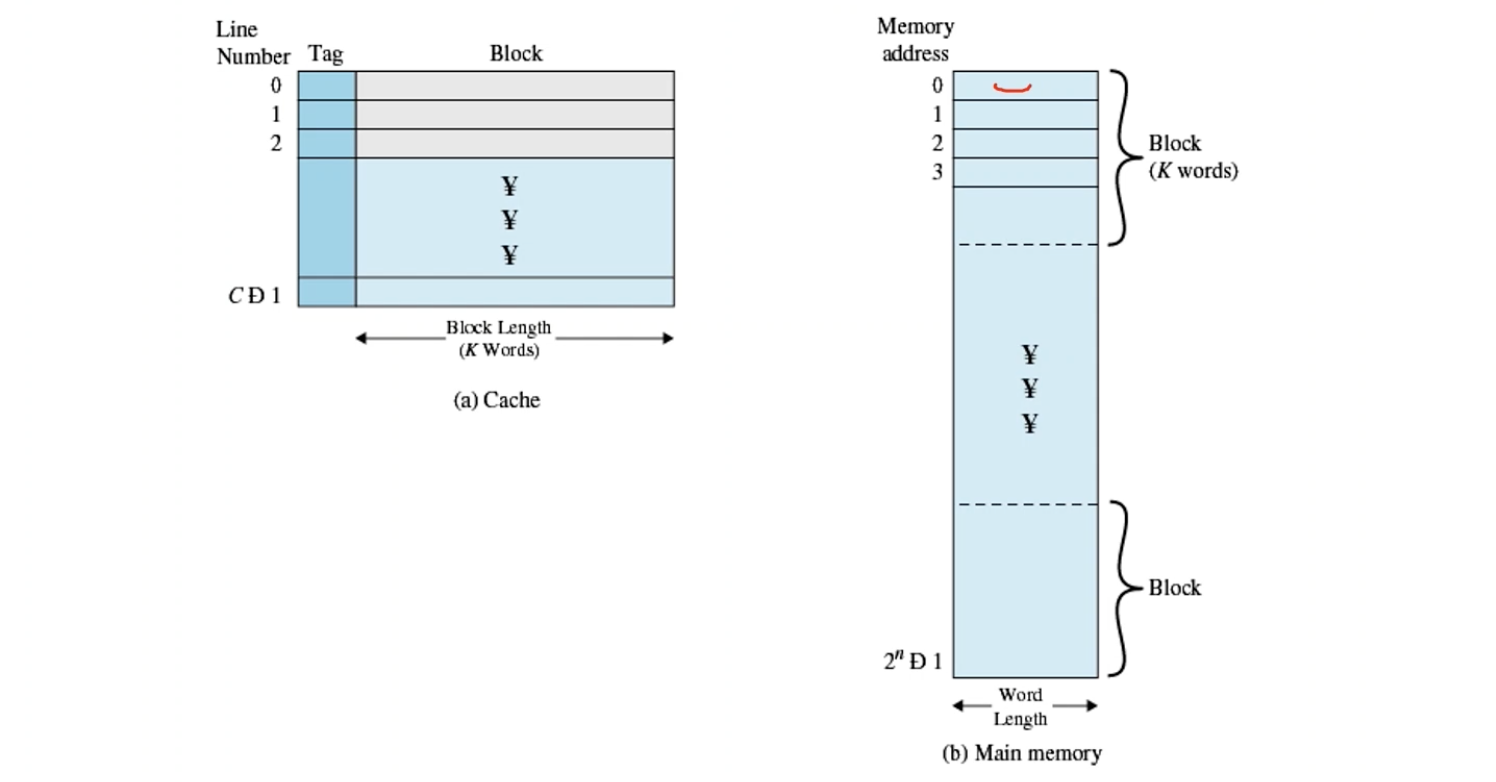

Memory System

- 여러개의 word 사이즈 == block 사이즈 == slot 사이즈

- 메인 메모리에서 여러개의 word를 block으로 묶어 cache slot 한줄에 저장한다

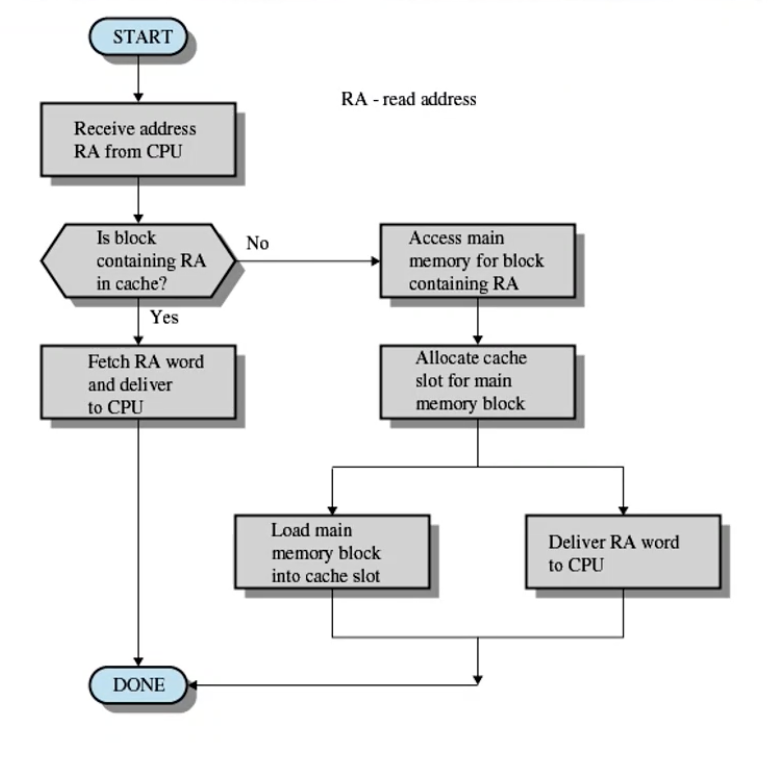

Cache Memory

- Cache 없이는 main memory에서 직접 데이터와 명령어를 가져온다

- Cache가 있다면 먼저 RA (read address)가 cache에 있는 주소인지 확인한다

- 있다면 cache에서 읽기

- 없다면 main memory 접근

- RA가 포함된 block을 통채로 cache로 가져온다- Cache에 가져온것 중에서 RA에 해당하는 word만 cpu로 가져온다

- Cache 사용시 효과가 나타나려면 cache에서 자주 읽어야한다

- 빈도가 적으면 cache에 있는지 확인하고 main memory에서 가져와야해서 overhead가 커질 수 있다- 따라서 자주 접근되는 데이터 혹은 명령어를 cache에 저장!

Cache hit ratio가 정말 높은 이유는 지역참조성

Cache Design

- Cache hit 비율이 낮으면 성능이 떨어져 관리 필요!

- Cache size

- 테스트를 통해 자주 접근되는 데이터와 명령어의 size가 그렇게 크지 않다고 판단- Cache size 작아도 효과는 크다

- 오히려 너무 크면 자주 접근되지 않는 데이터도 캐시에 올라가 비용 대비 효과가 떨어진다

- Block size

- Main memory와 cache 사이에서는 block 단위로 주고 받는다

- 한꺼번에 많은 word를 옮기는 이유는 주변 데이터 혹은 명령어에 접근할 가능성이 크기 때문이다- Main memory 접근 횟수를 줄일 수 있다

- Block size를 과도하게 키우면 실제로 자주 접근되지 않는 데이터 혹은 명령어가 Cache에 저장될 수 있다

- Mapping function

- set associative function

- CPU가 접근하고 하는 데이터가 cache에 있는지 빠르게 판별해야한다- Main memory에서 cache의 어느 위치에 저장할지 mapping functiond이 결정한다

- slot에 tag를 붙여 한번에 검색할 수 있다

- Replacement Algorithm

- Cache가 작기 때문에 꽉차면 어느 slot을 버릴지 결정해야 한다

- Least Recently Used Algorithm (LRU)으로 최근에 덜 사용된 slot을 삭제한다- LRU는 메모리에서도 사용된다

- Write policy

- write through: 바로 main에 반영 (느림)- write back: main memory가 가짜 값가지고 있을 수 있다

- cache에만 Write 반영? main memory도 같이 반영?

- CPU가 main memory에 STORE 명령을 실행하려는데 데이터가 cache에 있다면 cache에만 STORE한다 - 즉 cache 값과 main memory 값이 불일치하는 경우가 생긴다 부작용 INCONSISTENCY

- Replacement에 의해 cache에서 제거될 때 Main memory 업데이트

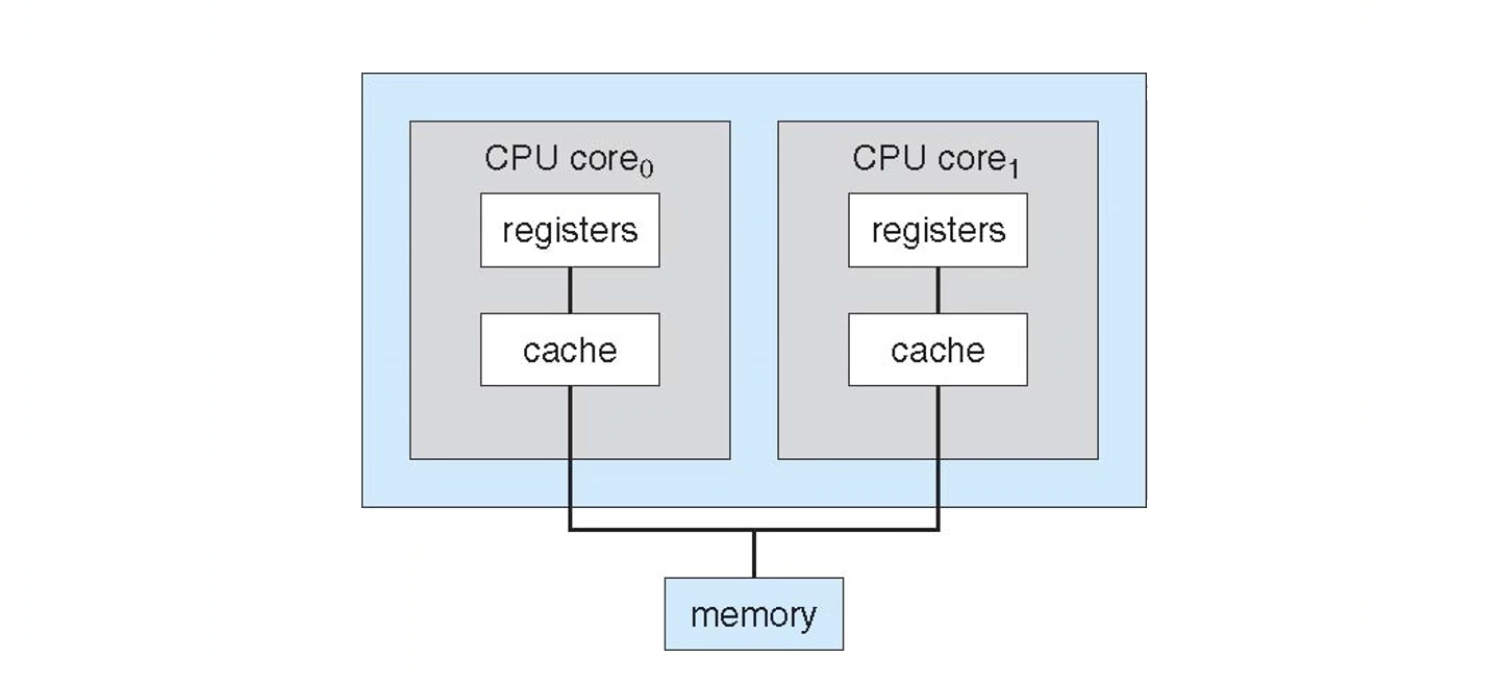

- Cache Coherence Problem- write through, back 둘다에서 발생

- L1 코어 안 캐시, L2 코어 밖 cpu 안 , L3 cpu 밖

- 코어가 여러개인 경우 코어마다 cache가 있을 수 있어 코어간의 데이터 값이 서로 다를 수 있다

- cache invalidation message 보내서 다른 코어에게 알려주기

- write through, back 둘다에서 발생

- Cache Coherence Protocol로 캐시 문제 해결

- write back: main memory가 가짜 값가지고 있을 수 있다

- Sequential flooding

- 쓸모없는 값이 캐시에 저장 ex) array- non temproal instructions: 캐시에 저장하지마

Disk Cache

- Main memory와 disk 사이에 cache

- sram이 아닌 dram

- Main memory 특정 영역에 디스크 데이터를 올린다

- disk 접근시 disk cache에 있으면 cache에서 처리한다

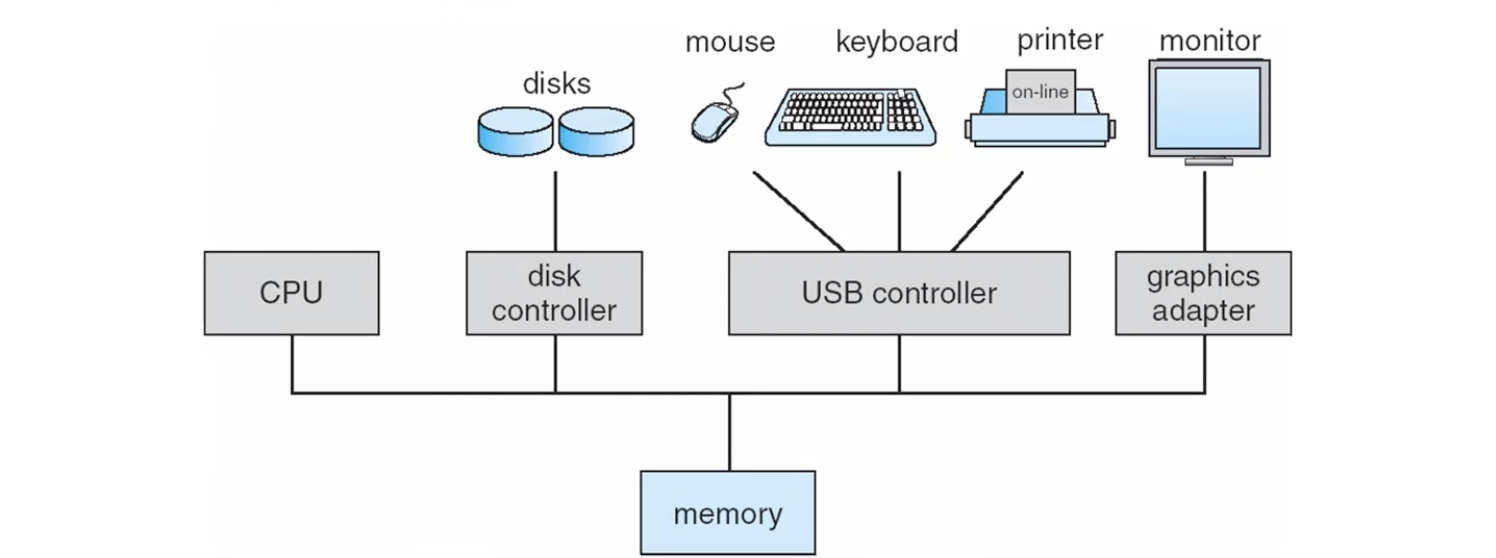

Computer System Organization

- 어떤 I/O 장치들이 있는가?

- 모든 장치들은 Bus로 연결된다

- IO는 CPU와 장치들 사이에 직접 일어나지않고 Memory를 매계로 일어난다

- 예) CPU -> Memory -> Disk, Disk -> Memory -> CPU

- 모두 독립적으로 일을 하기 때문에 memory contention 경쟁이 일어난다

- controller 혹은 adapter가 IO 장치들을 제어한다

- 즉 controller가 메모리에 접근한다

Computer System Operation

- I/O는 memory와 buffer 사이의 입출력이다

- device controller에는 local buffer가 있다

- Output

- Main memory에 있는 데이터를 먼저 buffer에 올려놓고 실제 flash memory에 저장한다 - Input

- flash memory가 buffer에 있는 데이터를 올려놓고 main memory가 가져오는 것이다

- 즉 I/O 장치는 직접 main memory에 입출력하지 않는다

- I/O가 끝나면 interrupt를 걸고 CPU interrupt handler가 buffer로부터 읽어드린다- 실제로 가져오는건 interrupt handler

왜 굳이 buffer와 interrupt handler를 거치는가? I/O 장치를 믿을 수 없다 OS의 신뢰영역에 침범할 수 있다. 따라서 OS 코드만 main memory에 접근 가능하다

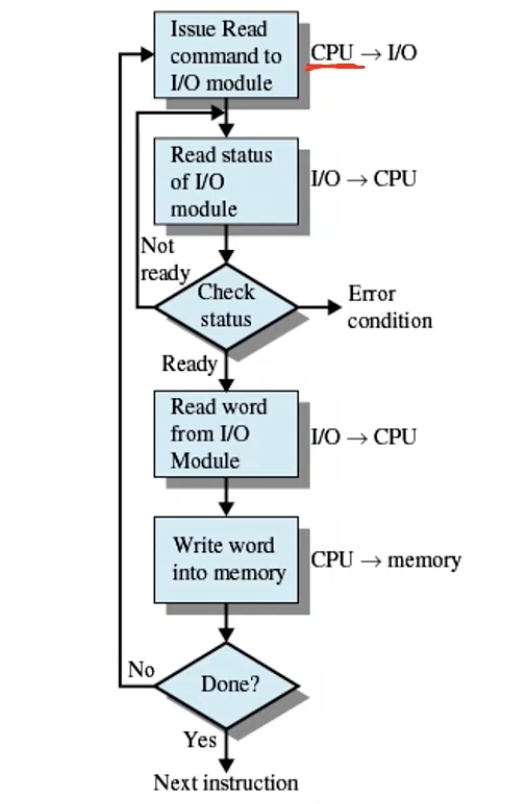

Programmed I/O

-

CPU -> I/O : 명령 issue

-

I/O -> CPU: 상태값 (busy bit) 전달

-

CPU : 바쁘다고 하면 루프 돌기 / 안바쁘면 진행 -> CPU를 쓰면서 무의미한 ...interrupt?

-

I/O -> CPU: 1 word 읽어감

-

CPU -> memory: 읽어온 1 word 쓰기

-

n번째 word를 읽기 위해 다시 처음으로

-

CPU가 관여해서 busy wait 발생

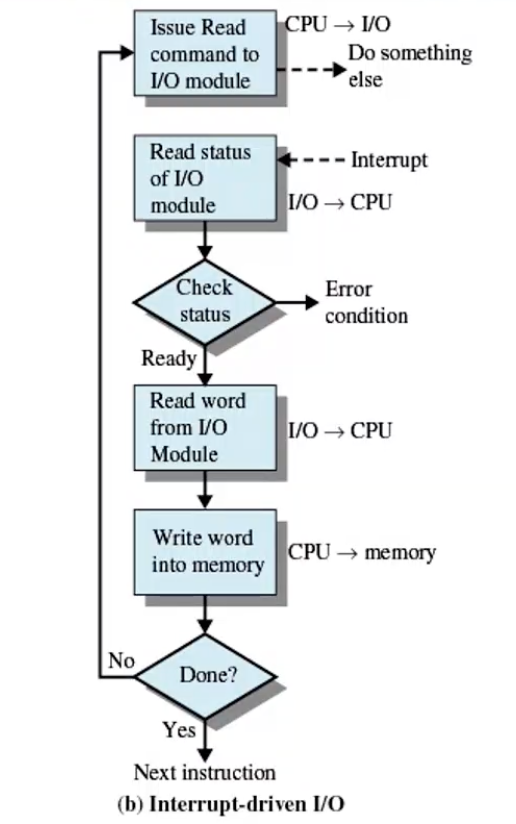

Interrupt-Driven I/O

- 달라진건 더이상 루프를 안돈다는 것

- Interrupt를 사용하여 I/O가 안바쁘다고 알려준다

- Busy wait 제거

- CPU 사용 효율이 높아진다

1 word 읽을 때마다 계속 도는 것은 너무 비효율적이다 -> I/O 장치가 main memory에 직접 접근 못해 CPU가 관여해야 하기때문에 어쩔수 없다..

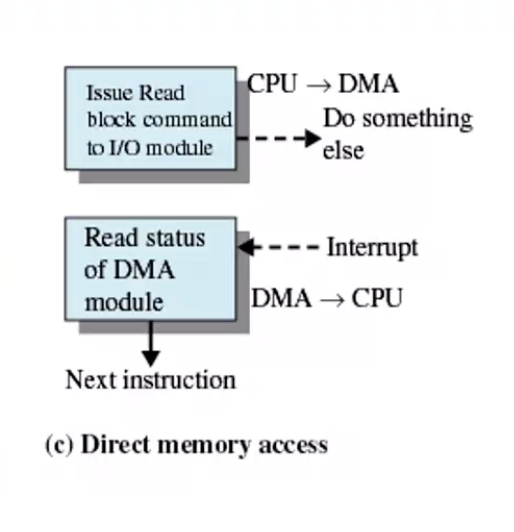

Direct Memory Access

- CPU가 아닌 것에 main memory에 직접 접근 권한 부여

- DMA controller

- board에 내장한 검증된 장치- DMA가 루프를 돌고 CPU는 다른 유의미한 일을 한다

- cpu가 1 word 단위로 가져오는 작업을 대신 수행

- 1 word 단위를 늘릴 수 있다!

- CPU -> DMA: 명령 issue

Interrupt와 DMA로 CPU 성능 향상

A Dual-Core Design

- 여러개의 core를 하나의 cpu로 본다

Computer Startup

-

bootstrap program

- 부팅시 실행- 모든 하드웨어 체크, 초기화

- read only memory ROM에 있음-> board에 내장

- OS를 메모리에 로드

교수님 부가 설명

Operating System

- service 제공 = system call

- 동기, 비동기

- 동기: interrupt

- 비동기: exception

- trap: system call 의도적

- fault: recoverable 에러

- abort: unrecoverable stop program

Dual mode

- assembly coding 이유 -> 중요 코드를 assembly로 최적화

- system call 대신에 assembly code로 운영체제 접근 문제 발생!!

- dual mode operation - 사용자가 박은 건 거절, system call은 수락하여 구분 -> status bit 0,1 (user/kernal mode)

- mode bit

Process

- 모든걸 가지고 있는 자료구조

- program: passive process: active

- 구조체로 구현

- binary는..? -> 메모리에 직접올리고 !주소!만 구조체에 저장

- process data structure - process를 manage

System Call

- os dependency 이식성

- primitive은 공통으로 만들자

- 직접 system call부르지 말고 API로

- open -> system call

- fopen -> c api

- libc -> standard library

Virtual Machine

- 기계 위 기계

- 시스템 프로그래밍

- virtual machine을 cloud computer에 배정하여 더 많은 환경 제공

- 서비스 중단 시간을 없애기 위해 virtual machine migration

Java Virtual Machine

- default

- web browser

- 하나의 컨텐츠마다 cpu/os 다 달라

- c -> compile -> machine instruction -> cpu dependency

- java virtual machine이 인지하는 명령어 집합이 있음

- byte code- java interpreter가 기기에 맞게 compile

- 느려서 jit으로 최적화

- java interpreter가 기기에 맞게 compile