1. type of performance

1.1 time

1.1.1 wall-clock time, response time or elapsed time

- 동작의 처음부터 끝까지의 실제 시간

- 모든 시간을 포함한다. 즉, 다른 program이 사용하는 CPU time, I/O, OS overhead 등의 시간 모두 합한 시간

- 이를 사용할 수 없는 이유는 불확실성(unpredictability)이 너무 크기 때문. 즉, 다른 process들이 CPU를 차지하기도 하는 이러한 상황이 불확실성을 야기함.

1.1.2 CPU(execution) time

- 주어진 하나의 program이 사용한 CPU time

- user CPU time + system CPU time(OS가 program을 위해 사용한 시간)

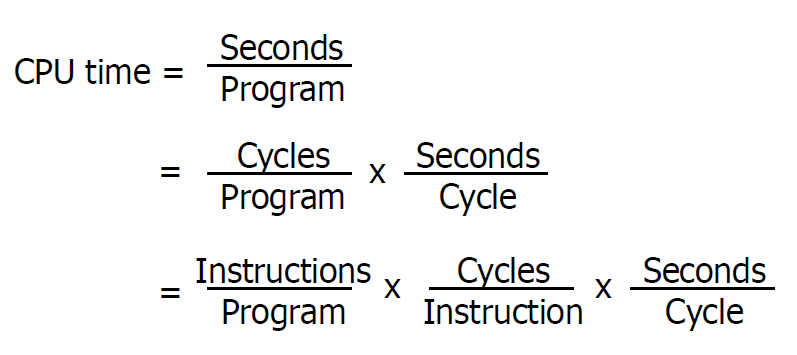

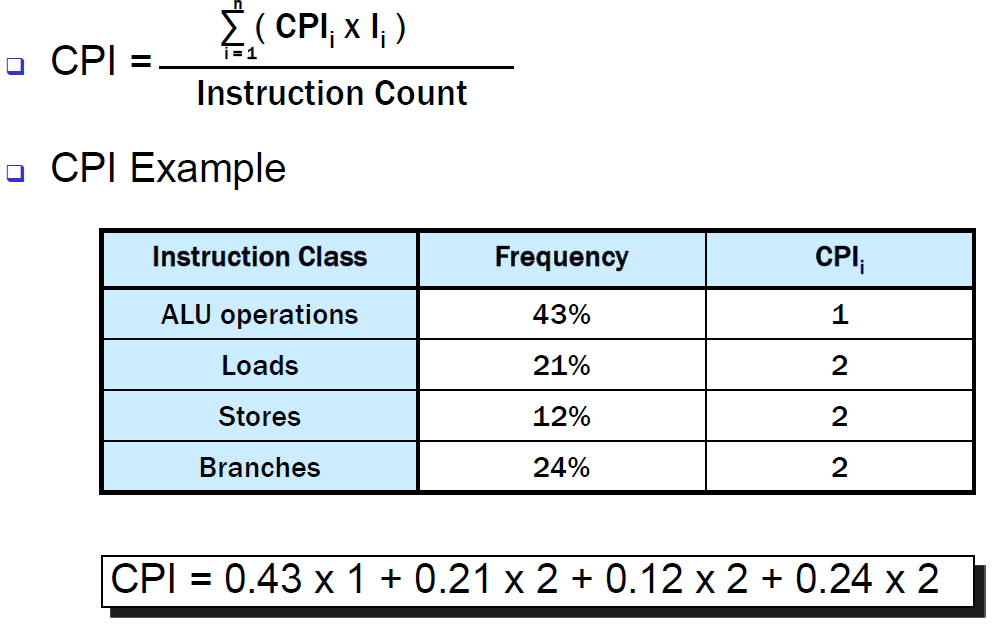

1.1.3 Decompostion of CPU(execution) time

cycles : 어떤 instruction에 걸리는 cycle의 수

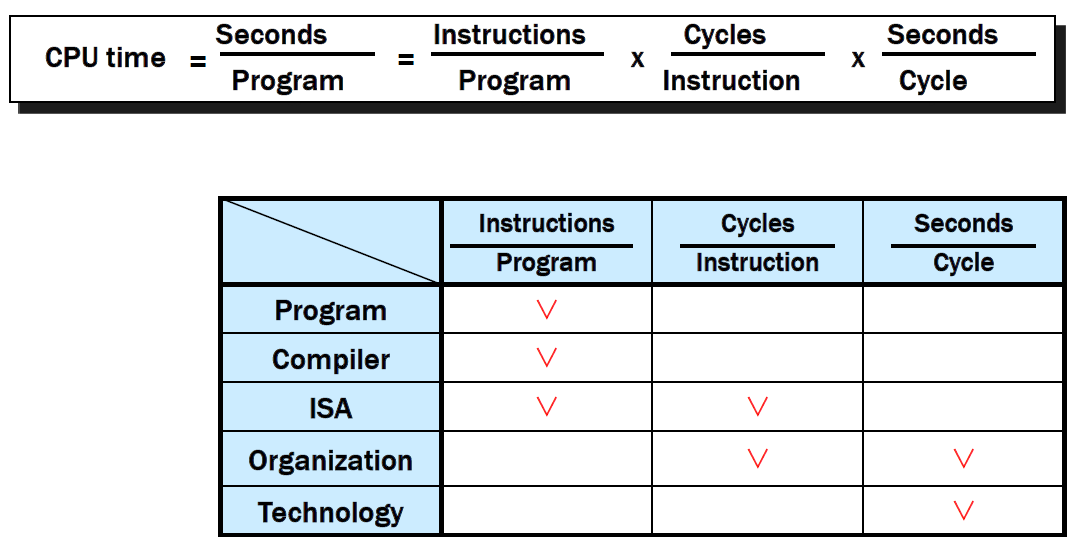

1.1.4 factors involved in the CPU time

- compiler & instructions/program : 같은 프로그램이더라도 compiler의 최적화에 의해 실행되는 instruction 수를 줄일 수 있음

- ISA & instructions/program : RISC일 경우는 더 많은 instruction을, CISC일 경우는 더 적은 instruction

- ISA & cycles/instruction : 2)와 같은 이유로 반대

- organization & cycles/instruction : pipelining을 할수록 한 개의 instruction을 실행하는 데 필요한 cycle 수가 줄어든다.

참고) ISA(Instruction Set Architecture)의 두 종류

- RISC(reduced instruction set computer) : instruction 하나하나가 간단하고, 효율적으로 pipelining을 함

- CISC(complex instruction set computer) : instruction 하나하나가 복잡해서 많은 일을 함

1.2 Rate

1.2.1 MIPS(million instructions per second)

- 이해하기 쉬움. 즉, 빠른 머신은 MIPS 값이 크다.

- 반면 다음과 같은 문제점이 있음

- 단위시간 당 몇 개의 수행하는 instruction 수를 셀 뿐, 각 instruction이 얼만큼의 일을 하는지는 고려하지 않는다.

- 같은 컴퓨터에서도 프로그램에 따라 다른 값을 갖는다.

- 경우에 따라서는 performance에 반비례할 가능성이 있다. 예를 들어, 같은 프로그램을 실행하는 데 한 컴퓨터는 4cycle이 걸리는 instruction 2개, 다른 하나는 1cycle이 걸리는 instruction 10개가 필요하다고 하자. 그러면 MIPS 값은 후자가 더 크지만 성능은 전자가 더 좋다.

2. Amdahl's Law

2.1 개념

주어진 improvement에 의한 성능 향상은 개선된 특징의 비중에 의해 제한된다.

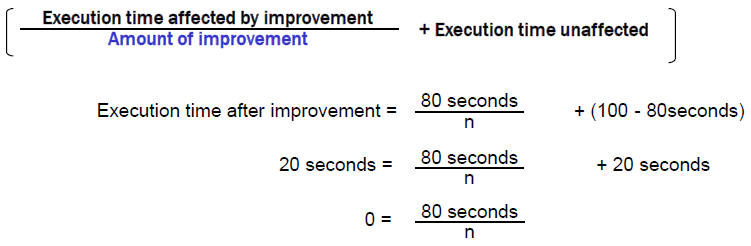

2.2 수식