컴퓨터와 디지털 논리회로 (2)

학습목차

- 컴퓨터와 디지털 논리회로(2)

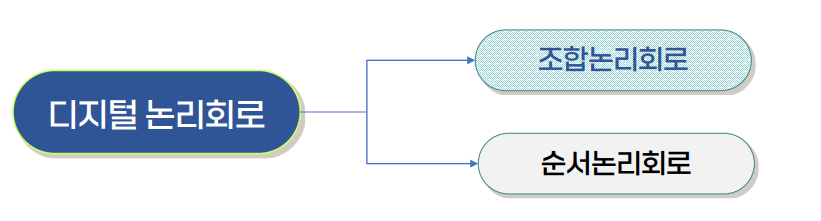

- 조합논리회로

- 순서논리회로

1. 조합논리회로

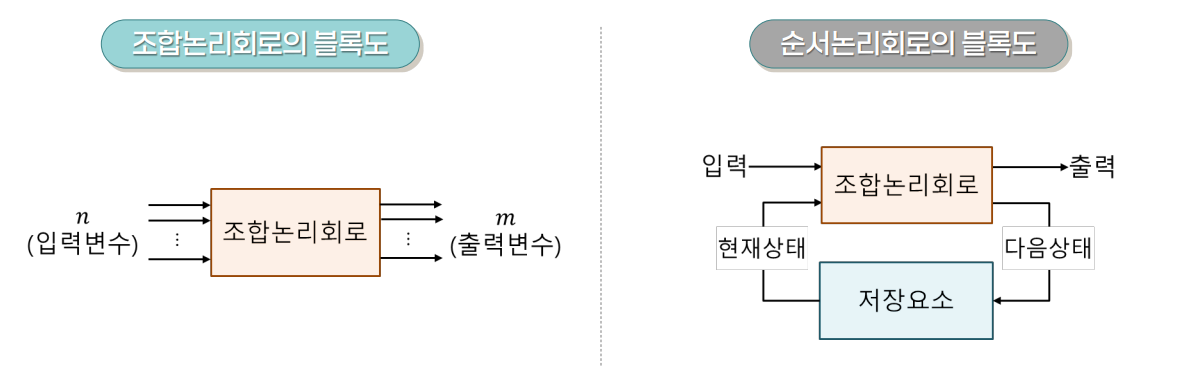

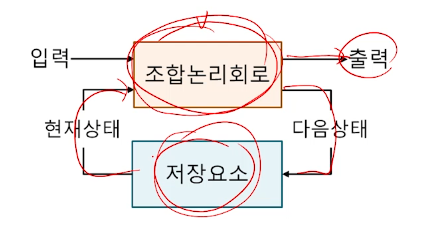

- 조합논리회로

- 현재 입력의 조합에 의해 출력이 결정되는 논리회로

- 순서논리회로

- 현재 입력과 이전 입력 상태(저장 요소의 상태)에 의해서 출력이 결정되는 논리회로

- 논리회로 블록도

- 회로도의 예

1.1 기본 연산회로

- 사칙연산을 수행하기 위한 산술연산회로

- 가산, 감산, 승산, 제산

- 대부분의 컴퓨터에서 산술연산회로는 가산기를 중심으로 구성되며, 덧셈을 응용하거나 변형하여 수행됨

- 논리연산은 가산기와 별도의 논리회로로 수행되지만, 산술연산 관점에서 보면 컴퓨터는 본질적으로 가산기 기반의 장치임

- 가산기

- 2진수의 덧셈을 수행하는 조합논리회로

- 반가산기(HA: Half Adder)

- 두 비트의 덧셈을 수행

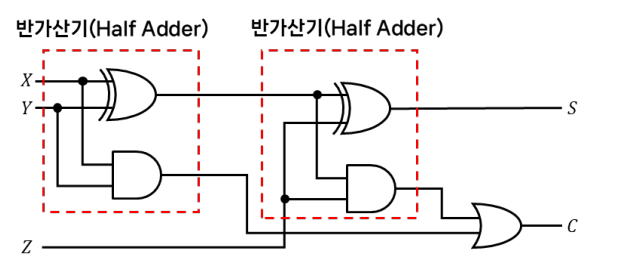

- 전가산기(FA: Full Adder)

- 세 비트의 덧셈을 수행

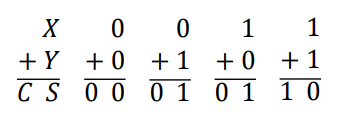

- 반가산기

- 두비트의 덧셈 (S:합, C: 자리올림)

- 간소화 과정을 통해 구해진 불함수

- 두비트의 덧셈 (S:합, C: 자리올림)

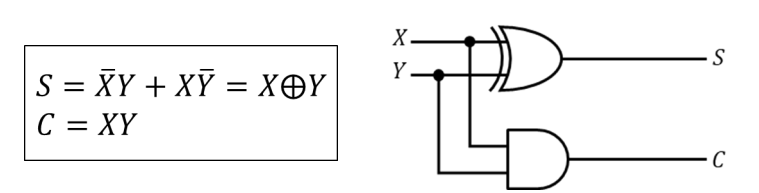

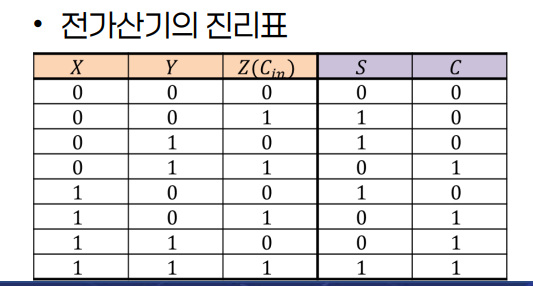

- 전가산기

- 세 비트의 덧셈

- 세 비트의 덧셈

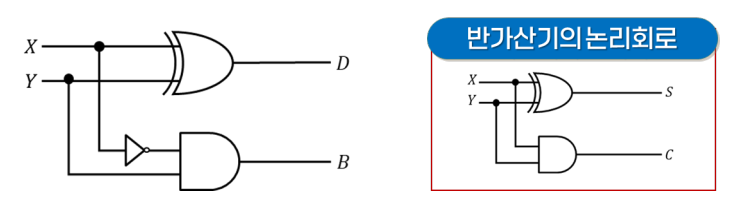

- 감산기

- 2진수의 뺄셈을 수행하는 조합논리회로

- 반감산기(HS: Half Subtractor)

- 두 비트의 뺄셈을 수행

- 전감산기(FS: Full Subtractor)

- 세 비트의 뺄셈을 수행

- 반감산기

- 두 비트의 뺄셈 (D: 차, B: 빌림 수)

- 간소화 과정을 통해 구해진 부울함수

- 두 비트의 뺄셈 (D: 차, B: 빌림 수)

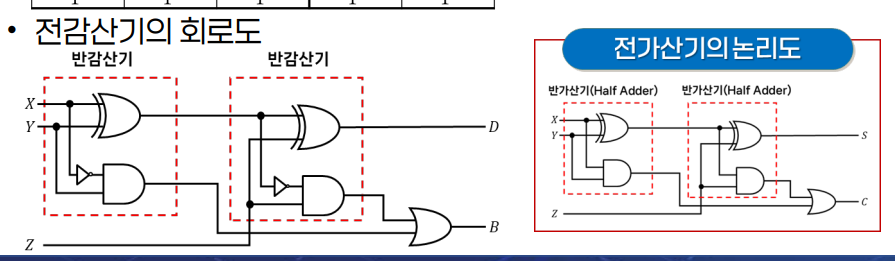

- 전감산기

- 전감산기의 진리표

- 전감산기의 회로도

- 전감산기의 진리표

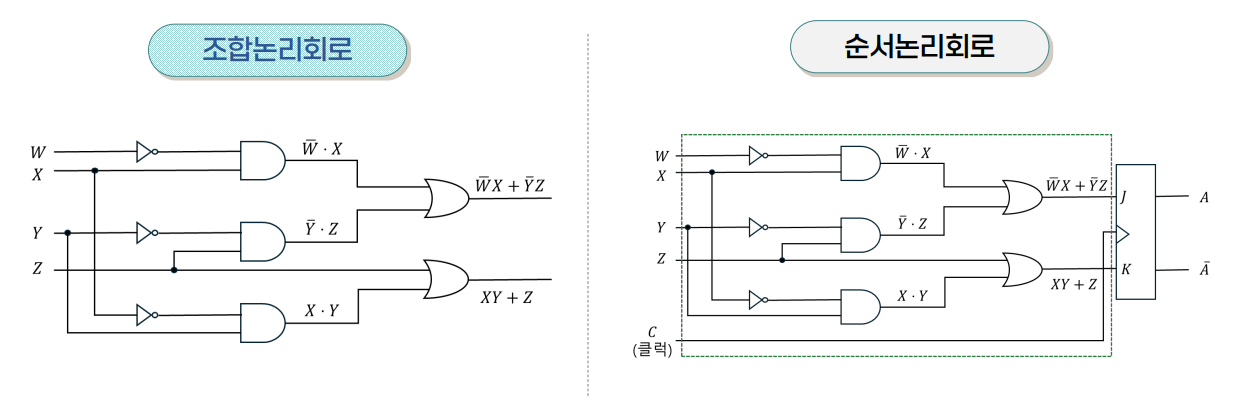

- 가감산기

- 덧셈과 뺄셈을 가산기만으로 수행하는 회로

- 감산기는 가산기에 NOT 게이트만 추가된 형태

- 덧셈과 뺄셈을 가산기만으로 수행하는 회로

1.2 MSI를 이용한 조합논리회로

- 집적회로

- 효율적인 회로를 만들기 위해서는 필요한 게이트의 수, 배선 등 물리적 요소를 최소화할 필요가 있음

- 이를 위해 처음부터 끝까지 직접 최적화 설계를 하는 것은 시간과 비용 측면에서 비효율적임

- 회로를 만들 때에는 이미 최적화되어 패키징 되어있는 집적회로(IC)를 많이 사용함

- 이미 만들어진 회로를 사용하여 다양한 조합논리회로를 설계할 수 잇음

- MSI(Medum Scale Integrated circuits) 장치 (MSI 소자)

- 여러 게이트의 조합으로 특정 기능을 수행하는 중간 규모 집적회로

- 이미 검증된 최적 설계를 제공하기 때문에 설계 생산성을 향상하고 유지보수가 용이해짐

- 논리블록 형태로 사용되기 때문에 설계자가 모든 설계를 직접 할 필요없음

- 대표적인 MSI 장치

- 인코더, 디코더, 멀티플렉서, 디멀티플렉서

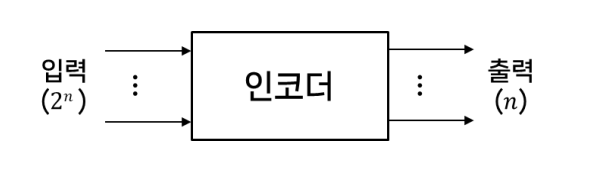

- 인코더(Encoder)

- 부호화되지 않은 입력을 받아서 부호화 된 출력을 내보내는 부호화기

- 입력된 데이터를 특정 형식으로 변환하는 장치

- 인코더는 2^n개의 입력과 n개의 출력을 가지며, 입력값에 대응하는 2진 코드를 출력 값으로 생성함

- 부호화되지 않은 입력을 받아서 부호화 된 출력을 내보내는 부호화기

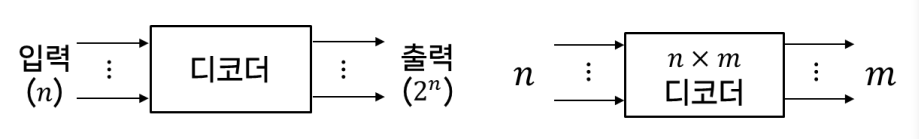

- 디코더(Decoder)

- 부호화 된 입력을 받아서 부호화되지 않은 출력을 내보내는 복호화기

- 입력된 데이터를 해석하여 해당되는 출력 신호로 변환하는 장치

- n비트의 2진 코드를 최대 2^n개의 서로 다른 정보로 변환함

- 2*4 디코더 예시

- 부호화 된 입력을 받아서 부호화되지 않은 출력을 내보내는 복호화기

- 멀티플렉서(Multiplexer)

- 여러 개의 입력선 중에 하나를 선택하여 단일 출력으로 내보내는 조합논리회로

- 특정 입력 신호를 선택하기 위해 선택변수 사용

- 2^n개의 입력 신호 중에서 특정 입력을 선택하기 위해서는

- 여러 개의 입력선 중에 하나를 선택하여 단일 출력으로 내보내는 조합논리회로

2 순서논리회로

- 현재 입력과 이전 입력 상태(저장 요소의 상태)에 의해서 출력이 결정되는 논리회로

저장요소의 유무가 큰 차이점

2.1 순서논리회로

동기화를 어떻게 하느냐에 따라 크게 2종류로 나눌 수 있다.

- 비동기 순서논리회로

- 저장 요소로 시간지연 소자를 사용할 수 있음

- 시간지연소자로 인해 신호가 전달되려면 일정한 시간이 걸리는데 이를 통해 신호를 기억하는 것 처럼 동작하게 할 수 있음

- 구성 요소간 공유하는 기준 타이밍인 클럭이 없기 때문에 여러 신호가 거의 동시에 바뀔 경우, 회로가 예상치 못한 순서로 상태가 변화할 수 있음

- 동기 순서 논리회로

- 특정 순간에만 저장 요소의 내용을 변화시킬 수 있는 신호인 클럭 펄스를 사용

- 클럭 펄스는 시스템 전체에 제공되며, 구성 요소들은 클럭 펄스를 기반으로 동작 타이밍을 결정

- 저장 요소로 플립플롭(flip-flop)을 일반적으로 사용하며, 가장 많이 사용되는 순서논리회로

- 특정 순간에만 저장 요소의 내용을 변화시킬 수 있는 신호인 클럭 펄스를 사용

작업 순서를 완전게 동기화시킬 수 잇다는 안정성 때무넹 동기순서 논리회로가 더 선호된다.

플립플롭(F/F: Flip Flop)

- 1비트의 2진정보를 저장할 수 있는 기억소자 (0 or 1)

- 입력신호에 의해 상태 변경 지시가 있을때까지 현재의 2진 상태를 유지

- 클럭 신호에 의해 출력 상태를 바꿈

종류

- SR 래치

- 넓은 의미의 플립플롭 - "디지털 기반 기억소자" 전체를 일컫는 포괄적인 개념

- 구동 입력이 1일 때 출력이 바뀌는 비동기 순서논리소자

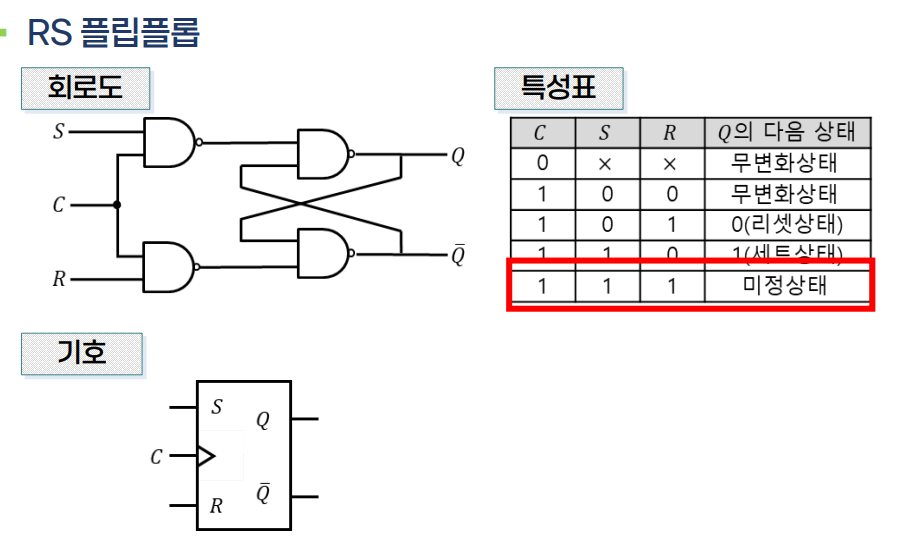

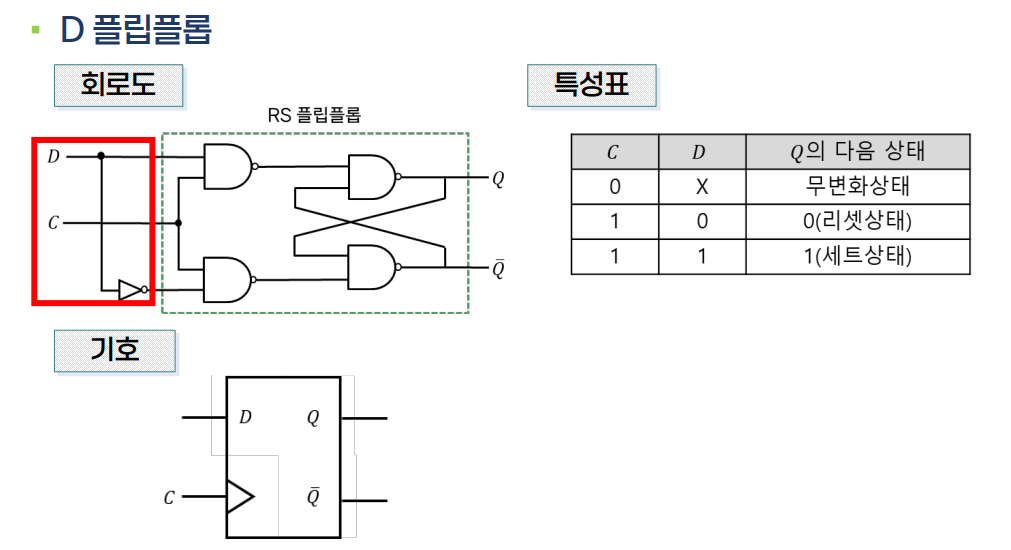

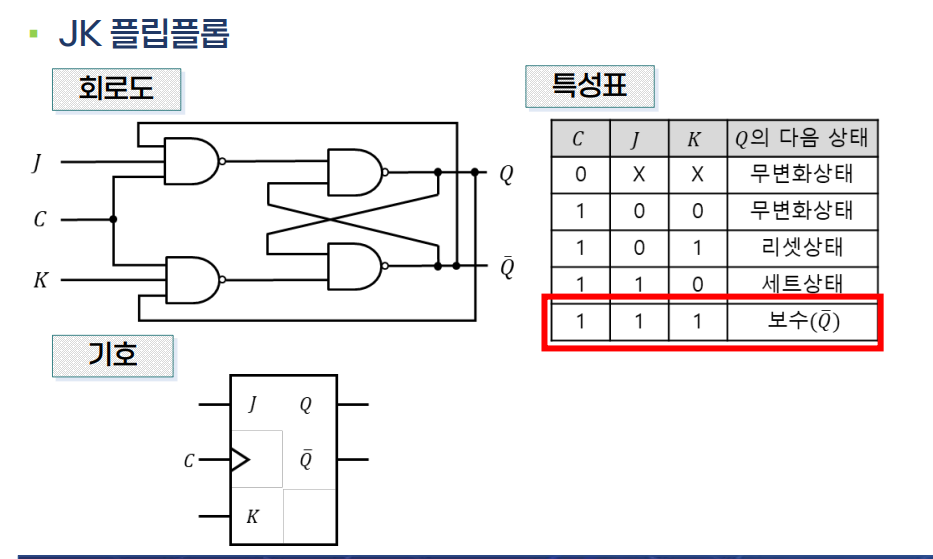

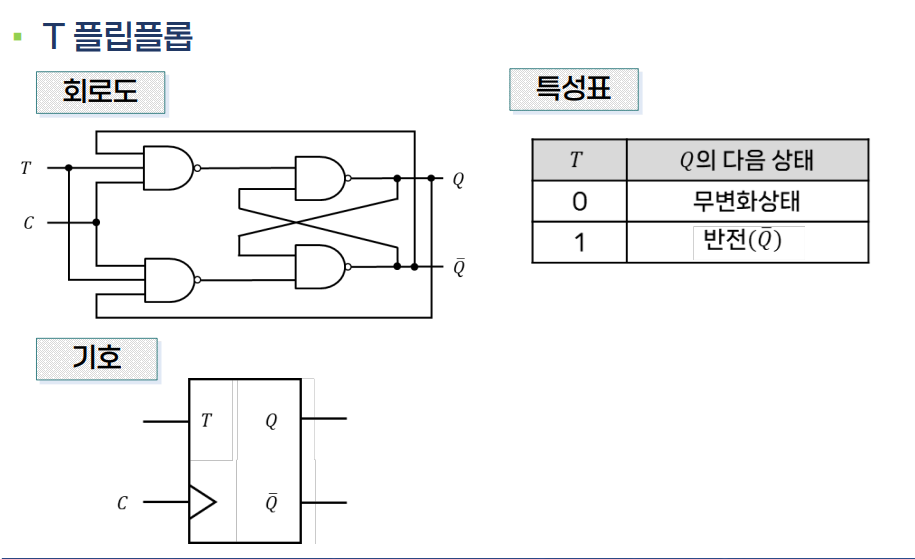

- RS 플립플롭, D 플립플롭, JK 플립플롭, T 플립플롭

- 클럭 신호에 의해 출력이 바뀌는 동기 순서논리소자

단점: 미정상태라는 논리적 오류 상태가 있을 수 있음

가장 간단한 형태의 플립플롭

미정상태가 발생하지 않는 플립플롭

T는 반전 스위칭 때문에 토글의 T를 따온 것

2.2 레지스터

- 데이터를 일시 저장하거나 전송하는 장치

- 여러 개의 플립플롭을 연결하여 구성

- 플립플롭은 1비트의 값을 저장, 여러 개를 연결하여 더 큰 데이터를 저장함

- n비트 레지스터

- n개의 플립플롭으로 구성되며, n개의 2진 정보를 저장

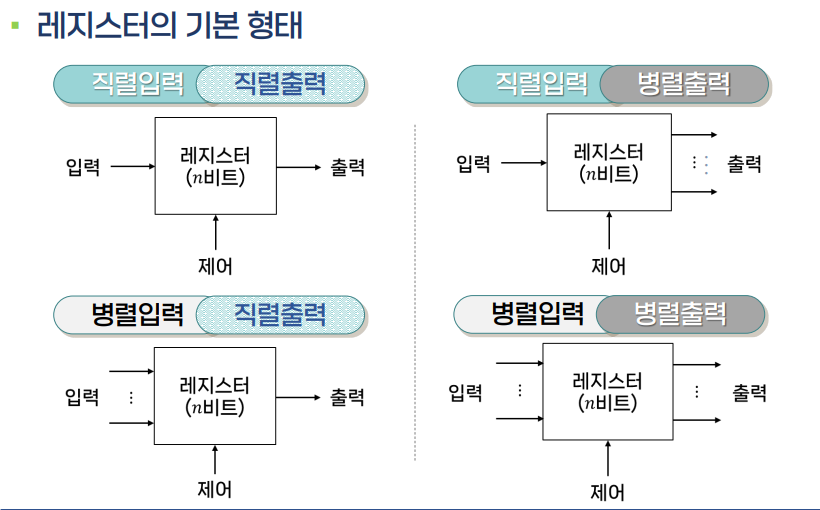

레지스터의 기본 형태

- 데이터 적재 레지스터

- 입력된 데이터를 그대로 기억하는 역할을 수행

- 일반적으로 D 플립플롭을 사용

- 데이터 입력 방식

- 적렬 적재 레지스터

- 병렬 적재 레지스터

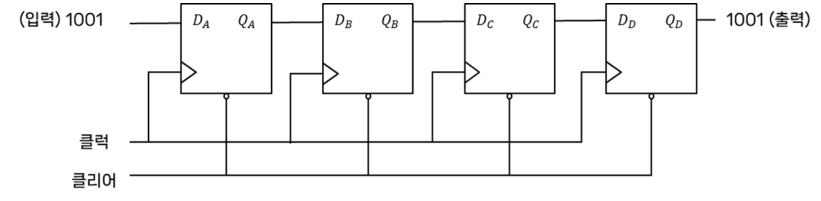

직렬적재 레지스터

- 여러 개의 플립플롭을 연결하여 구성

- 4개의 플립플롭을 연결한다면 4비트의 정보를 저장

- 직렬적재 방식: 직렬 입력-직렬 출력 레지스터

- 데이터를 1비트 씩 순차적으로 입력하는 방식

- 데이터를 1비트 씩 순차적으로 입력하는 방식

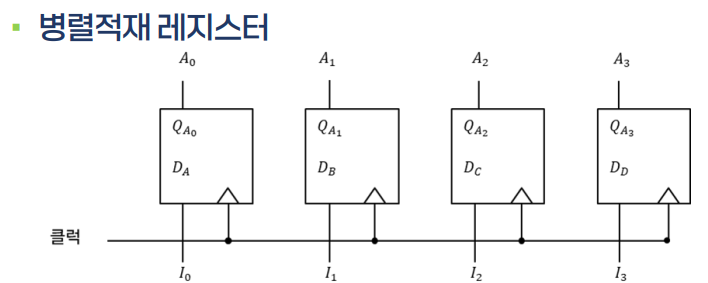

병렬적재 레지스터

- 레지스터에 클럭 펄스가 입력되면 4개의 입력 데이터가 병렬로 적재

- 적재된 내용을 그대로 유지하려면 회로에 클럭 펄스가 입력되지 않아야 함

- 클럭 펄스가 1이면 적재, 0이면 내용 유지

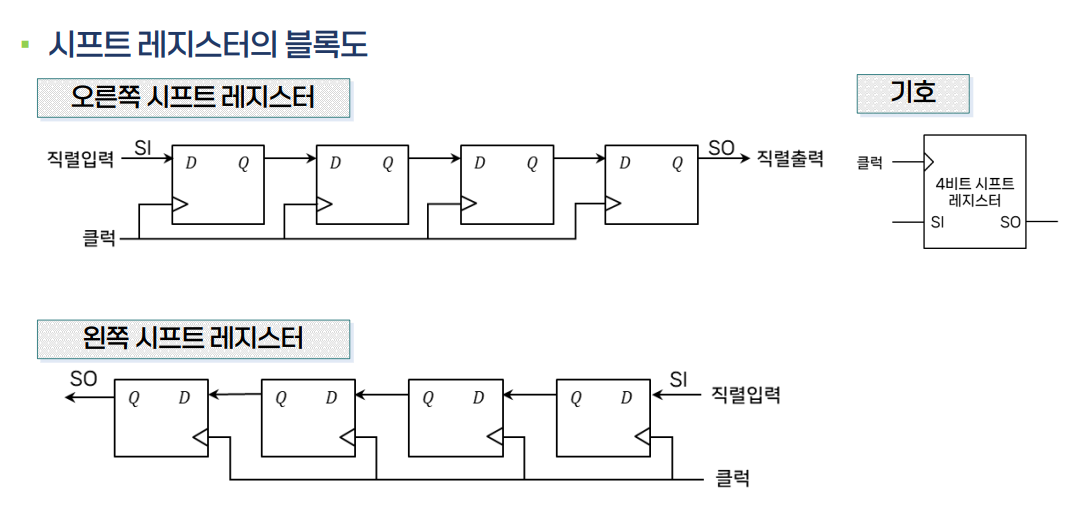

시프트 레지스터

- 레지스터에 저장된 값에 대해 한 방향 또는 양방향으로 저장된 값의 위치를 이동시킬 수 있는 레지스터

- 플립플롭을 직렬 연결, 모든 플립플롭은 공통 클럭 펄스를 사용

- 클럭 펄스에 따라 한 칸씩 자리를 이동

2.3 카운터(Counter)

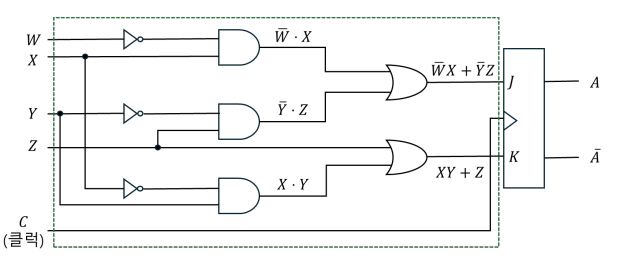

- 플립플롭을 사용해 만든 순서논리회로

- 클럭 펄스의 적용에 따라 미리 정해진 순서에 따라 상태가 변하는 특수한 형태의 레지스터

- 외부 입출력이 없으며, 상태 변화는 클럭 펄스에 의해 수행

- 일반적으로 T 플립플롭이나, JK 플립플롭이 사용됨

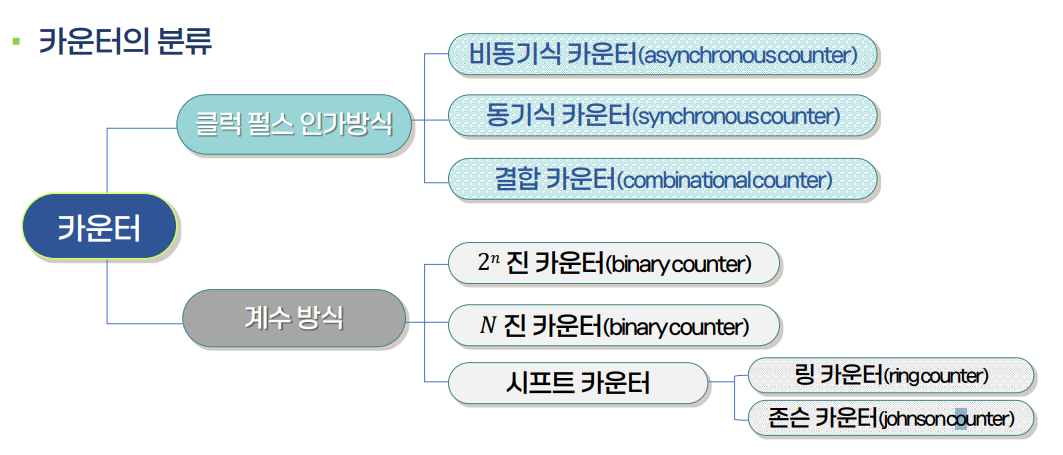

분류

- 카운터를 나타낼 때는 비동기식 2진 카운터, 동기식 10진 카운터 등으로 표현

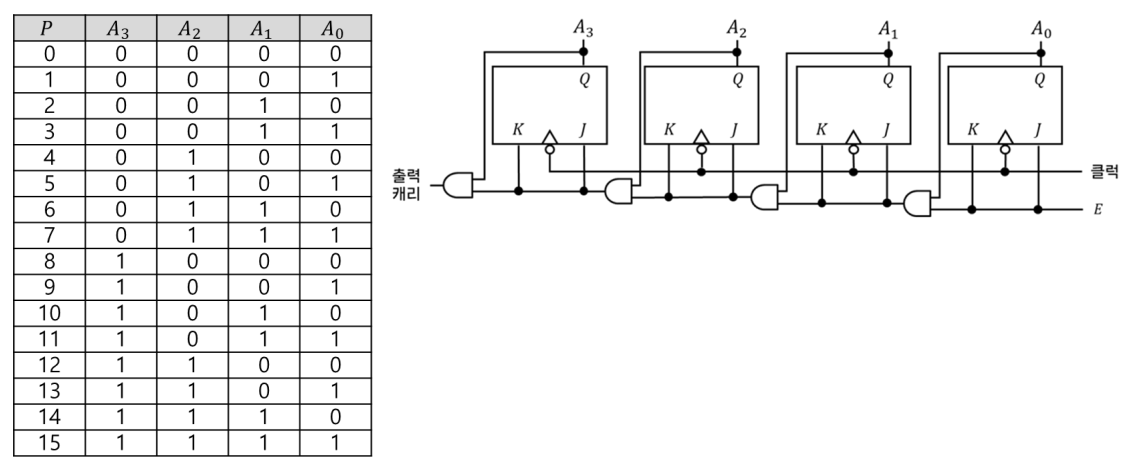

4비트 동기식 2진 카운터 예시