TLB

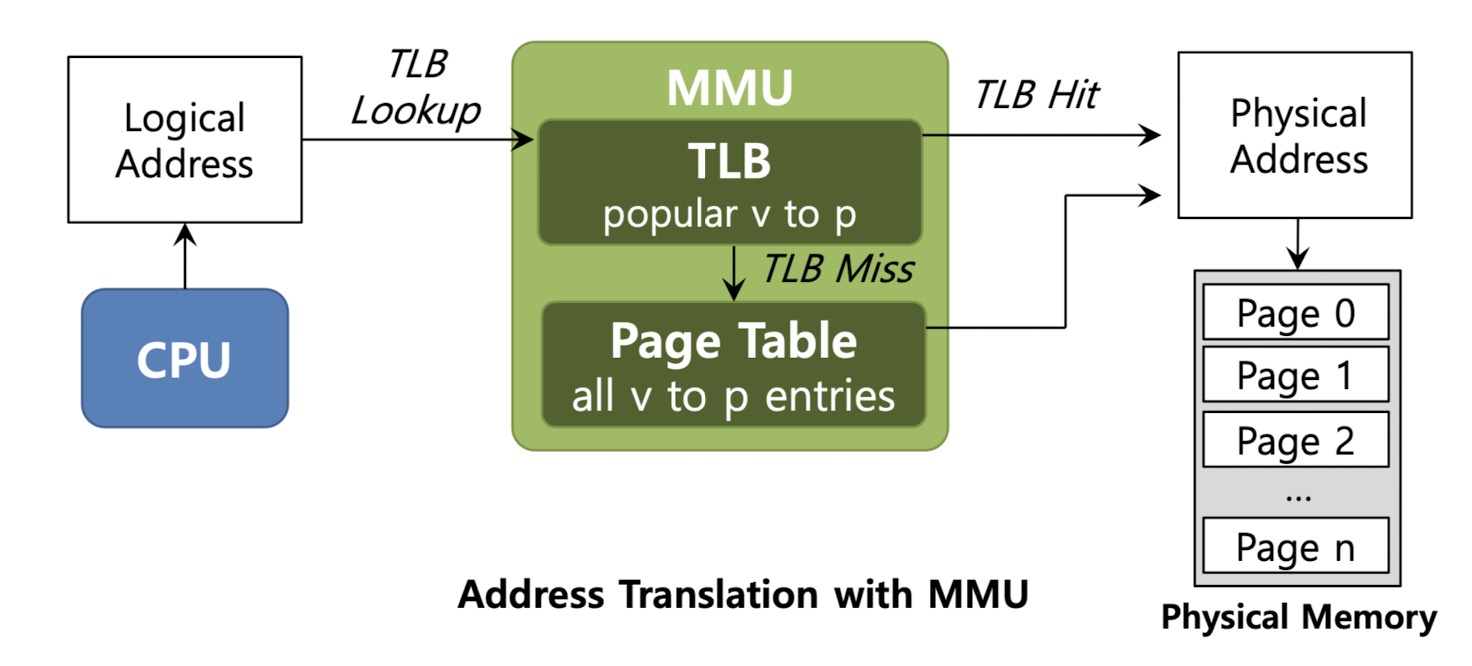

정의

Translation Lookaside Buffer

MMU 내부에 존재

Page Table의 Cache라고 생각하면 편함

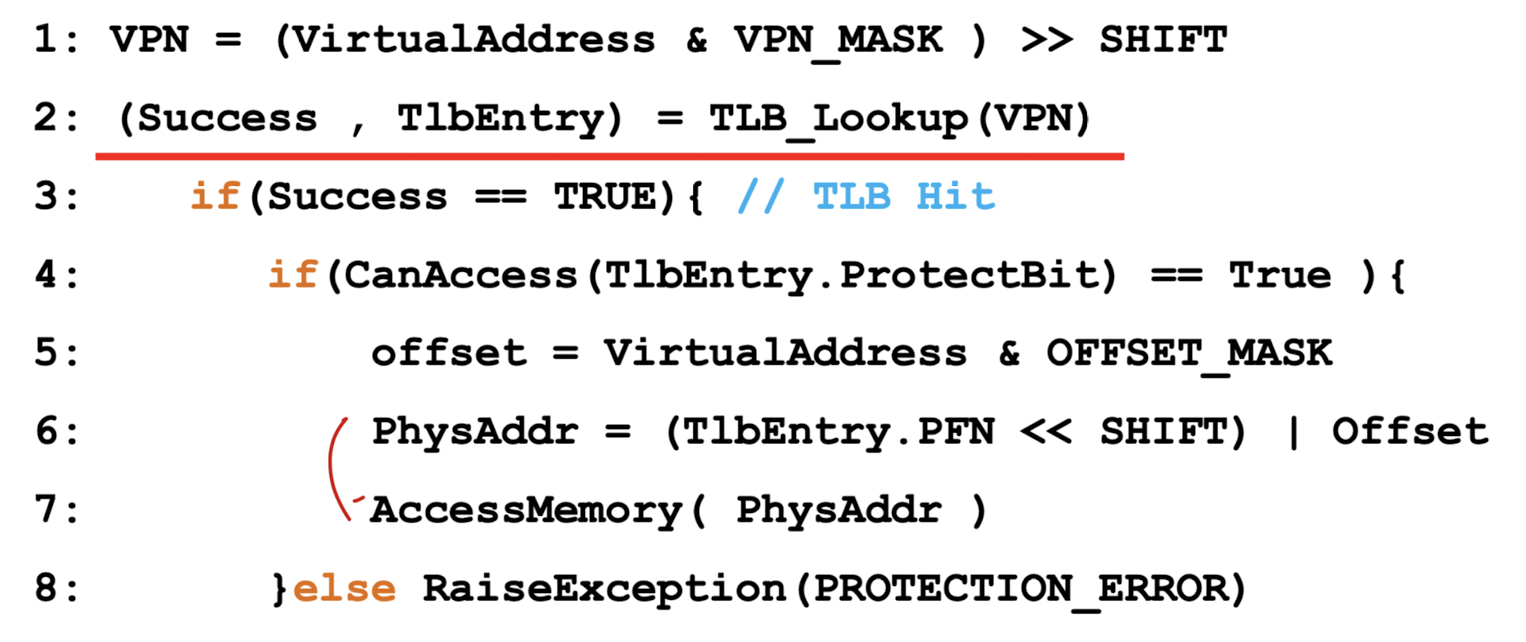

Algorithm

1번 : Page Table의 VPN을 추출

2번 : TLB를 먼저 뒤져봄

3번 ~ : 만약 TLB안에 찾는 page가 있다면(TLB hit)

-> protect bit만 검사하고, 맞으면 바로 추출

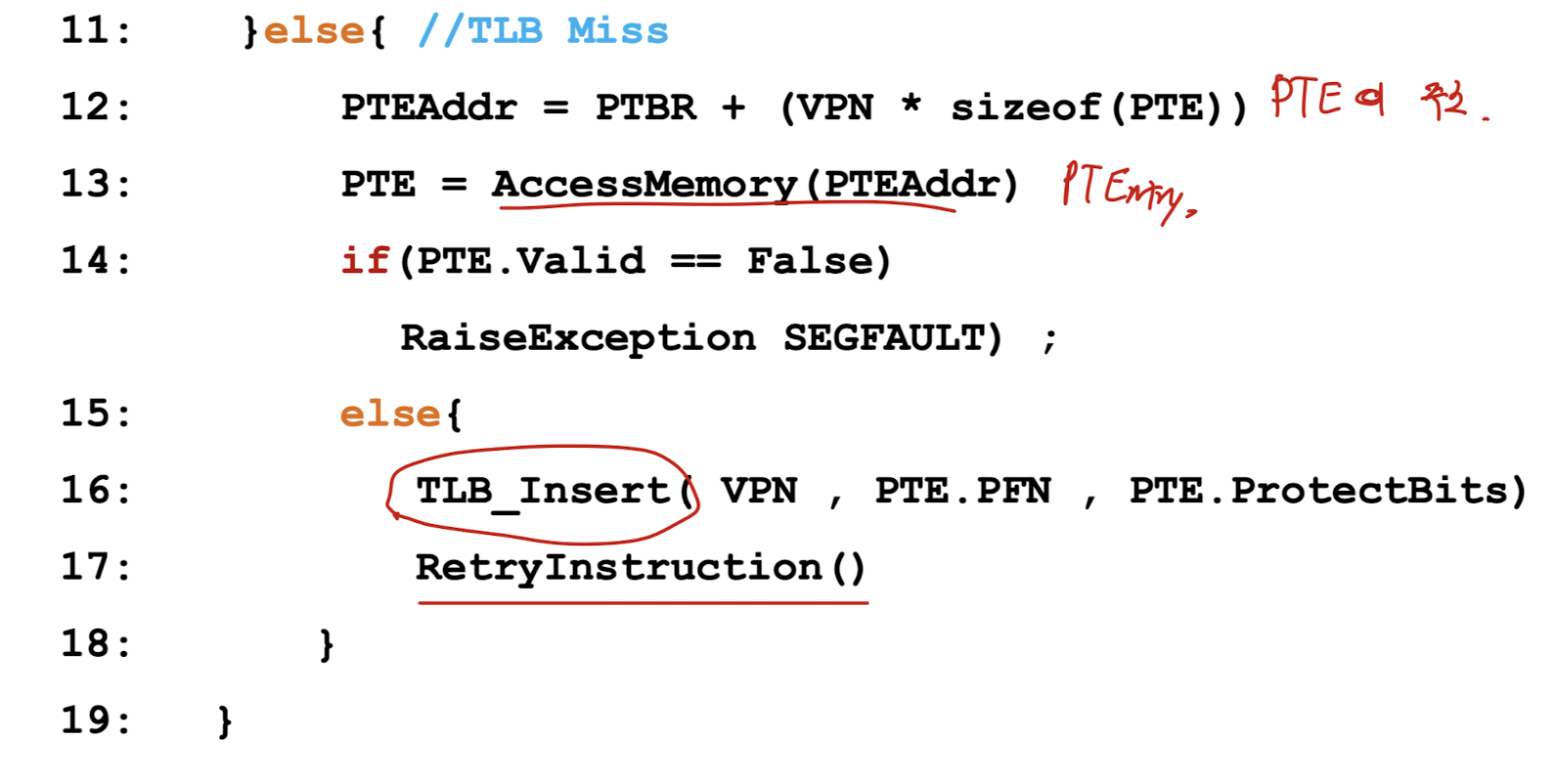

11번 ~ : TLB Miss의 경우

Page Table을 통해서 Page Table Entry 접근

만약 Valid 하지 않으면 -> exception

Valid하면 -> TLB에 집어넣고 다시 실행

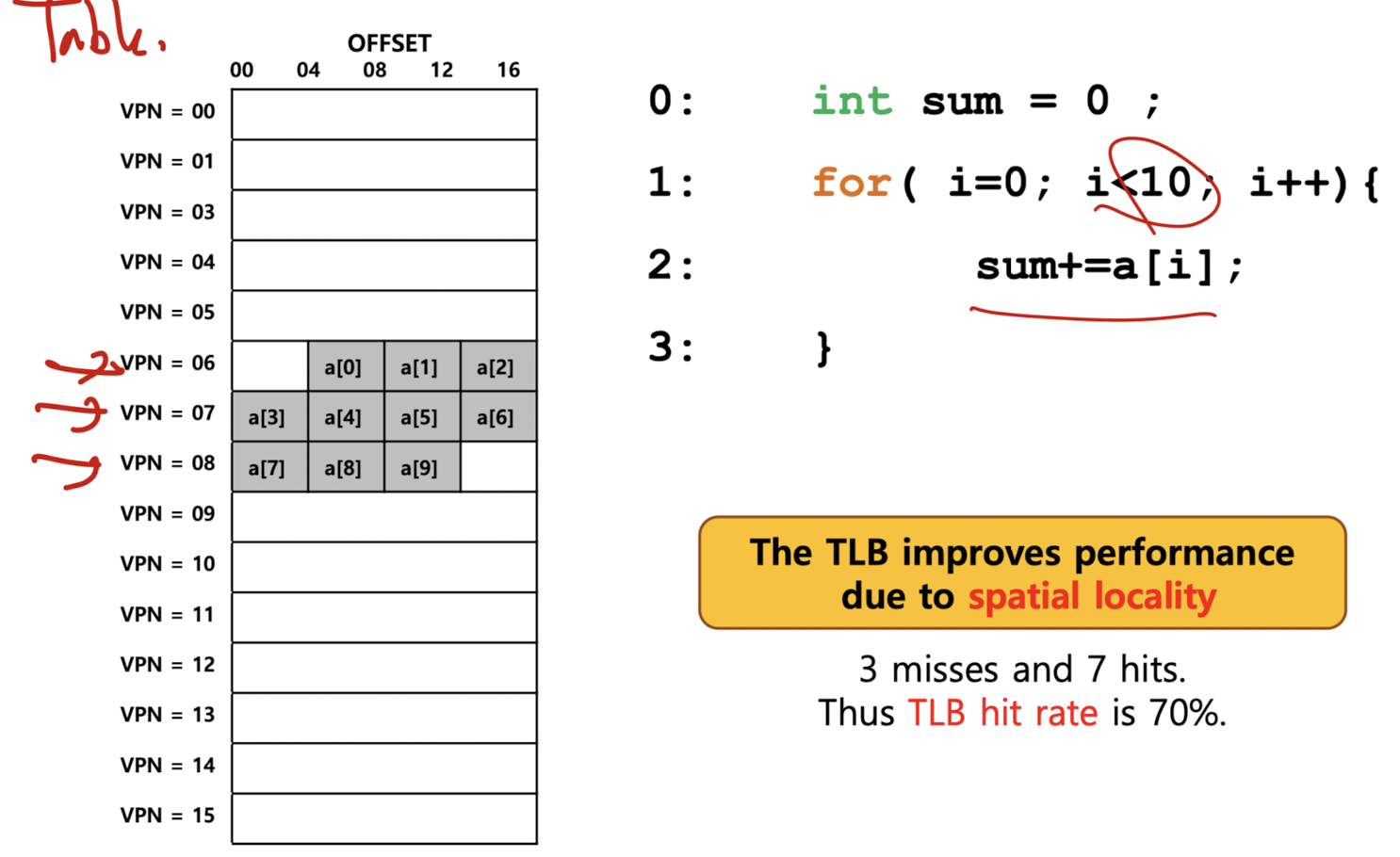

example

이렇게 되어있는 경우 각 TABLE에 처음 접근할 때 1번씩 miss발생하므로 3번 TLB Miss

TLB Miss Handling

by Hardware

CISC

Hardware가 page table의 위치, 구조를 정확히 알고 있어야 함

Hardware가 page table에 들어가서 올바른 entry 추출하고, TLB update하고, retry instruction..

특징

- H/W Design이 complex해짐

- 빠름

by Software

RISC

TLB Miss 발생 시 raise exception

kernel mode로 page table에 접근하여 가져오고 retry

특징

- OS가 동작 -> kernel thread가 동작한다는 것 -> Context Switch overhead(느림)

- H/W Design Simple

TLB Entry

Page Table Entry랑 다름!

PTE는 PFN + other bits

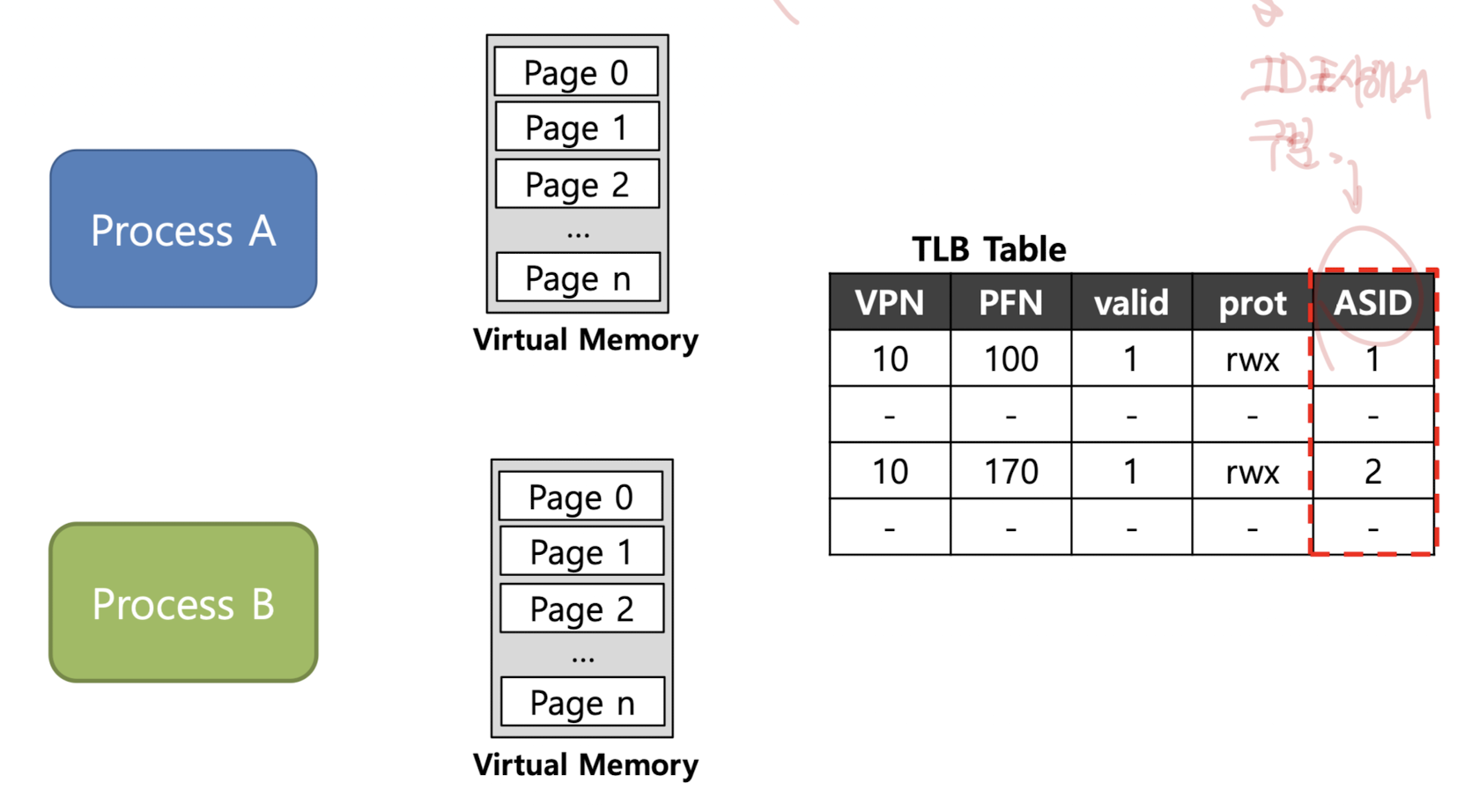

문제: Process간 VPN 겹침

Virtual address는 모든 process가 동일하기 때문에,

서로 다른 process의 page가 TLB에 올라갔을 때 VPN으로 구별을 못한다는 문제가 있다.

해결

TLB Entry에 ASID (ID를 표시)를 통해 각 프로세스를 구분

TLB replacement policy

새로운 entry를 등록할 때, 기존의 entry를 내쫓아야 하는데

누구를 내쫓을까?

LRU(Least Recently Used)

제일 옛날에 쓰였던 애를 내쫓기

reference bit을 통해

Q. 어떻게 알아?

reference bit 일정 시간마다 초기화해주고 access되면 1로 set

그러면 0으로 되어있는 애가 후보가 됨!