Instruction Level Parallelism (ILP)라고 부르는

명령어들의 Parallelism을 활용

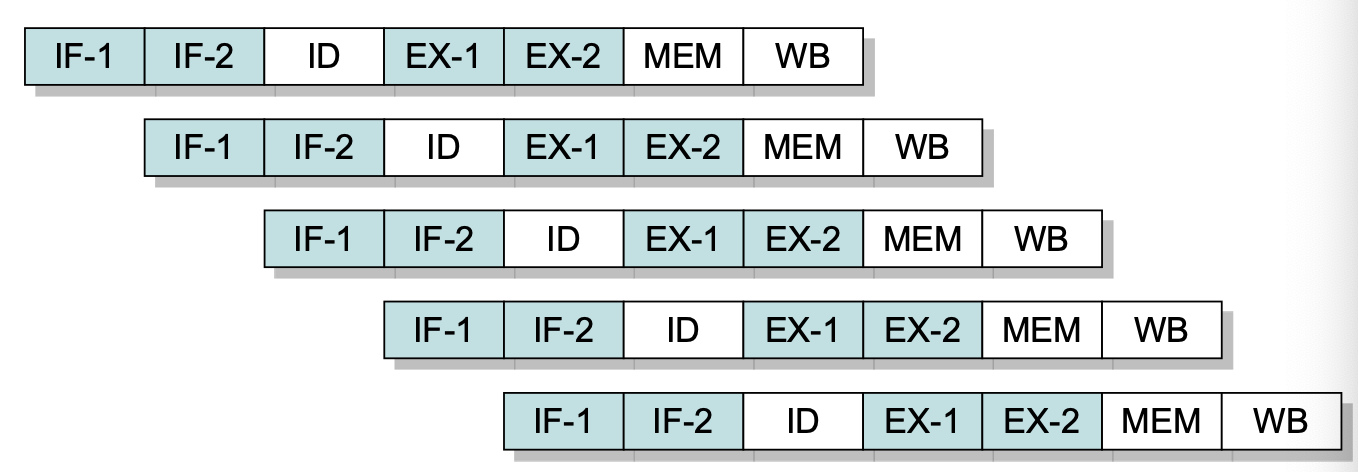

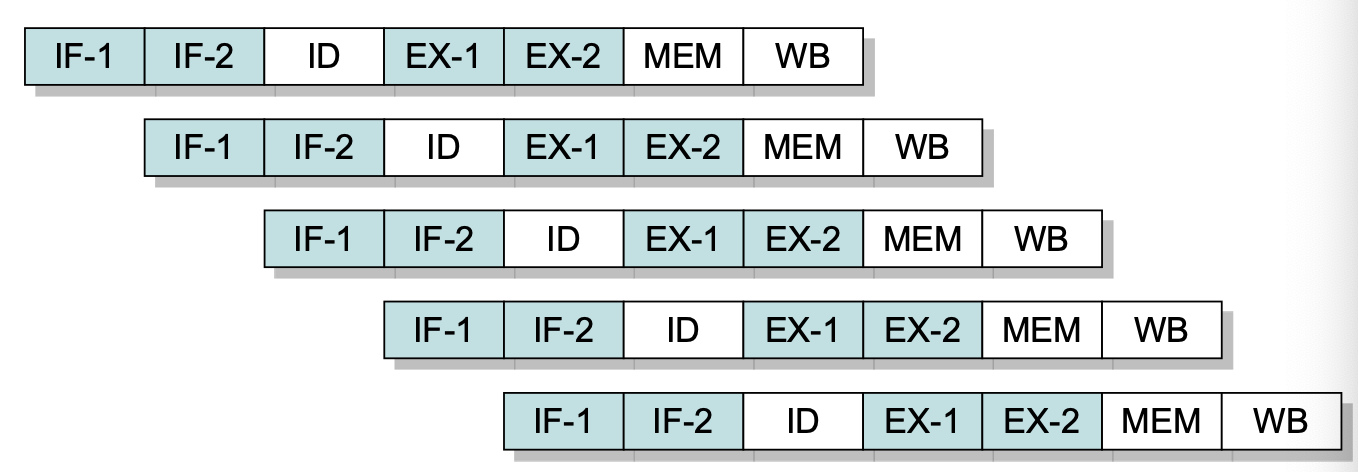

Superpipelining

Clock Frequency를 높이는데 목적이 있음

→ 과거엔 Clock Frequency가 높으면 좋은 것이라는 인식때문

Stage의 수가 더 많아지므로, 그에 따른 추가적인 Stage Register 필요

Hazard Issue가 더 복잡해짐

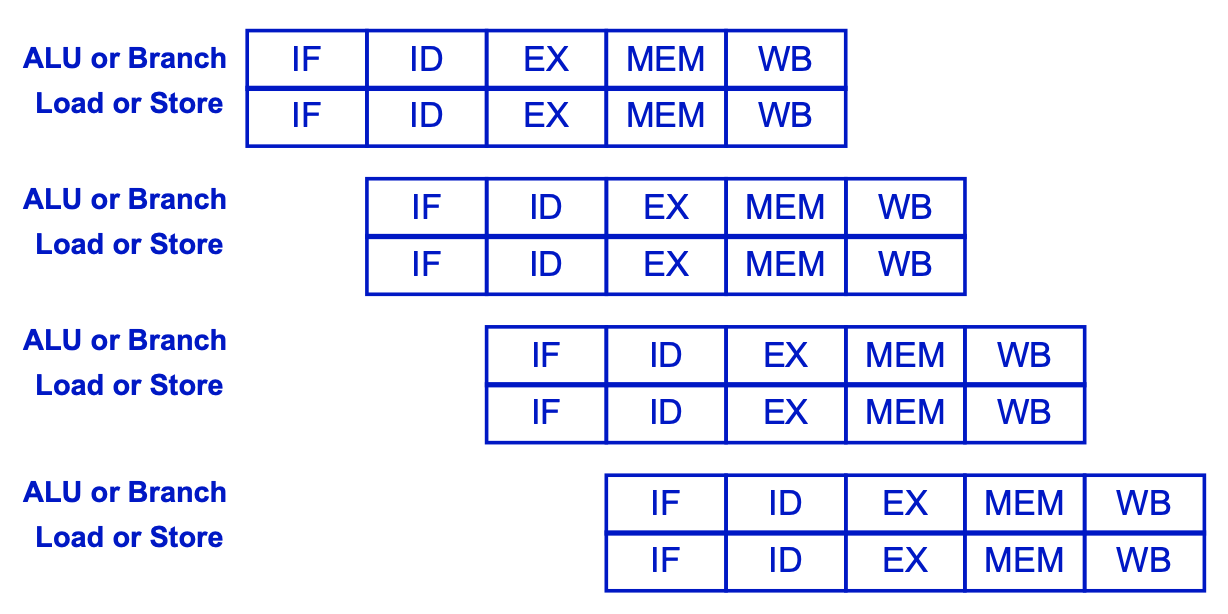

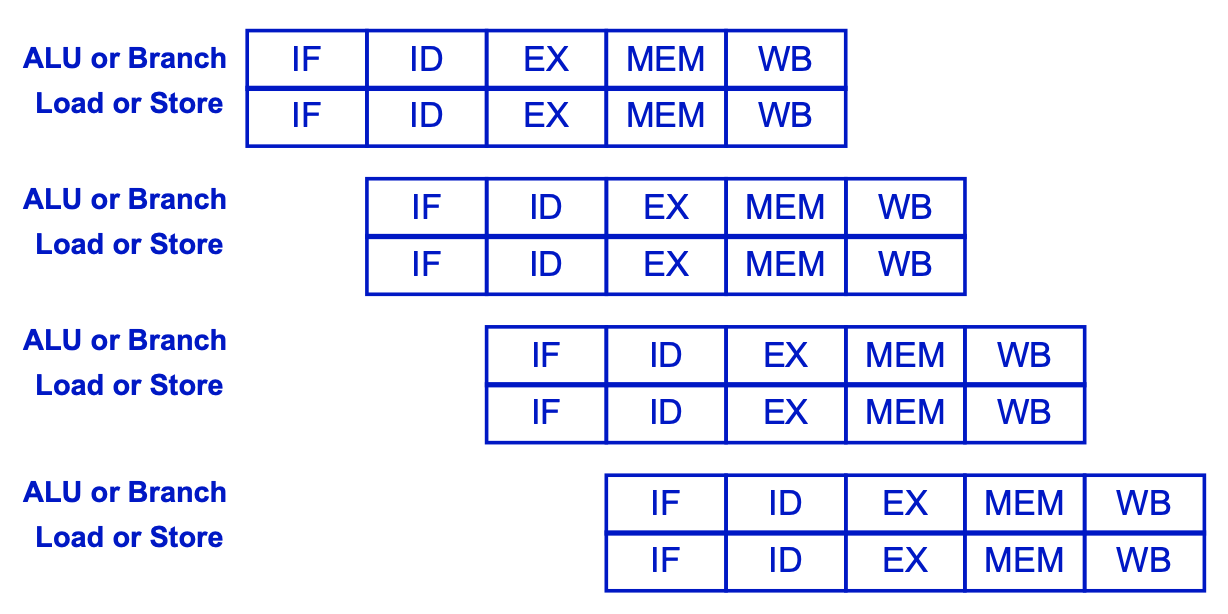

Super-Scalar

명령어들의 Parallelism을 활용

→ 과거엔 Clock Frequency가 높으면 좋은 것이라는 인식때문