CPU의 작동 원리

1. ALU와 제어장치

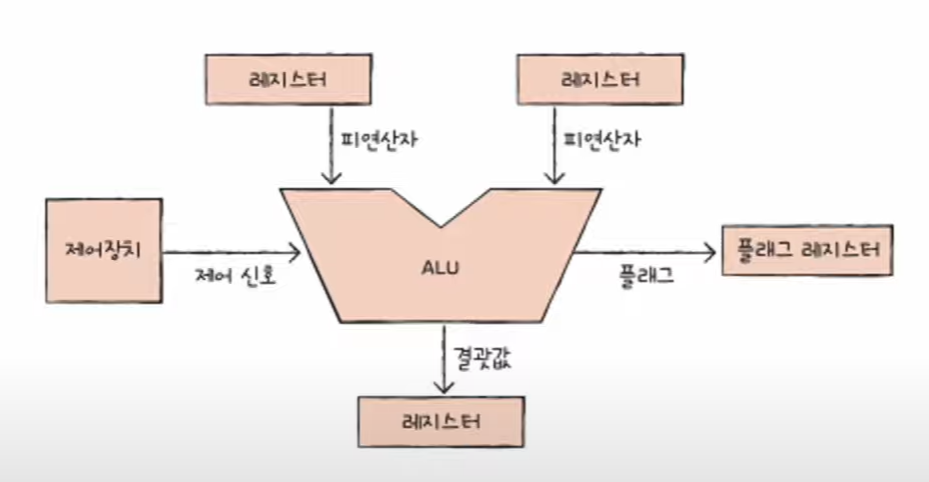

1) ALU

[컴퓨터 공학 기초 강의] 9강. CPU의 내부 구성 - ALU와 제어장치 01:10

- 연산 수행

- 레지스터로부터 피연산자 전달

- 제어 장치로부터 제어 신호 전달

- 결과값을 레지스터로 전달

- 메모리에 직접 접근하는 것보다 속도 빠름

플래그: 연산 결과에 대한 부가 정보 제공, 플래그 레지스터에 저장

- 플래그 예시

플래그 조건 내용 (1일 경우 true, 0일 경우 false) 부호 플래그 연산 결과 < 0 1일 경우 계산 결과가 음수, 0일 경우 양수 제로 플래그 연산 결과 == 0 1일 경우 계산 결과가 0, 0일 경우 0이 아님 캐리 플래그 연산 결과에 올림수나 빌림수 발생 여부 1일 경우 발생, 0일 경우 발생하지 않음 오버플로우 플래그 오버플로우 발생 여부 1일 경우 발생, 0일 경우 발생하지 않음 인터럽트 플래그 인터럽트 가능 여부 1일 경우 인터럽트 가능, 0일 경우 불가능 슈퍼바이저 플래그 현재 실행중인 모드의 커널 모드 판단 1일 경우 커널 모드, 0일 경우 커널 모드가 아님 (사용자 모드)

- 기타 ALU 구성 요소

- 가산기 : 덧셈 연산 회로

- 보수기 : 뺄셈 연산 회로

- 시프터 : 시프트 연산(자릿수) 회로

- 오버플로우 검출기 : 오버플로우 대비

2) 제어장치

-

제어 신호 발생 및 명령어 해석

-

제어 신호: 컴퓨터 부품 관리 및 작동 신호

-

제어 장치의 수신 정보

(1) 클럭 신호 수신

클럭: 컴퓨터 부품의 시간 단위- 하나의 명령어는 하나 이상의 클럭에 걸쳐 실행

(2) 해석할 명령어 수신

- 명령어 레지스터에 담긴 명령어 받아들이고 해석

(3) 플래그 레지스터의 플래그 값 수신

- 플래그 값을 고려하여 제어 신호 발생

(4) 시스템 버스 중 제어 버스로 전달된 제어 신호 수신

- CPU 외부 장치에서 발생한 제어 신호 수신

-

제어 장치에서 발생하는 제어 신호

- CPU 외부 전달 신호

- 메모리 제어 신호 : 메모리에 읽기 또는 쓰기 요청 신호

- 입출력장치 제어 신호 : 입출력장치에 읽기 또는 쓰기 요청 신호

- CPU 내부 전달 신호

- ALU : 수행할 연산 지시

- 레지스터 : 레지스터 간 데이터 이동, 레지스터에 저장된 명령어 해석

- CPU 외부 전달 신호

2. 레지스터

1) 주요 레지스터

(1) 프로그램 카운터, PC, Program Counter

- 메모리에서 가져올 명령어의 주소 저장

- 명령어 포인터

(2) 명령어 레지스터, IR, Instruction Register

- 메모리에서 읽어온 명령어를 저장

- 제어 장치가 해당 명령어를 해석하여 신호 발생

(3) 메모리 주소 레지스터, MAR, Memory Address Register

- 메모리의 주소를 저장

- CPU의 메모리 접근 시 주소 값을 주소 버스로 전송하는 과정에 사용

(4) 메모리 버퍼 레지스터, MBR, Memory Buffer Register

- 메모리와 주고 받을 모든 데이터를 저장하는 레지스터

- 데이터 버스를 통해 현재 메모리에 저장할 값, 전달 받은 값 모두 사용

- = MDR, Memory Data Register

< 레지스터들의 작동 과정 예시 >

메모리 주소 1101 1000 1111 1001 1101 1002 : : 1000 1500 주소 1000 ~ 1500에 저장된 프로그램 실행 시

1) PC에 메모리 주소 '1000' 저장

2) 1000번지에 가기 위해 MAR에 1000 저장

3) '읽기' 제어 신호가 제어버스로, 주소 레지스터 값이 주소버스로 전달

4) 메모리에서 1000번지에 저장된 값을 데이터 버스를 통해 MBR 전달

5) PC값 증가

6) MBR에 저장된 값이 IR로 전달

7) 제어장치에서 IR의 명령어 해석 및 제어 신호 발생

- 프로그램 종료까지 프로그램 카운터가 지속적으로 증가하여 프로그램을 차례로 실행

- JUMP, CONDITIONAL JUMP, CALL, RET 등 특정 메모리 주소로 실행 흐름 이동 시 변경된 주소 저장

- 인터럽트 발생 시에도 실행 흐름 중단

(5) 플래그 레지스터

- 연산 결과 및 CPU 상태 저장

(6) 범용 레지스터

- 특정 용도 없이 다양한 방식으로 자유롭게 사용

(7) 스택 포인터

(8) 베이스 레지스터

2) 레지스터를 활용한 주소 지정 방식

(1) 스택 주소 지정 방식

- 스택과

스택 포인터 (Stack Pointer)사용- 스택 포인터 : 스택의 꼭대기(Top)을 가리키는 레지스터

- 메모리 상에 이런 주소 지정 방식을 위한

스택 영역존재

(2) 변위 주소 지정 방식

- 명령어의 오퍼랜등에 필드 값(변위)와 특정 레지스터 값을 더하여 유효 주소 계산

- PC와 베이스 레지스터 사용

- 사용되는 레지스터가 무엇인지에 따라 상대 주소 지정 방식과 베이스 레지스터 주소 지정 방식으로 구분

i. 상대 주소 지정 방식

- 오퍼랜드와 프로그램 카운터의 값을 더하여 유효 주소 계산

- 분기문(프로그래밍 언어의 if문)과 유사하게 분기를 두어 특정 주소의 코드를 실행 시 사용

ii. 베이스 레지스터 주소 지정 방식

- 오퍼랜드와 베이스 레지스터의 값을 더하여 유효 주소 계산

- 레지스터에 기준 주소값이 들어있고 그로 부터 거리값을 나타내는 오퍼랜드로 구성

(3) 상용화된 CPU 속 레지스터 및 주소 지정 방식

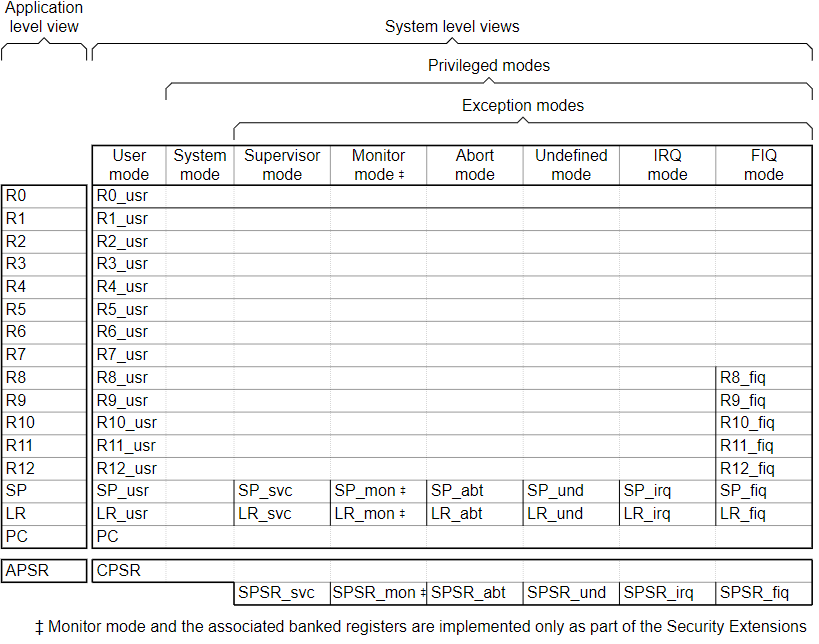

i. ARM

-

ARM 모드에 따라 사용할 수 있는 레지스터 구분 (프로세서 모드에 대한 매뉴얼)

-

범용 레지스터 (General Purpose Register)

- R0 ~ r12, SP, LP

- 최대 32개가 존재하나 모드에 따라 사용 구분, 하나의 모드에 총 15개

ARM 레지스터 구성

-

특수 목적 레지스터 (Special Purpose Register)

- R13, Stack Pointer (SP)

- 32bit 명령어를 사용하는 ARM 모드에서(cf. Thumb모드 : 16bit) 제한된 상황에서 범용 레지스터로 사용 가능

- 그러나 권장되지 않으며 대부분의 경우 스택 포인터로 사용, C, C++ 컴파일러에서는 항상 스택 포인터로 사용

- R14, Link Register (LR)

- 서브루틴 호출 시 리턴 주소를 저장하는 레지스터

- 반환 주소를 SP에 저장하는 경우 범용 레지스터로 사용

- R15, Program Counter (PC)

- 실행된 명령어의 크기씩 증가

- 분기 명령어는 PC에 대상 주소 저장

- APSR, Application Program Status Register

- 프로그램의 상태 플래그 저장

- 저장되는 N, Z, C, V 조건(음수, 제로, 캐리, 오버플로우) 플래그의 사본 값에 따라 조건부 명령어 실행

- 아키텍처에 따라 추가로 저장되는 플래그 종류 증가

- CPSR, Current Program Status Register

- APSR의 프로그램 상태 플래그와 추가 정보 저장

- 프로세서 모드, 인터럽트 비활성화 플래그, 명령어 집합 상태 등

- APSR의 프로그램 상태 플래그와 추가 정보 저장

- SPSR, Saved Program Status Register

- 예외 발생 시 CPSR의 현재 값을 저장하여 예외 처리 이후 복원

- 예외 처리 모드에서만 존재 (사용자 모드 및 시스템 모드에서는 없음)

- R13, Stack Pointer (SP)

ii. x86

-

명령어 길이(16, 32, 64bi)에 따라 사용되는 이름에 차이

이름 16 32 64 용도 Accumulator register AX EAX RAX 산술 연산에 사용 Counter register CX ECX RCX 시프트/회전 연산과 루프에서 사용 Data register DX EDX RDX 산술 연산과 I/O 명령에서 사용 Base register BX EBX RBX 데이터의 주소를 가리키는 포인터로 사용 Stack Pointer register SP ESP RSP 스택의 최상단을 가리키는 포인터로 사용 Stack Base Pointer register BP EBP RBP 스택의 베이스(최하단)을 가리키는 포인터로 사용 Source Index register SI ESI RSI 스트림 명령에서 소스를 가리키는 포인터로 사용 Destination Index register DI EDI RDI 스트림 명령에서 도착점을 가리키는 포인터로 사용 -

현재 상태를 담는 레지스터

- (e)ip, Instruction pointer : 현재 실행중인 명령어의 주소를 저장

- (e)flags : 플래그를 저장 x86 플래그

3. 명령어 사이클과 인터럽트

1) 명령어 사이클

- instruction cycle

- 일정한 주기로 실행되는 명령어를 처리하는 정해진 흐름

- 인출 사이클 : 메모리에 있는 명령어를 CPU로 가지고 오는 단계

- 실행 사이클 : CPU의 명령어를 실행하고 제어 신호를 발생시키는 단계

- 간접 사이클 : 간접 주소 지정 방식 등 추가로 메모리 접근이 필요한 경우

2) 인터럽트

- CPU의 작업이 중단되는 신호

- 동기 인터럽트 : CPU에 의해 발생하는 인터럽트

=예외 - 비동기 인터럽트 : 입출력 장치에 의해 발생하는 인터럽트

=하드웨어 인터럽트

- 동기 인터럽트 : CPU에 의해 발생하는 인터럽트

- 하드웨어 인터럽트

하드웨어 인터럽트 처리 과정

(1) 입출력장치 >> CPU :인터럽트 요청 신호

(2) CPU : 실행 사이클 종료 후 명령어 인출 전에 항상 인터럽트 확인(폴링, Polling)

(3) 인터럽트 요청 확인 :인터럽트 플래그를 통해 현재 인터럽트 허용 여부 확인

(4) 인터럽트 허용 시 : CPU 작업 백업

(5) CPU :인터럽트 벡터를 참조하여인터럽트 서비스 루틴실행

(6) 인터럽트 서비스 루틴 종료시 : 4의 백업 작업 복구 및 실행 재개

- 인터럽트 요청 신호 : CPU의 실행 흐름 중단 요청

- 인터럽트 플래그 : 인터럽트 허용 여부 확인을 위한 플래그

- non maskable interrupt : 인터럽트 플래그와 관계없이 처리(정전, 고장 등)되는 인터럽트

- 인터럽트 서비스 루틴, ISR : 인터럽트 처리를 위한 프로그램

= 인터럽트 핸들러, interrupt handler - 인터럽트 벡터 : 서로 다른 인터럽트 서비스 루틴을 식별하기 위한 정보, ISR 시작 주소 포함

3) 예외의 종류

fault: 예외 처리를 위한 인터럽트로 CPU 작업 중단 이후 예외가 발생한 명령어부터 실행 재개trap: 예외 처리 이후 예외가 발생한 다음 명령어부터 실행을 재개, 디버깅 시 중단점 역할abort: CPU가 실행 중인 프로그램을 강제로 중단시키는 오류 발견- 소프트웨어 인터럽트 : 시스템 호출 발생 시

참고자료

📚강민철, 『혼자 공부하는 컴퓨터 구조 + 운영체제』, 한빛미디어, 2022.

📹유튜브 공식 강의 9, 10, 11강

🐈⬛책 부록 GitHub

🖥️ARM Developer Manual - ARM Registers

🖥️x86 Architecture Registers