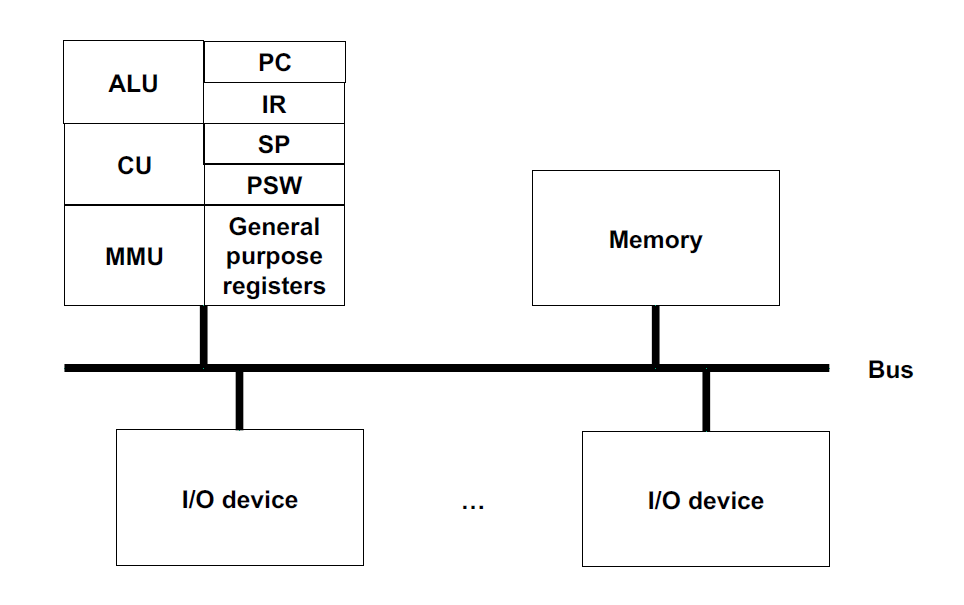

CPU

-

CPU architecture

- ALU(Arithmetic Logic Unit) : 산술 연산, 논리연산자 수행

- CU(Control Unit) : return, goto 등을 처리

- MMU(Memory Management Unit) : 하드웨어적인 처리

-> 메모리를 효율적으로 관리하도록 - PC(Program Counter) : 수행해야 할 명령어가 있는 주소값을 저장

- IR(Instruction Register) : 저장된 주소값에서 명령어를 가져옴

- SP(Stack Pointer) : 메모리 프로세스가 동작을 할 때, STACK의 정보를 저장

- PSW(Process Status Word) : 프로세스(실행된 프로그램)의 상태값(wait, ready, running 등) 저장

- General purpose registers : 범용으로 사용가능. I/O device를 컨트롤(ex 1번 device는 register 10번) 하며 임시로 데이터를 저장

-

Instruction Set Architecture (ISA)

-

CISC (C - complexed)

= 초기 계산기 형태일 때 우세, 복잡한 명령을 수행할 때, 여러 instruction을 하나의 instruction으로 합친다- 장점 : overhead를 줄일 수 있다

- 단점 : CPU 설계가 복잡하고 어려워진다

-> HW 적인 한계 도달

-> 최소한의 instruction들의 조합으로 CPU를 동작시키자! -> RISC 등장

-

RISC (R - reduced)

- 단점 : Cache가 많이 필요하며 비싸다

- 장점 : Pipelining

ex) ARM

-

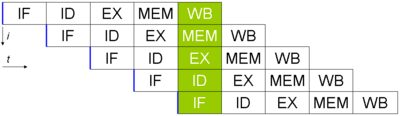

Pipelining -> RISC의 최대 장점

= 종속성이 없는 process들을 겹쳐서 수행

- Fetch : Program count(PC)에 있는 주소에 저장된 instruction을 가져온다

- Decode : CPU가 어떤 instruction인지 파악

- Execution : 실행

- Write-back : 마무리 ex) 메모리 갱신

-> 최대 4배의 성능개선

- 성능 저하 요인

- 실행시간 차이 : 실행 시간이 길면 다음 과정이 밀린다

- 종속성 -> ex) Wb 결과 데이터가 다음 과정에서 사용될 때

- 분기가 생길 때 -> ex) CFI(controll flow instruction) - return, branch, jump, if

+) Instruction-Level parallelism (ILP)

= pipeline과 다르게 병렬적으로 수행- VLIW : complie 타임에 동시에 실행할 수 있는 명령어들을 미리 파악 -> binary code를 분석해서 병렬적으로 동작하게 한다

- Superscalar : CPU가 프로그램을 실행시키면서 동시동작 할 process를 찾는다

-

-

CPU operation

-

Von Neumann architecture

[ CPU ]–[ Memory ]

Memory에 data와 code를 모두 저장 -

Harvard architecure

[ Code ]-[ CPU ]-[ Data ]

code와 data를 분리해서 저장 -> 빠르지만 하드웨어 복잡도가 높다

-

Architecture

- Multi-core architecture

CPU는 하나, CPU는 여러개의 코어를 갖는다 - Symmetric multiprocessing architecture

독립적 CPU가 여러개, Memory를 공유해서 사용 - NUMA multiprocessing architecture

CPU마다 memory를 가진다 ex) 기상청 슈퍼컴퓨터 - Clustered system architecture

- Parallel : 하나의 컴퓨터에 여러 CPU -> 연산을 분산시켜 동시동작 하도록

- Distributed system : 독립적인 컴퓨터 n개가 네트워크로 연결 / 하나의 컴퓨터가 고장나도 나머지가 일을 처리하면 문제가 발생하지 않기 때문에 다용성이 좋다

ex) 서버