< 컴퓨터 구조 >

-

컴퓨터 시스템 : 하드웨어 + 소프트웨어 구성

-

소프트웨어 : 운영체제(Linux, MacOS, Windows), 응용 프로그램(운영 체제로 돌아가는 프로그램들)

-

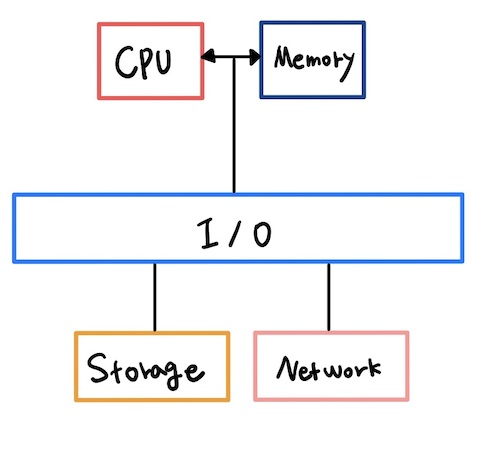

4대 하드웨어 : CPU(중앙처리장치), Memory, Storage(SSD/HDD(하드디스크) 저장매체), Network

기존에는 어떤 프로그램(동작 부품)을 만들기 위해서는 하드웨어(로직)를 매번 각각 만들어줘야했음 → 비용이 늘어나고, 수정이 번거로움, 다른 작업 수행 시 스위치 설치, 전선 재배치 하여 데이터 전송, 신호처리

📌

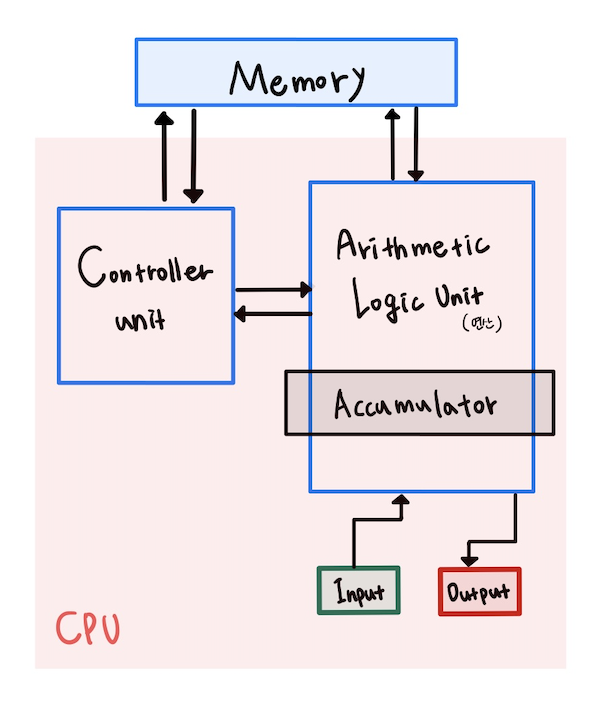

폰노이만 구조(=현 컴퓨터 구조)

- 폰노이만이 제안한 구조, Memory에 프로그램과 데이터가 저장

- → 이 이후는 소프트웨어만 교체하면 ok

- 명령코드를 메모리에 순차적으로 올려놓음 → CPU가 그 코드를 읽어서(controller unit) 코드에 쓰여져 있는 명령 대로 실행 → 메모리에 있는 코드도 프로그램에 따라 바꿔주면 → CPU라는 하드웨어 하나, 메모리 하나에 여러가지 프로그램을 돌릴 수 있다는 제안을 함

- 모든 컴퓨터에 CPU, memory, 저장매체 ; 실행을 시키려면 반드시에 해당 코드를 메모리에 올려두고 CPU가 하나씩 읽을 수 있도록 해야 함

- 구조 ; CPU, memory, 프로그램으로 구성

📌

컴퓨터 주요 구성요소

- CPU(Central Processor Unit) :

-

연산 ALU (Arithmetic Logic Unit)

- 산술연산(계산) : Arithmetic Operation , 1+1

- 논리연산(조건) : Logic Operation, 조건문

-

제어 Control Device - I/O Device(입출력장치), 메모리, ALU 동작 제어

- Memory(코드와 데이터를 저장하는 장치) :

프로그램, 프로그램 수행에 필요한 데이터를 저장 (전체 데이터 저장)

-

내부기억장치(주기억장치) :

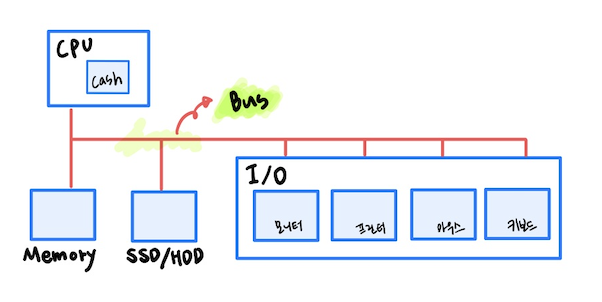

- CPU 안에 레지스터(작은 저장공간, 변수 선언 등의 임시저장)

- 캐쉬(일정 기간 안에 사용했던 기존 데이터를 넣는 곳으로 메모리보다 가까운 곳, 여기서 데이터 가져옴)

- DRAM등 메모리 (램, RAM, DDR4) (임시적으로 저장하는 ) == 속도가 빠르고, 컴퓨터가 꺼지면 다 날라감

-

외부기억장치(보조기억장치) :

- SSD, HDD ; 꺼져도 남아있지만, 주기억 장치보다는 속도가 느림

- I(intput)O(output) Devices(입출력 장치) :

- 입력 장치 : 마우스, 키보드, 터치패드 →신호를 컴퓨터에 줌

- 출력 장치 : 모니터, 프린터, 스피커 등 → 컴퓨터가 출력한 내용을 보여줌

- 버스(Bus) :

세 가지 핵심을 연결해주는 기능

- CPU, Memory, I/O Devices를 연결해 통신이 가능하게 하는 장치, 개별적인 I/O Devices들을 연결해주고 데이터를 송수신해주는 장치

📌

비트 표현 이해

0과 1로 커뮤니케이션, 숫자 표현 가능, 문자 표현 가능, 연산 가능

비트 : 0 or 1 로 프로그램이 동작

- 논리연산 Gate

and (직렬)/ or(병렬) 논리 연산 (조건문)

↔ nand / nor

→0과1로 비트를 엮어서 문자, 숫자 의미 부여 가능

인풋에 따라 아웃풋이 회로를 따라서 논리적으로 동작 = 논리연산 구성 가능 → 논리 연산 가능한 회로 구성 가능

부울 대수식 : 하드웨어를 구성해서 좀 더 복잡한 구성을 하려면 많은 게이트들이 필요한데, 이걸 더 간단한 형식으로 표현한 것

(이진수의 덧셈)

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1 // 논리 연산이 or 연산과 동일

1 + 1 = 0 → 하지만 다음 자릿수를 1을 더해야 함 (carry 비트) → 10

- 반가산기 (half adder) : 두 bit를 덧셈하는 가산기를 의미 ↔ 전가산기 : 두 bit 외, carry까지 계산할 수 있는 가산기를 의미

- 각각 하나의 bit인 A와 B를 더해서, 합 S와 자리올림(carry) C를 출력하는 조합논리회로

- 전가산기 (full adder) : A bit, B bit, carry bit 값을 입력으로 받아서, sum과 carry 값을 출력해줌

📌

Oscillator

, Output 값이 0과 1를 반복하는 회로

전원을 받았을 때마다 CPU가 모든 동작을 한 번에 수행함

- 클럭(0과1로 일정하게 왔다갔다 → 1싸이클, 주기)을 만들 수 있음

- 1GHz = 1,000MHz=1,000,000,000Hz

- CPU : 2.5GHz * 1,000,000,000Hz 만큼의 사이클이 생김, 각각 사이클 마다 CPU가 명령 동작 수행

- 오버클럭 : 작동을 좀 더 빠르게, 원래는 2.5GHz 만큼 동작하는 클럭의 주기를 더 높인 것 → 더 빠르게 움직이니까 열이 🔥

📌

플립플롭(flip-flop)

데이터를 저장하는 조합 논리 회로 —> 이를 통해 메모리를 구성

스위치를 켜고 끄기를 저장 가능 → 이전에 전기를 켜고 끄기라는 사실을 회로가 기억할 수 있게 함

💡 on - 최근에 첫 번째가 켜졌었음

💡 off - 최근에 두 번째가 꺼졌었음R-S(Rset-Set) flip-flop, NOR Gate

Q = output

= Q의 반대값

S와 R이 동시에 1인 건 논리적으로 말이 안 됨

Level-triggered flip-flop

- Hold that bit(=클럭), reset과 set → AND 게이트로

D-type flip-flop, 두 개의 input(RS)을 하나의 input(Data)으로 바꿈, 1이 되면 홀드댓 비트가 클럭이 1이 되는 순간 저장이 됨, 하나의 데이터를 저장할 수 있음(전가산기와 비슷)

Level-triggered(Hold that Bit가 1일 때만=특정한 일정한 클럭, 레벨이 튈 때만)D-type(데이터 저장) flip-flop ,

레벨에 맞춰 플립플롭이 동작할 수 있게끔 논리 회로를 만들 수 있다 → 이러한 논리 회로를 이용해 메모리를 구성함

- 1 bit latch = Level-triggered D-type flip-flop ,(write = 클럭)

- 8 bit latch 8 bit 저장 (= 2의 8승 = 256) → latch 8개를 연결 write가 1일 때 8bit data inputs가 8bit data outputs에 저장, 값이 유지됨

- 8-to-selector (부품), 8비트 데이터에서 특정 비트 값만 출력 데이터를 저장하면 어느 위치에 저장했는지, 저장한 데이터 중에 가지고 오고 싶은 데이터가 어느 위치에 있는 데이터인지 선택해줄 필요가 있음 → 데이터의 특정 주소가 필요 8개의 신호를 데이터에 연결 → 특정 데이터만 선택 가능

- 3-to-8 decoder 8개의 공간 중 한 공간을 선택하고 선택한 공간에서 데이터를 사용

- 온전한 8 bit latch = RAM(Random Access Memory), 8개 중 하나의 비트를 선택해서 쓰거나 읽을 수 있음

RAM array (8x1 Ram을 하나씩 추가→8x2, 16x1 = 램을 여러 개 추가 = m * n RAM array)

-

8 x 2 RAM array (16개X 두 개의 데이터를 한 번에 쓰고 한 번에 읽음)

데이터 8개 저장, 읽음 → 각 데이터 2bits

-

16 x 1 RAM array = 8 x 2 RAM array구조 + select, 1-to2 decoder/ 2-to-1 selector 추가

데이터 16개 저장, 읽음→ 각 데이터 1bits (데이터 공간 16개 중에 하나)

- 램을 여러개 연결, 여러 개의 select로 decoder/selector를 구성해 많은 데이터를 읽고 저장함

64K RAM

2의 16승(주소) X 8 bits(데이터) → 65,536개의 데이터 저장 및 사용 가능한 메모리

- 메모리 공간들은 주소(이진수로 표현된)가 있다 !

📌

Accumulator (가산기)

CPU 안 덧셈 기기 → 데이터를 한 번에 넣어서 계산하는 게 아니라 하나씩 넣어서 축적

clear(계산을 위한 추가 스위치) = 1 → Q output = 0 ; f-f 값을 삭제

CPU 안, 데이터 처리를 위한 임시 저장공간 = Register 저장 공간 (1 cycle),

메모리까지 닿기 위해 상대적으로 많은 싸이클 필요

→ 클럭이 계속 튕기지만 중간에 다른 계산 수행이 더뎌짐(데이터가 와야 처리가 가능하니까)

→ 메모리 데이터를 레지스터, 캐쉬에도 저장 (CPU랑 가깝지만 공간은 작음)

→ 단계별로 CPU가 확인

*SSD(10us), HDD(10ms) - 단위가 다른 저장매체에서 데이터를 가져오는 건 시간 오지게 걸림

*어셈블리어(Assembly언어), CPU에 가장 가까운, 유사한 기계어. 완전히 CPU가 동작하는 것처럼 구성

📌

PC

클럭이 튕길 때마다 1씩 증가하는 기능의 레지스터

Control Panel;

(Takeover 스위치 = 1) 순차적으로 특정 숫자를 써넣음 →

(Takeover 스위치 = 0) = 컨트롤 패널에서는 더이상 램 안에 있는 내부 부품을 제어하지 않음 →

PC의 clear 스위치(= 초기화 스위치)가 0이 되면(=pc값 초기화하고 주소값을 accumulator에 넣어주면 주소값에 숫자가 들어감 →

다음 클럭 튕김 →

pc값 1 증가 →

해당 주소값을 찾아서 다음 숫자가 들어감 →

어큐뮬레이터에서 해당 숫자를 더함

내가 원하는 위치에 순차적으로 더하고 싶은 숫자를 넣으면 회로 변경 없이 원하는 계산(accumulator)을 할 수 있다 !

*회로 변경 없이 원하는 데이터를 메모리에 순차적으로 기재하면 된다. (코드는 위에서부터 밑으로 실행됨)

📌

Programing

명령을 메모리에 넣고 CPU가 하나씩 그 명령을 수행하게끔만 하면 회로는 그대로 두고 우리는 명령만 다르게 짜서 원하는 기능을 수행하게끔 한다.

- Data , Code

- 메모리 공간 분리 (pc 주소값) - code 메모리, data 메모리(주소값) → 동일한 주소값에 접근하게 하는 명령 작성 → 해당 명령 cpu가 읽음

Ram 분리 → 명령 의미 값 순차적으로 → 코드 실행 가능

Load, Add, Store → cpu한테 명령 내림 → 기능에 대한 의미 값이 필요 (명령 의미 숫자를 만들고, 주소에 맞는 코드를 넣음)

명령 숫자 : Instruction Code, Operation Code → 또는 ‘opcode’

회로를 추가해 각각의 명령 대로 동작할 수 있게 구성한 CPU = intel CPU, ARM CPU 등 = opcode 제공

이를 기반으로 어셈블리어로 해당 CPU에서 명령 동작을 하게끔 프로그래밍 → 복잡 코드 작성 어려움

💡 그래서 !

내부적으로 컴파일을 통해 opcode로 변환, CPU에게 명령

→ 우리는 opcode를 몰라도 프로그램을 짤 수 있다.

= 현재의 Programing !!📌

Instruction Set, 코드(명령어+데이터)

- 고급언어 : 컴파일러 필요, C언어 Java 등

- 저급언어 : 인터프리터, 코드 자체 실행

*CPU 기본 실행 구조 ; 메모리에 주소 또는 인자들 포함 명령들을 주소마다 저장하고, PC를 해당 주소를 가리키게 하여 해당 과정을 거치면서 명령어로 실행함

-

Instruction Fetch, 메모리에서 읽은 명령어를 CPU로 가져옴

PC가 가리키는 주소를 MAR에 보냄 → 그 주소를 메모리에서 읽고 MBR에 보냄 → 다시 그걸 IR에 저장 → 다음 명령 가리키도록 PC 주소값 증가

-

Instruction Decode, IR에서 인출한 명령어의 해당 데이터 가져오고, 해독(OP 코드 해석)

-

Instruction Execution, 명령어 실행 MAR ACC(가산기)의 데이터를 연산 → ACC에 데이터 저장

-

Write Back, 출력된 실행 결과 메모리 등에 저장

📌

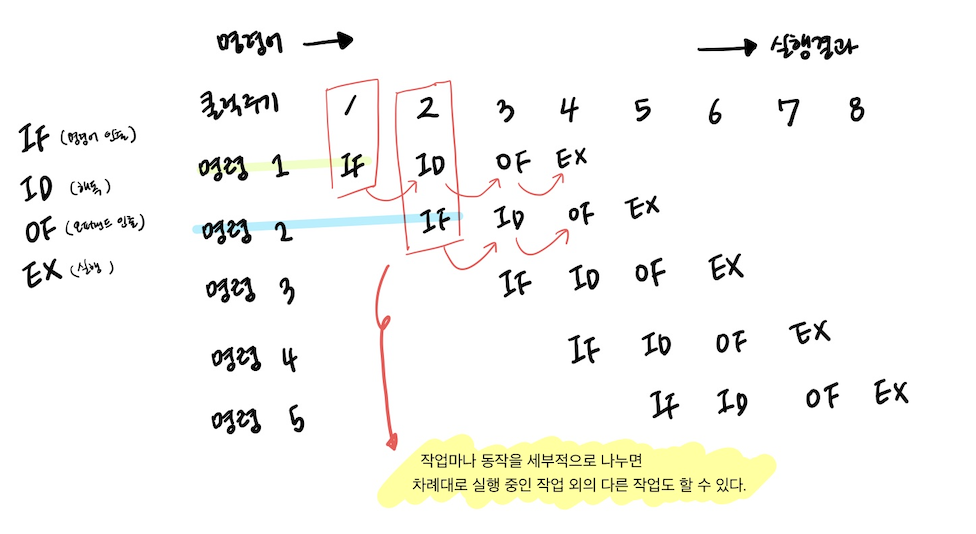

파이프 라인

하나의 작업에 필요한 일을 세부적으로 나누어서 동시에 다른 세부작업을 실행하는 기법

** 사이클 : 클럭이 한 번 튈 때, 5cycle = 5단계 16cycle = 16단계

📌

ARM, Intel

- ARM - RISC, 간단 명령어 조합 실행 → 코드가 길어짐 (Phone) -RISC ; 명령어 포맷과 길이 고정, 하나의 사이클로 실행, 시간 예측 가능, 임베디드 ARM스마트폰 IoT 기기

- Intel - CISC, 복합 명령어 → CPU 로직 복잡도 증가, 실행 시간 증가 (PC) -CISC ; 명령어 포맷과 길이 고정 x, 하나 이상의 사이클, 전체 명령이 얼마나 걸릴지 시간 예측 어려움, 인텔 CPU