시간표현과 상태기억II

- 게이트가 있는 래치

- 플립플롭

- 카운터

- 레지스터

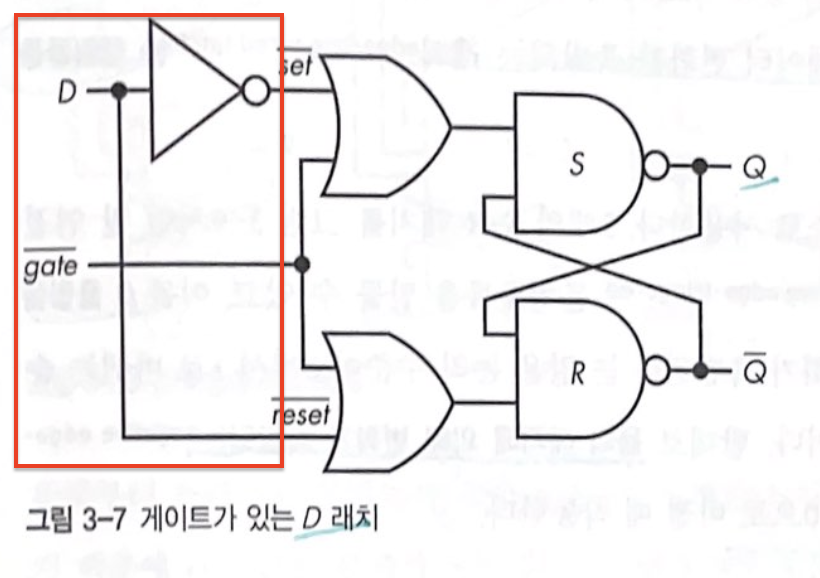

게이트가 있는 래치

로우 = 참 = 0

하이 = 거짓 = 1

어느 시점에서 데이터를 기억한다는 것을 배워 배워보자.

gate 입력이 거짓(하이 = 1)인 경우 set와 reset가 어떤 값이든 아무 관계가 없다.

1비트 정보를 유지하기 위해서 set와 reset을 같은 입력에 연결하면서 한쪽 입력에는 인버터를 추가하여 입력을 1비트만 받게 만들 수 있다.

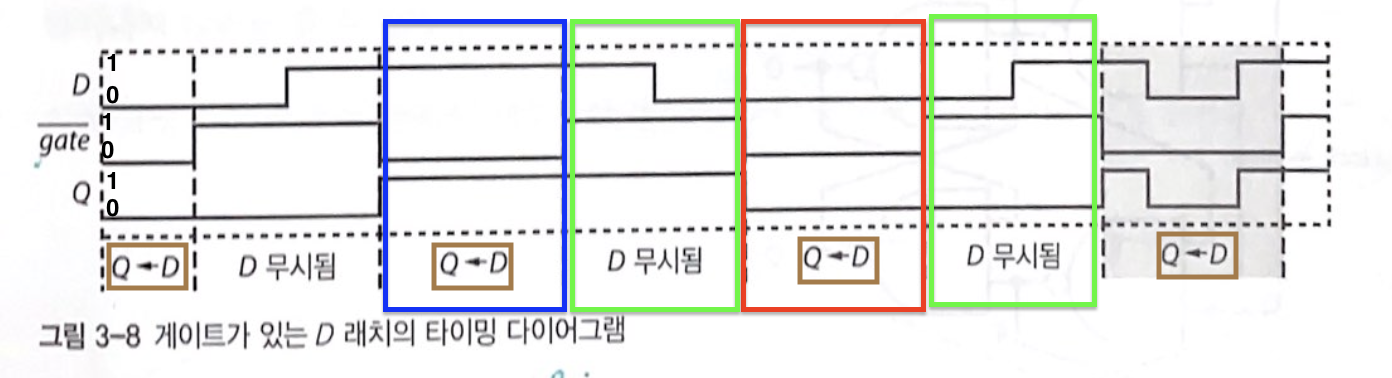

1. gate가 참(로우 = 0), D가 1 일때, Q출력은 1 (파랑색)

1. gate가 참(로우 = 0), D가 1 일때, Q출력은 1 (파랑색)

2. gate가 참(로우 = 0), D가 0 일때, Q출력은 0 (빨간색)

3. gate가 거짓(하이 = 1), D가 변해도, Q출력 변화없음. (초록색)

gate가 참인 상태에서 D의 변화가 그대로 출력되는 문제가 생겼다. (갈색)

이로 인해 게이트를 여는 시간을 최소화 해서 순간적으로 D의 상태에 맞춰 출력 상태를 변경할 수 있게 한다면 좋을 것이다.

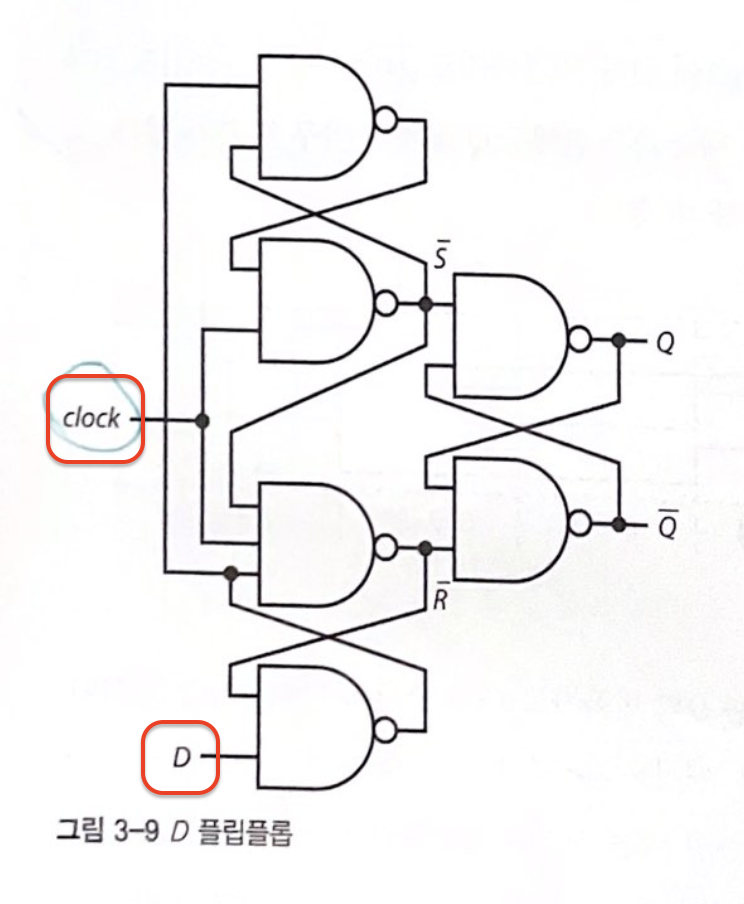

플립플롭

클럭 입력를 가지며 클럭 입력에 반응하여 출력상태를 바꾸는 기억소자라고 한다.

논리 수준(로우,하이)이 특정 값에 머무는 동안 데이터를 잡지 않고, 논리 수준이 한 수준에서 다른 수준으로 전의 되는 중간에 데이터를 잡아내는 것을 에지(edge)라고 한다.

에지에 의해 데이터 변화가 촉발되는 래치를 플립플롭이라고 한다.

(키포인트는 변경, 전이에 초점을 맞추어 보시면 될 것 같아요.)

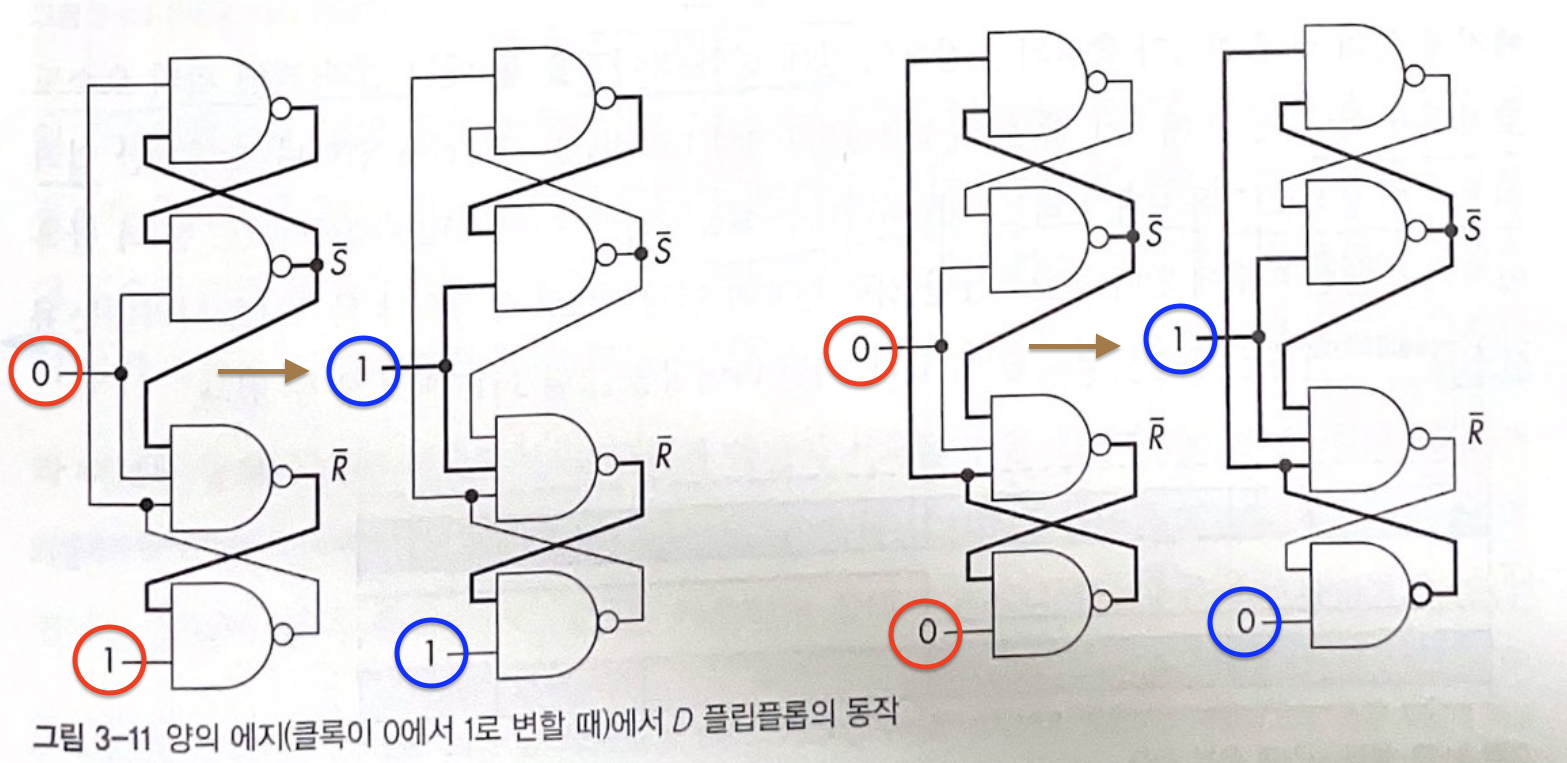

양의 에지에 의해 변화가 촉발되는 플립플론(D플립플롭)은 양의 에지구간에서 작동하고,

음의 에지에 의해 변화가 촉발되는 플립플론은 음의 에지구간에서 작동한다.

- D와 클럭에 때른 회로의 동작

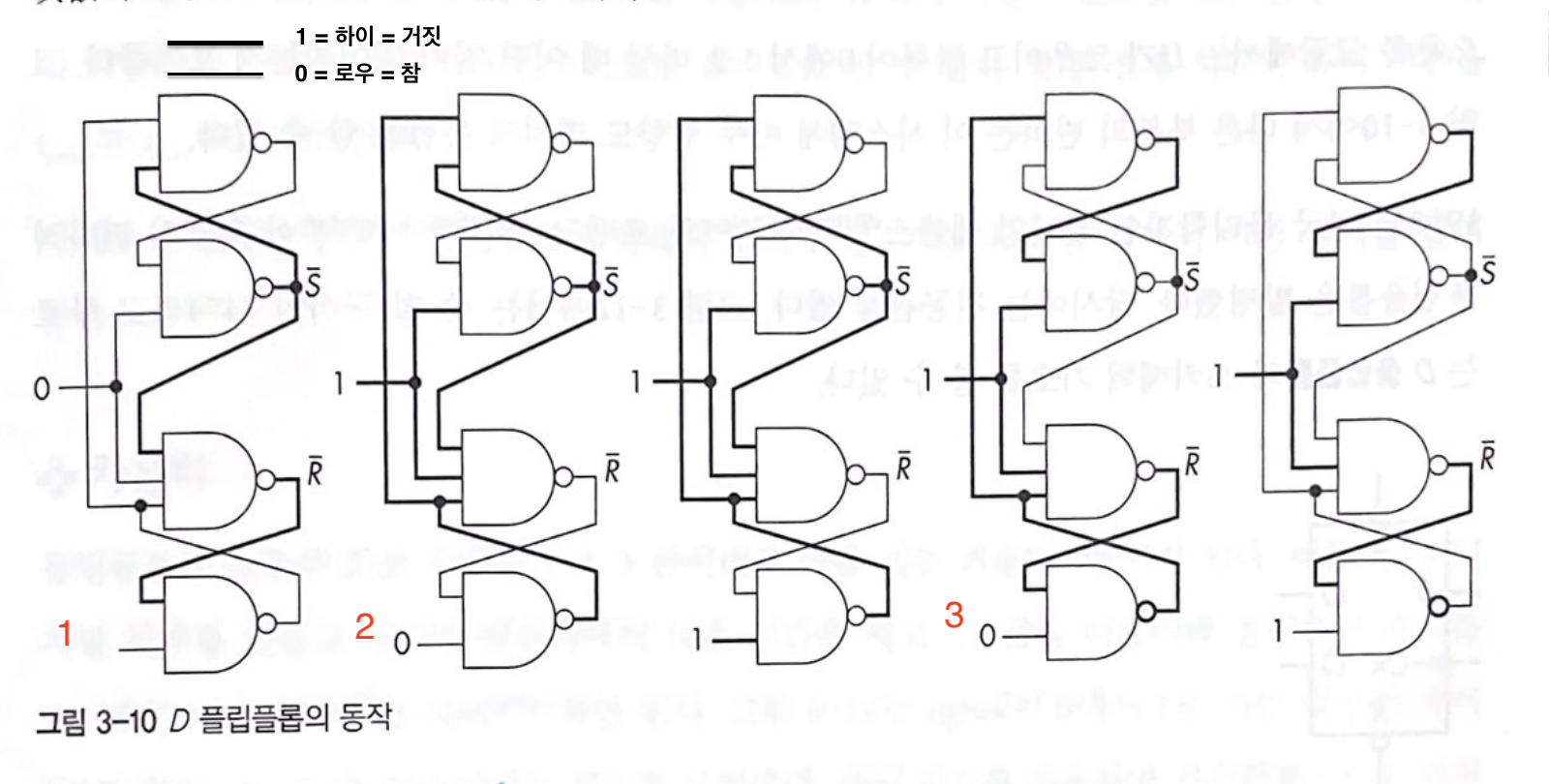

굵은 선은 논릿값이 1, 가는 선은 논릿값이 0

- 클록이 0S R 거짓(하이)이기 때문에 D의 값은 바뀌지 않음.

- R가 참인 경우 D의 값을 바꿔도 아무효과없음.

- S가 참(로우)인 경우 D를 바꿔도 변화 없음.

- 클록이 로우에서 하이로 바뀔때 회로의 모습

- 클록이 로우, D가 하이 일때, S R 거짓(하이)

클록이 1로 바뀌면 S가 로우로 변경 - 클록이 로우, D가 로우일때,

클록이 1로 바뀌면 R참(로우)로 변경

두 경우 모두플립플롭의 상태가 바뀐것을 볼수 있습니다.

- 클록이 로우, D가 하이 일때, S R 거짓(하이)

1918년 월리엄 에클스와 프랭크 조던이 최초의 전자석 플립플롭을 발명하였다.

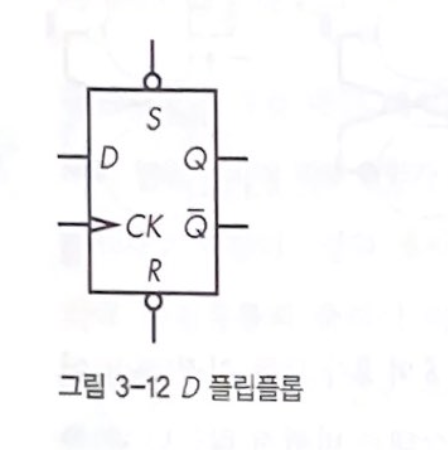

D플립플롭 스키매틱 기호

D플립플롭은 몇가지를 제외하고 S-R래치와 같다.

왼쪽의 D는 데이터(data)를 , CK는 클록(clock)를 뜻한다.

이 플립플롭은 양의 에지에 촉발되기 때문에 ck신호가 0에서1로 바뀌는 시점에 D입력 값이 저장된다.

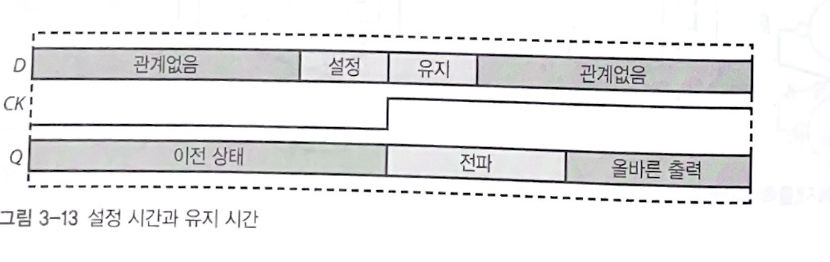

에지에 의해 상태 변화가 촉발되는 장치의 상태변화 타이밍을 볼때 전파지연, 설정시간, 유지시간을 고려해야한다.

- 설정시간 (tsetup) : 클록에너가지 발생하기 전 얼마동안 입력 신호가 안정적으로 유지 돼야 하는지를 나타낸다.

- 유지시간 (thold) : 클록에지가 발생한 이후 얼마나오랫동안 입력 신호가 안정적으로 유지돼야하는지를 나타낸다.

D를 보면 설정,유지시간을 제외하면 출력에 영향을 주지 않는 것을 볼수 있다.

D를 보면 설정,유지시간을 제외하면 출력에 영향을 주지 않는 것을 볼수 있다.

전파지연시간이 지나야 D입력과 무관하게 출력이 안정적으로 유지된다.

카운터

플립플롭을 응용한 회로로 1,2,3 순서대로 수를 셀 수 있다.

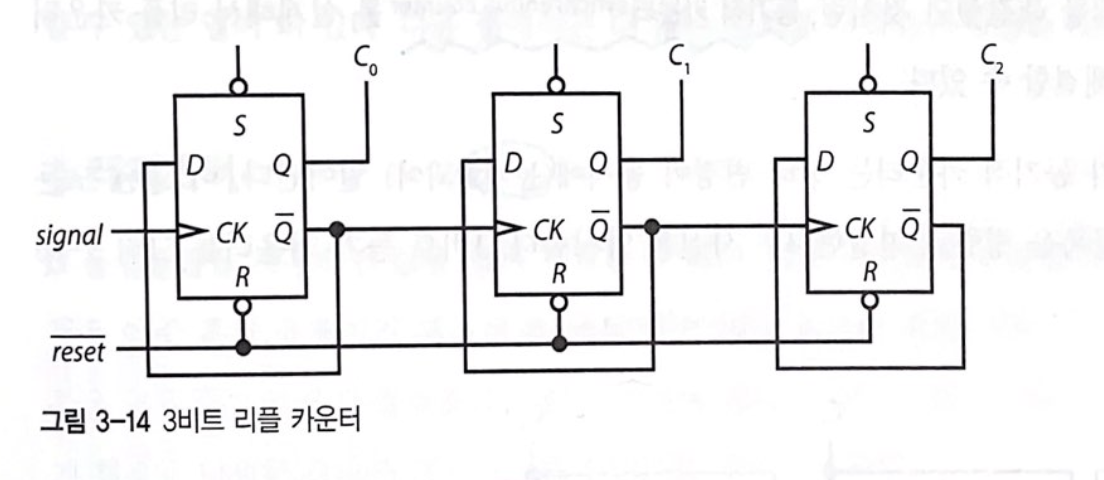

- 리플카운터

물결이 퍼저나가 듯이 결과가 왼쪽에서 오른쪽으로 퍼저나가는 동작을 보고 이름을 지음.

signal이 0에서 1로 가는 횟수를 세서 3비트수(c2,c1,c0)를 만들어 내는 회로이다.

signal이 0에서 1로 가는 횟수를 세서 3비트수(c2,c1,c0)를 만들어 내는 회로이다.

resert를 사용하면 카운터를 0으로 재설정 할 수 있다.

c0는 c1을 바꾸고, c1은 c2를 바꾸는 과정을 반복한다.

각 플립플롭은 자신의 CK신호가 0에서 1로 전이 될때마다 상태가 바뀐다.

각 비트의 상태가 다른 비트의 상태변화에 시차를 두고 있어 이 회로를 비동기 카운터라고 한다.

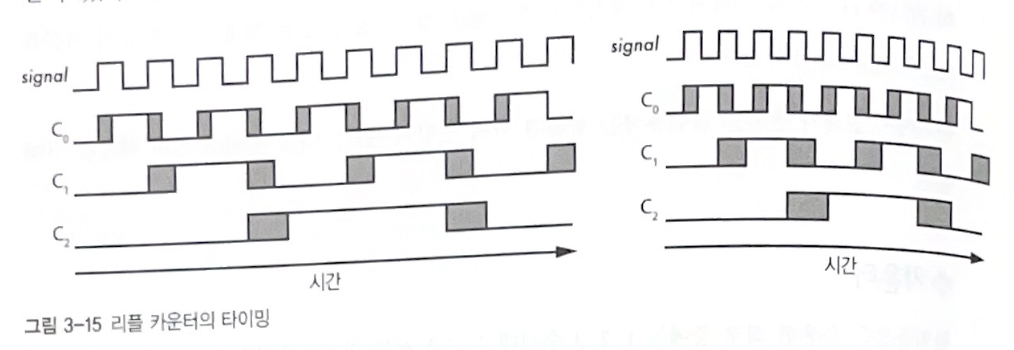

타이밍다이어그램

c0 ~ c2 뒤로 갈 수록 결과를 얻는데 오랜시간이 걸린다.

회색영역: 전파지연왼쪽은 전파지연을 제대로 감안해 3비트 수를 세는 경우.

오른쪽은 전파지연이 허용하는 것보다 더 빠른 속도의 입력 변화.

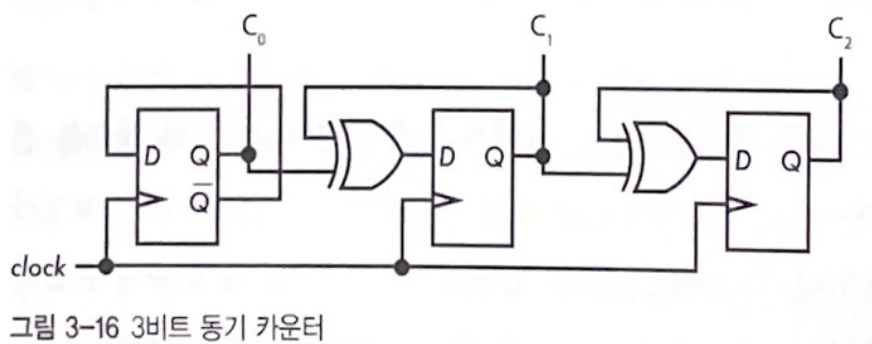

- 동기적카운터

동기적 카운터를 사용하여 리플카운터의 타이밍 문제를 해결 할 수 있다. 모든 플립플롭에 같은 클록을 병렬로 연결한것.

모든 플립플롭에 같은 클록을 병렬로 연결한것.

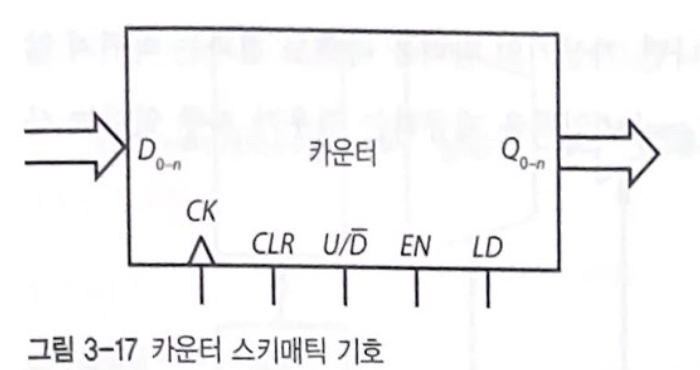

카운터를 더 큰 회로를 만드는 기본 기능 요소로 사용할 수 있다.

CLR : 카운터를 0으로 되돌리는 것.

EN : 카운터 활성화 시키는 것.

U/D : 양방향으로 수를 세는 것.

LD : D0-n과 카운터를 데이터 입력에지정한 값으로 설정

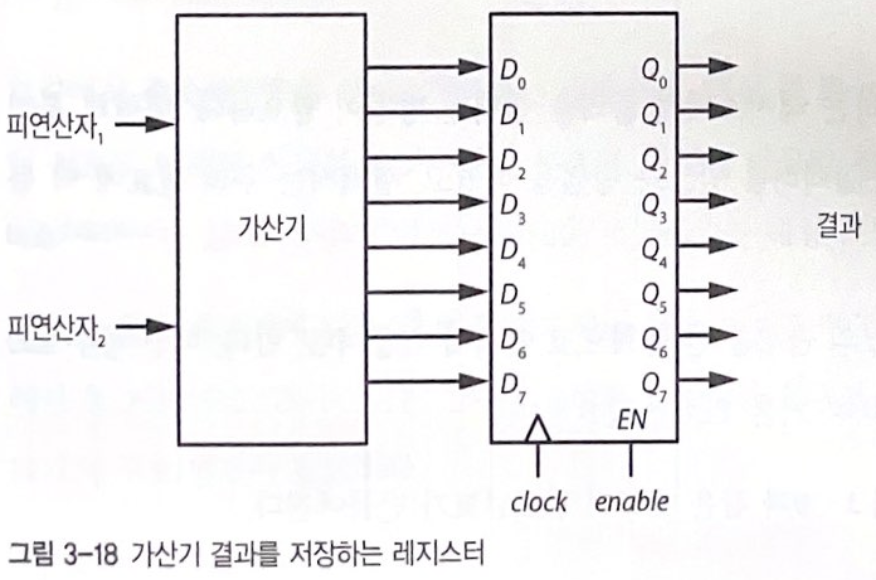

레지스터

레지스터는 클럭을 공유하는 여러 D플립플롭을 한 패키지에 넣은것이다.

가산기 출력을 클록을 사용해 레지스터에 넣고 나면, 가산기의 입력을 바꿔도 결과는 바뀌지 않는다.

레지스터도 카운터에서 봤던 것과 비슷한 enable 입력을 제공하는 경우가 자주 있다.