Cortex-M Processors - Memory Systems

임베디드시스템설계

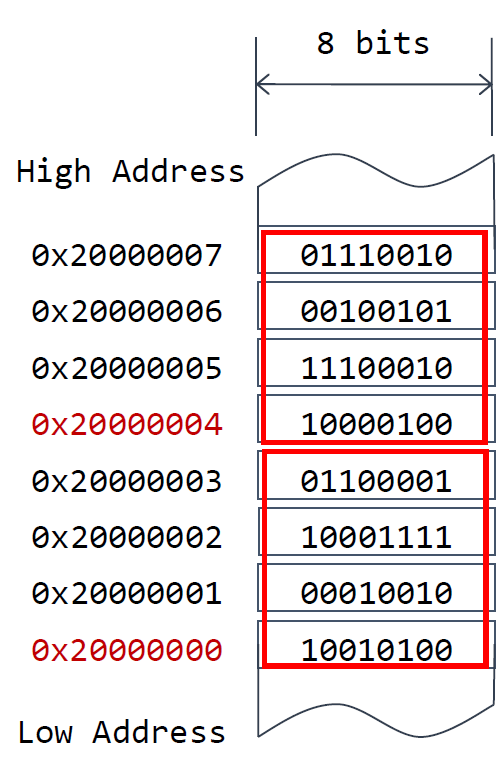

Logic View of Memory

- 8 bits = 1 byte

- 16 bits = 2 bytes = 1 halfword

- 32 bits = 4 bytes = 1 word

software 관점에서 memory는 addressable한 bytes의 array이다 (8 bit 단위).

만약 memory를 word 단위로 본다면 4 bytes 단위가 된다. word address는 그 word의 4 bytes중 가장 작은 address이다.

만약 memory를 word 단위로 본다면 4 bytes 단위가 된다. word address는 그 word의 4 bytes중 가장 작은 address이다.

위의 경우 word address는 0x20000000, 0x20000004이다.

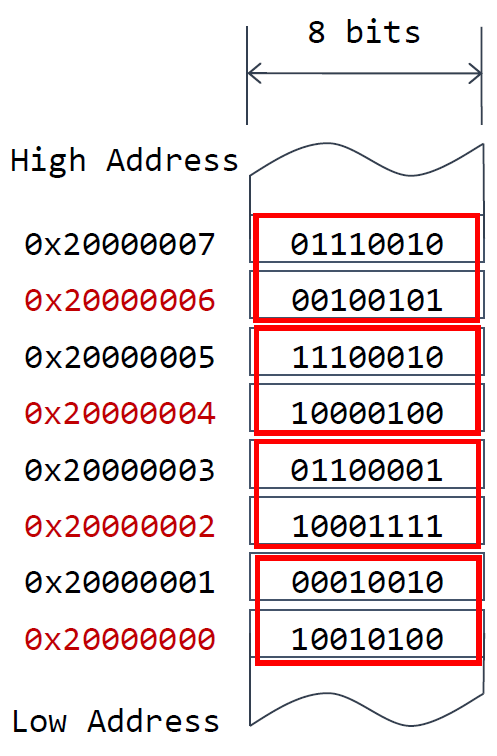

만약 memory를 halfword 단위로 본다면 2 bytes 단위가 된다. halfword address는 word address와 동일하게 그 halfword의 2 bytes중 가장 작은 address이다.

만약 memory를 halfword 단위로 본다면 2 bytes 단위가 된다. halfword address는 word address와 동일하게 그 halfword의 2 bytes중 가장 작은 address이다.

위의 경우 word address는 0x20000000, 0x20000002, 0x20000004, 0x20000006이다.

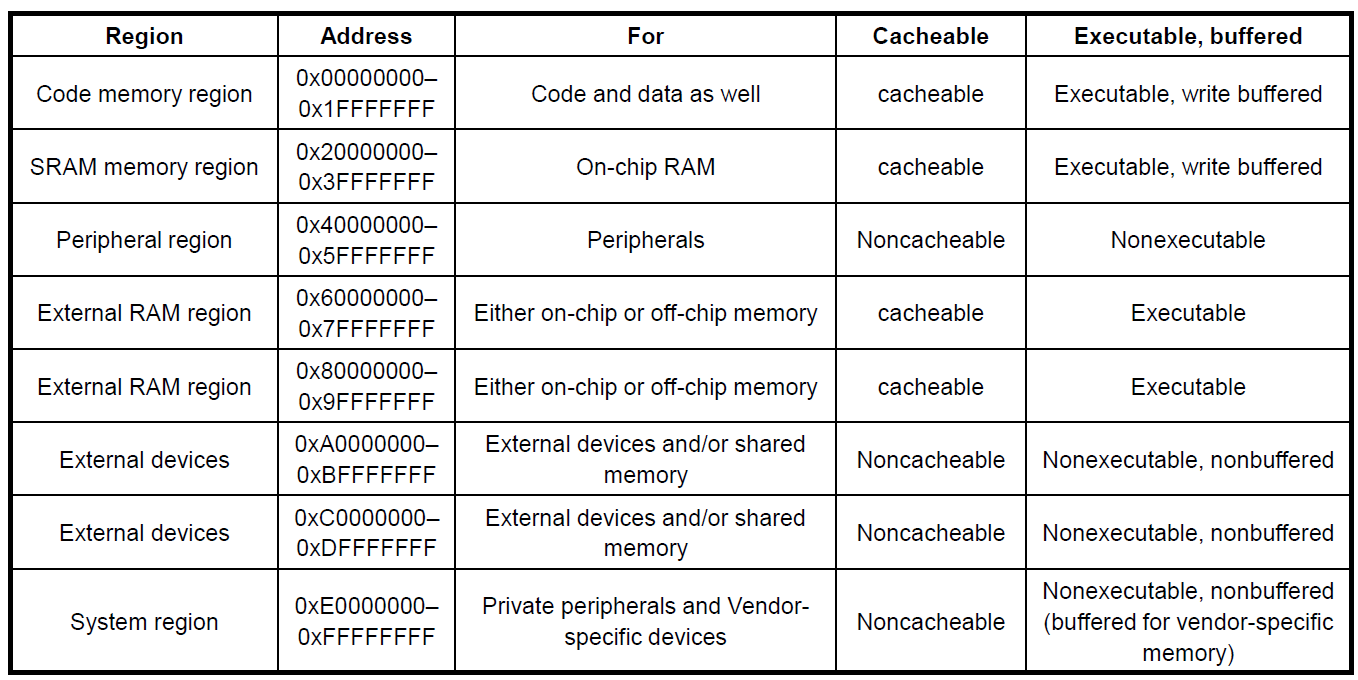

Memory Map

Cortex-M3 프로세서는 4 GB의 addres space를 가지고 있다.

또한 Cortex-M3 프로세서는 fixed memory map을 가지고 있다. fixed memory map이기 때문에 Cortex-M3 product는 NVIC와 MPU가 모두 동일한 memory location을 갖고 있어서 그들 사이의 software porting이 쉽다고 함.

거의 모든 하드웨어가 address를 부여받고 그 address를 통해 하드웨어에 접근할 수 있음.

Memory Access Attributes

memory map은 각 memory block이나 device에 접근할 때의 memory attribute를 정의한다. Cortex-M3 프로세서는 default memory attribute setting을 가지고 있지만 overridden될 수 있다 (MPU와 관련 있음).

- Bufferable : 프로세서가 다음 instruction 실행을 계속하는 동안 write buffer를 통해 memory write를 수행할 수 있다. 모든 memory write가 write buffer로 수행됨.

- Cacheable : memory read를 통해 얻어진 data가 memory cache에 copy돼서 다음 번에 그 값을 cache로부터 얻어 프로그램 실행 속도를 높일 수 있다. memory access가 cache를 통해 이루어질 수 있음.

- Executable : 프로세서가 이 memory region의 코드를 fetch해서 execute할 수 있다. memory에 올린 프로그램이 실행되는건 그 memory region이 executable하기 때문임.

- Sharable : 이 memory region의 data는 여러 bus master에 의해 공유될 수 있다. memory system은 bus master와 sharable data region의 coherency를 보장해야 한다.

bus master은 memory transcation이 가능하게 하는 하드웨어 component임. master만 transaction을 발생시킬 수 있음.

peripheral과 device와 관련된 부분은 실행할 수 없음.

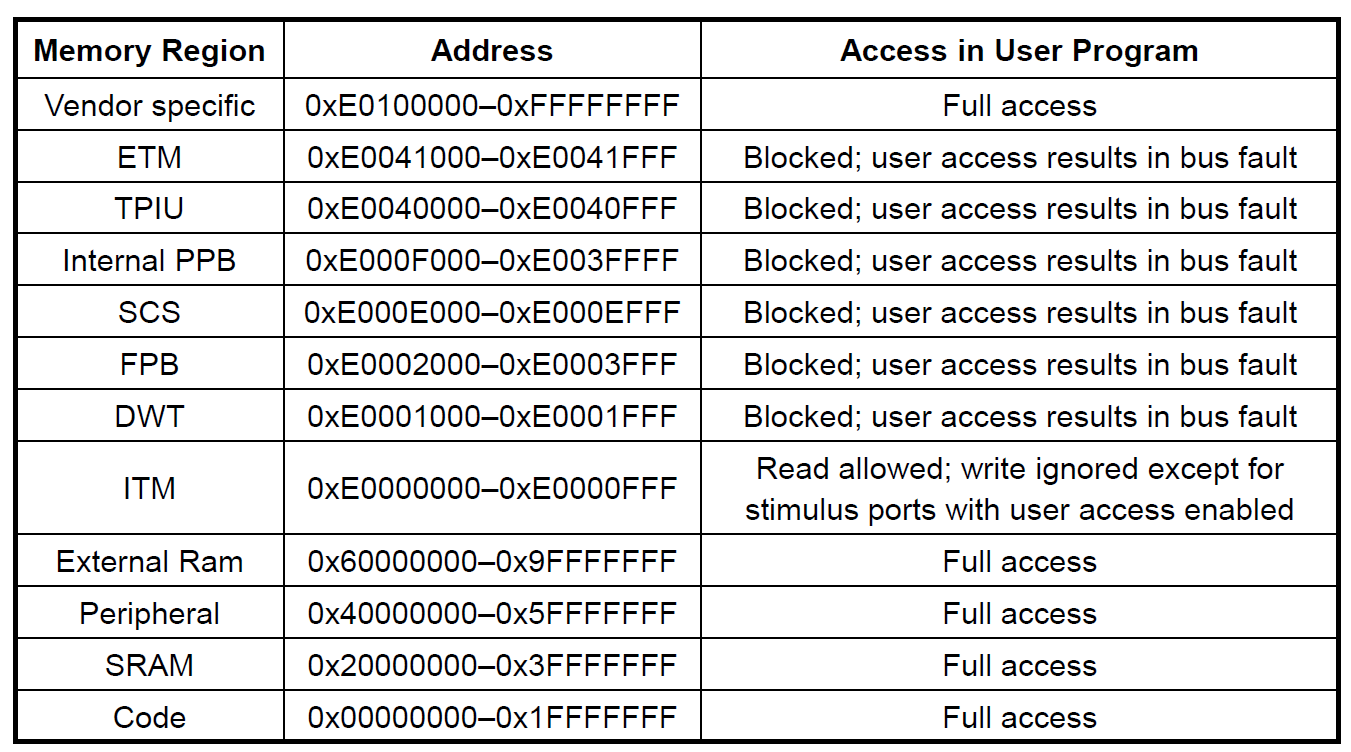

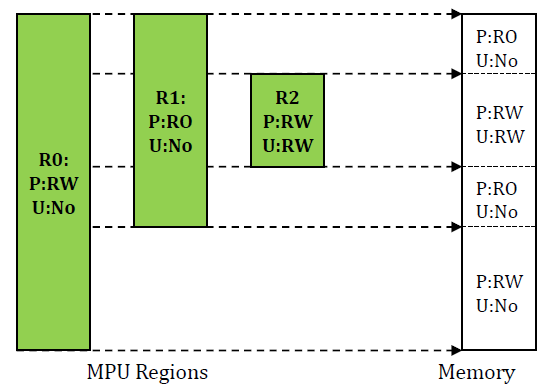

Default Memory Access Permissions

Cortex-M3 memory map은 memory access permission을 위한 default configuration이 있다.

default memory access permission은 다음과 같은 경우에 사용된다.

- No

MPUis presentMPUis present but disabled

위의 경우가 아니라면 MPU가 memory access가 allow됐는지 결정한다.

만약 접근하려는 memory region의 memory access가 block되어 있다면 fault exception이 즉시 발생한다.

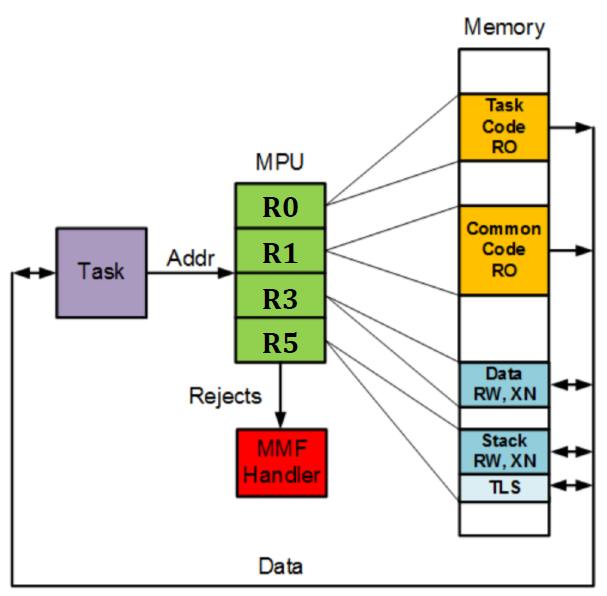

MPU (Memory Protection Unit)

MPU는 memory와 I/O access가 허용되었는지 확인할 수 있는 기능을 제공한다.

8~16개의 개별적인 memory region을 지원하고 각 region은 fetch, read, write permission의 combination으로 이루어져 있다. 또란 access attribute도 지정할 수 있음..

만약 허용되지 않은 access라면 trap(exception)이 발생한다 (MMF, memory management fault).

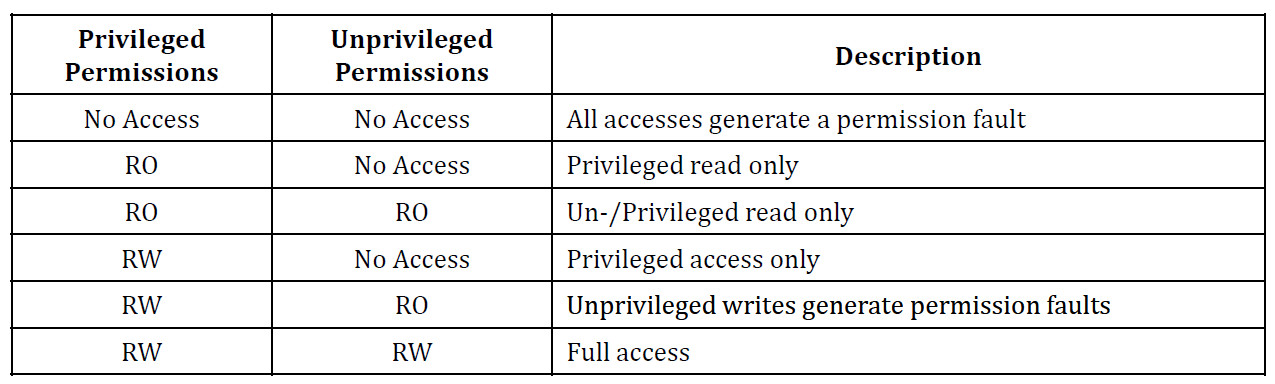

MPU는 privileged/unprivileged memory access permission의 combination이다.

MPU region은 중복될 수 있다 (ARMv7 only).

memory region이 overlap되면 memory access는 highest number를 가진 region의 attribute에 영향을 받는다.

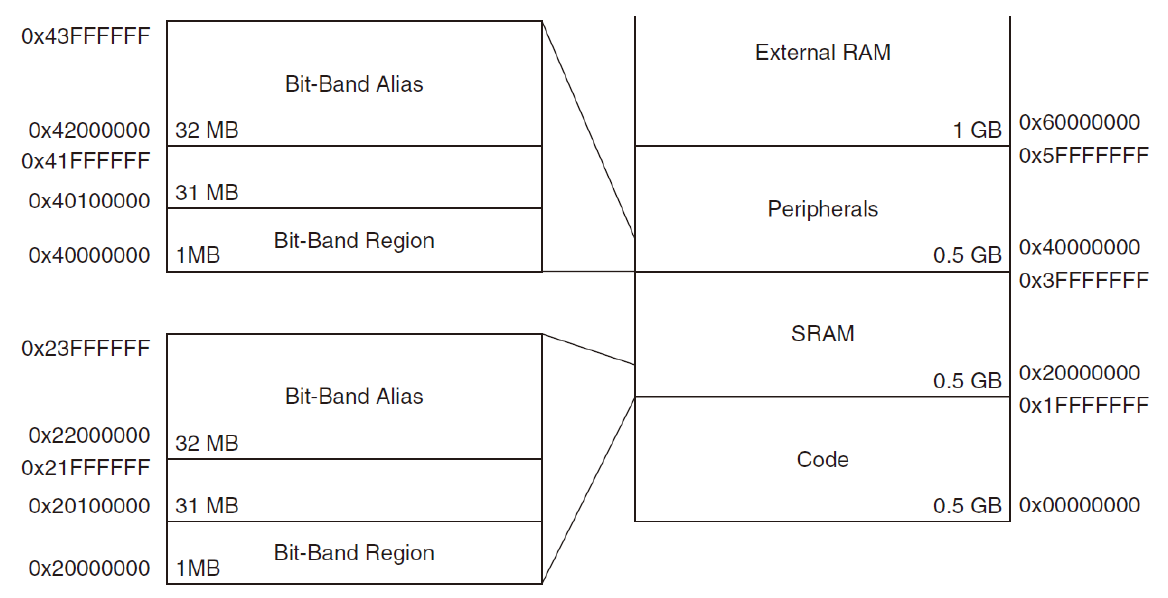

Bit-Banding

bit-band operation은 single data bit에 접근하는 single load/store operation을 지원한다.

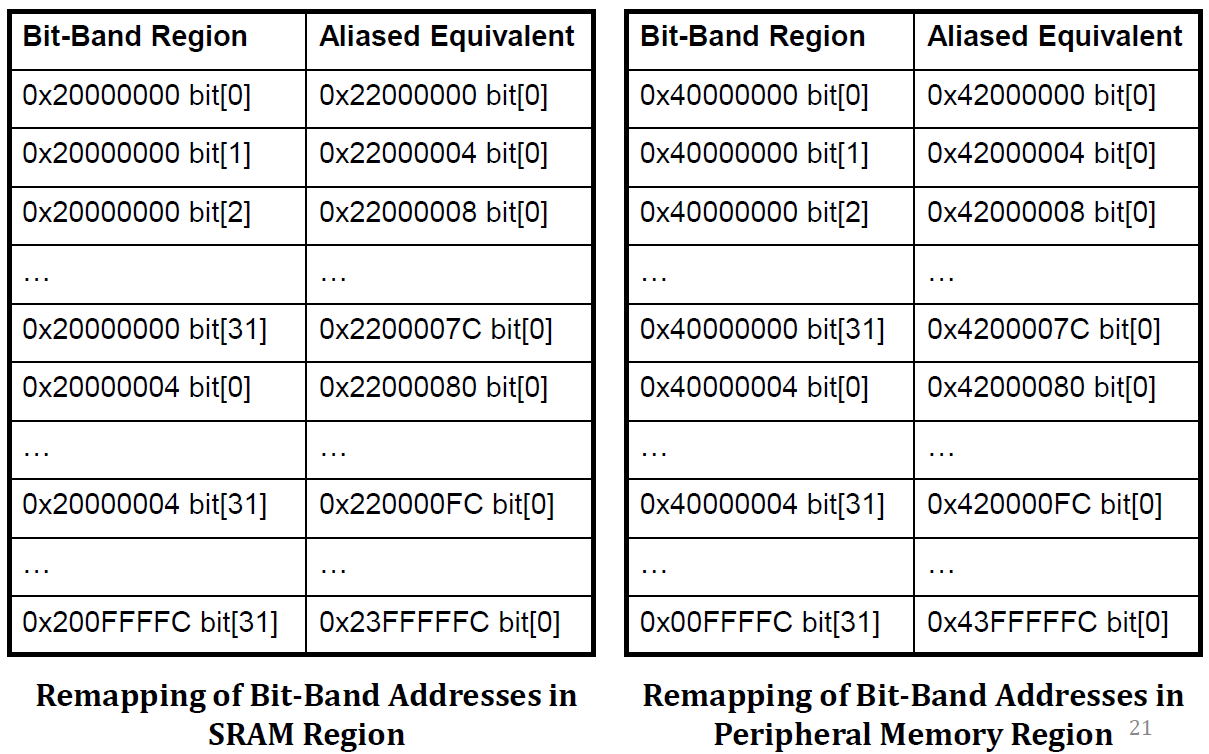

bit-band region은 다음과 같다.

SRAMregion의 첫 번째 1 MB- peripheral region의 첫 번째 1 MB

이 영역들은 bit-band alias라고 불리는 분리된 memory region을 통해 access될 수 있다.

bit banding은 bus matrix를 통해 수행된다.

https://todayis.tistory.com/254 참고.

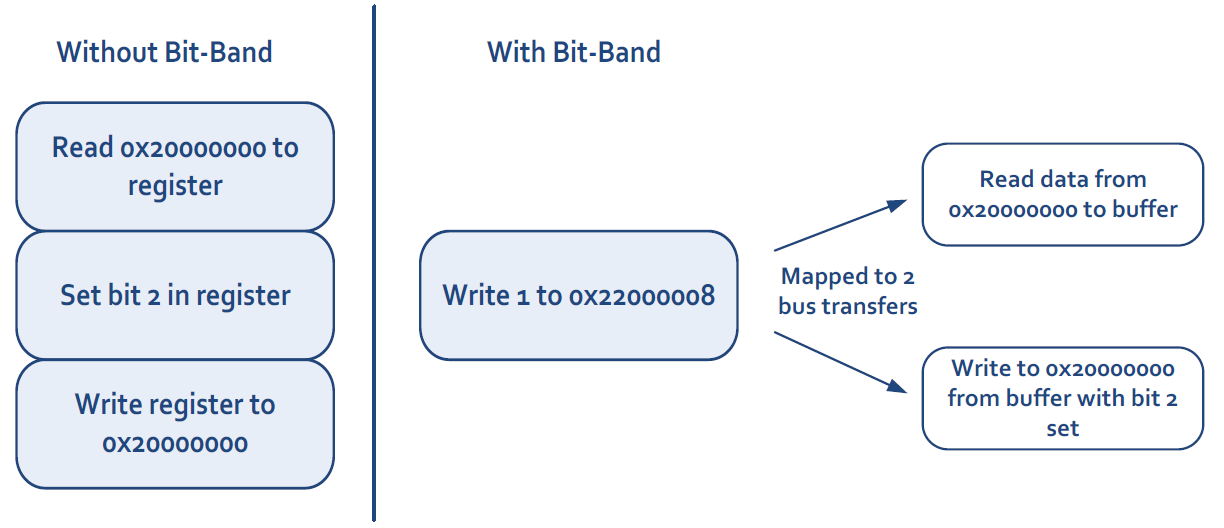

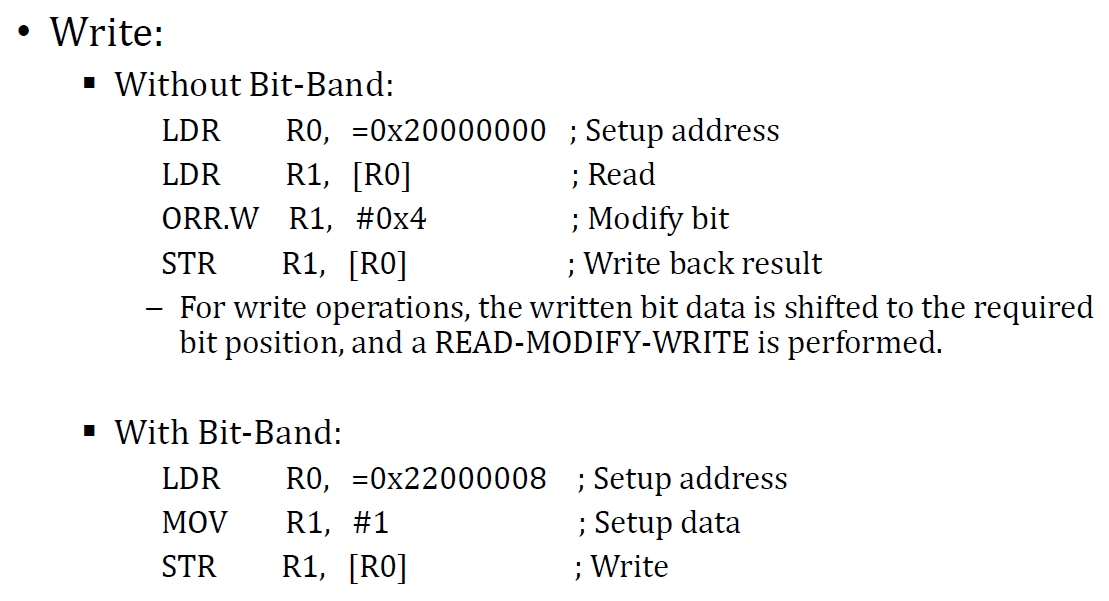

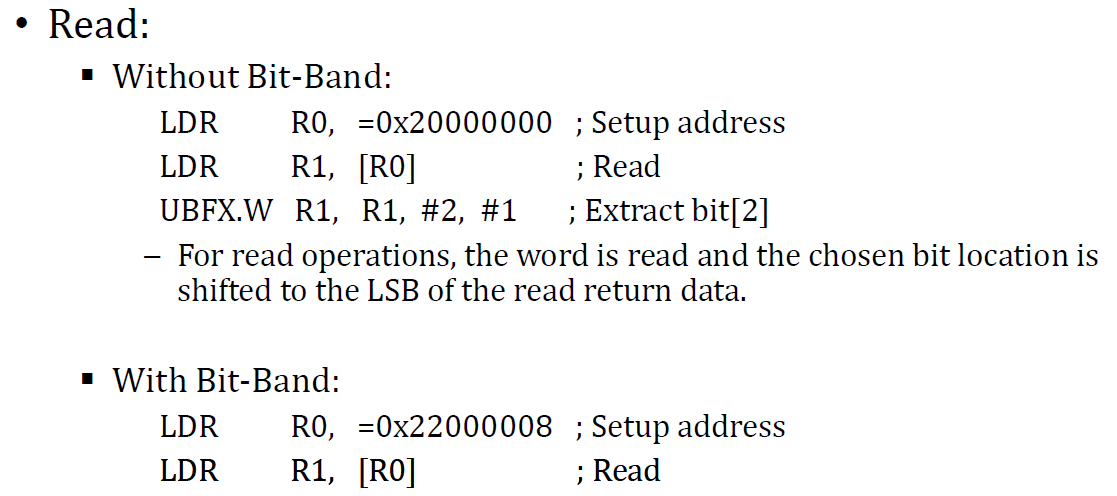

1. Write

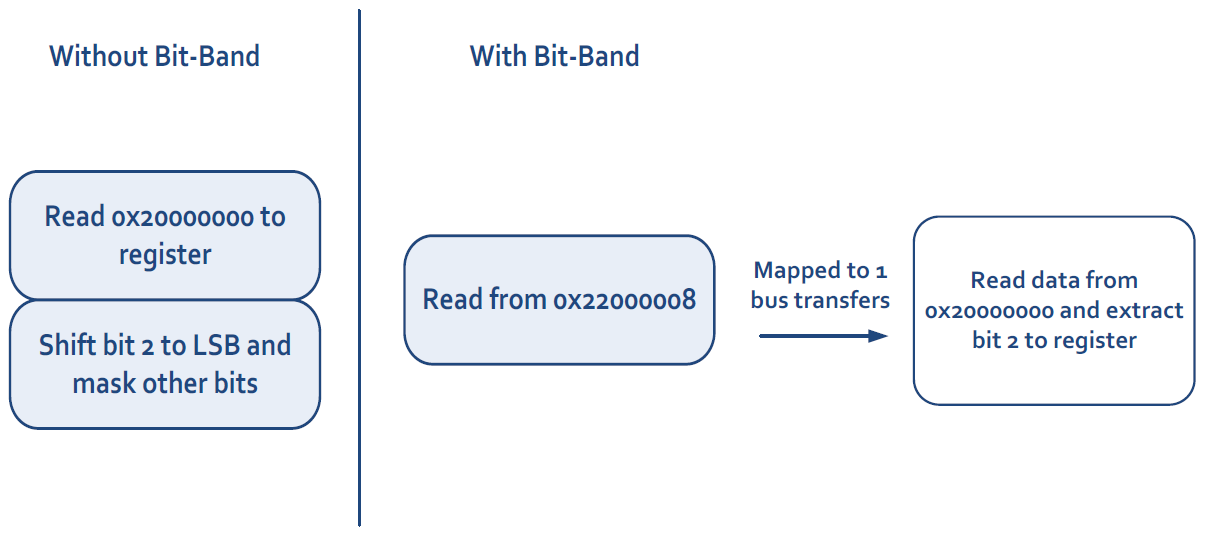

2. Read

사용하는 instruction의 수를 줄여서 bit operation을 더 빠르게 수행할 수 있다.

hardware를 통한 수 많은 read/write operation을 줄일 수 있음.

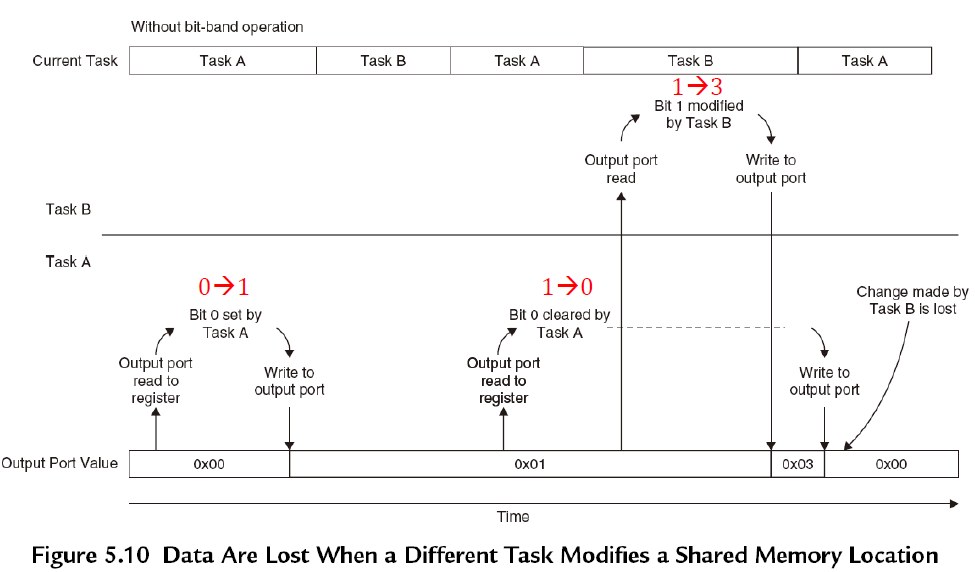

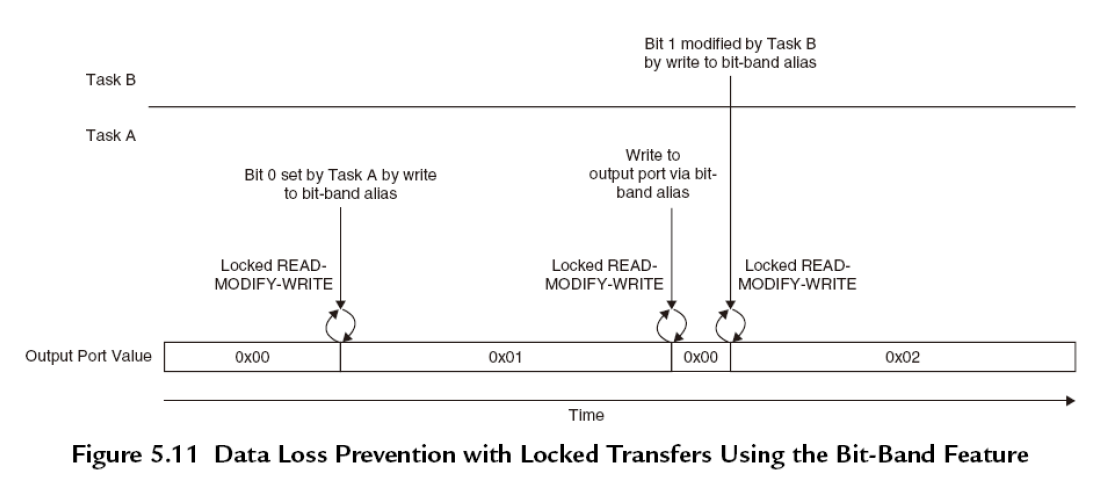

그리고 bit-band operation을 통한 read/write을 할 때에는 lock이 걸리기 때문에 shared memory location의 data가 손실되거나 하지 않는다.

1을 0으로 만들고 싶었던건데 의도치않게 interrupt handler에 의해 3으로 바뀐걸 0으로 바꿔버림.. race condition.

이런 현상을 피하기 위해 single instruction으로 bit operation을 실행시키고자 하는 것임. bit-band operation을 사용하면 single instruction으로 bit operaion을 실행할 수 있음.

C에서는 bit-band operation이 native하게 지원되지 않으므로 이를 따로 정의해주어야 한다. bit-band operation을 쓰면 C compiler가 이를 인식하지 못함... 그래서 bit-band operation을 쓰고 싶으면 추가적인 코드를 사용해야함.

가장 쉬운 방법은 bit-band region을 pointer로 사용하는 것이다. 그럼 single write로 bit-band를 구현할 수 있다.

Miscellaneous Features

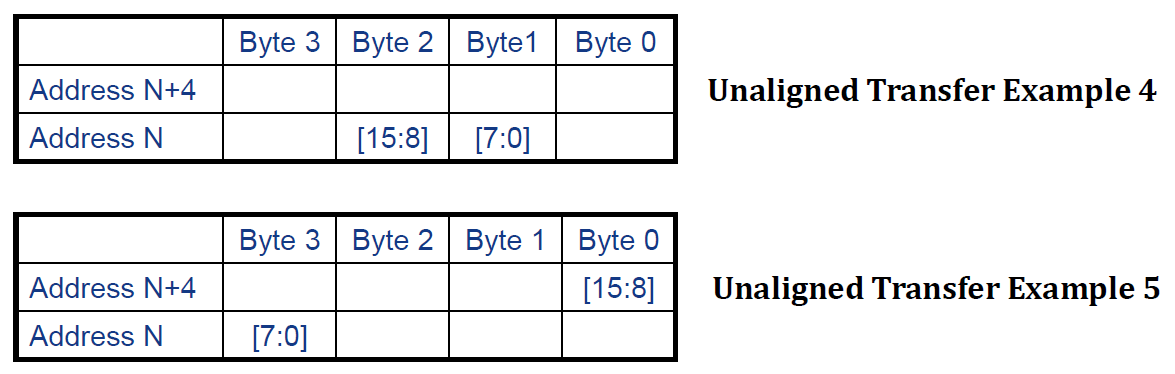

Unaligned Transfers

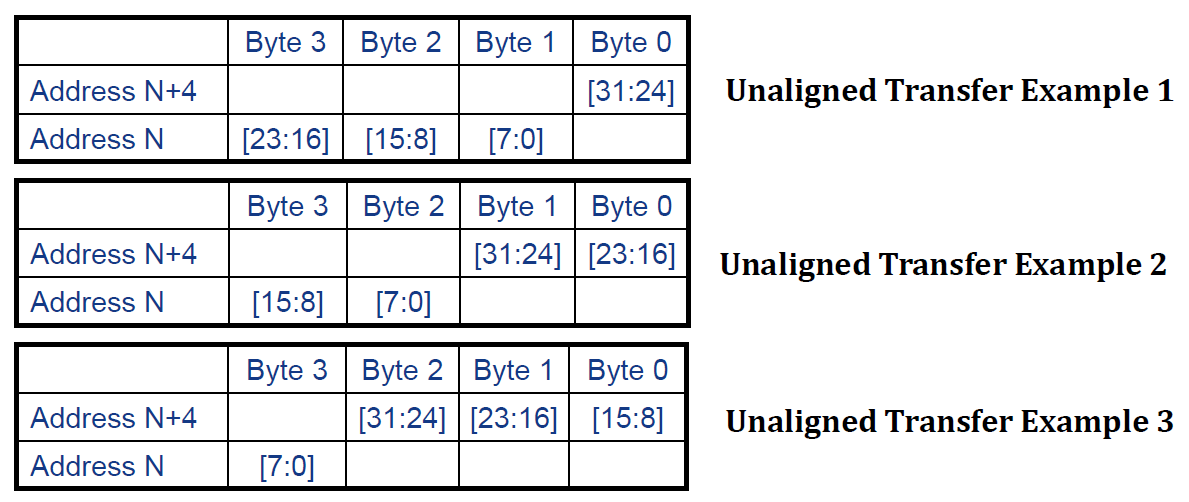

Cortex-M3은 single access에서의 unaligned transfer를 지원한다.

data memory access는 aligned/unaligned 으로 정의될 수 있다.

unaligned transfer인 경우

1. Word size인데 address가 4배수가 아닌 경우

2. Halfword size인데 address가 2배수가 아닌 경우

unaligned transfer는 load/store multiple instruction을 지원하지 않고 stack operation(push/pop)은 무조건 align으로 사용해야 한다. 또한 exclusive access는 align된 상태로 접근되어야 하고 unaligned transfer는 bit-band operation을 지원하지 않는다.

unaligned transfer는 여러 개의 aligned transfer로 변환되어 사용된다. 따라서 single data access에 더 많은 clock cycle을 소모하게 된다.

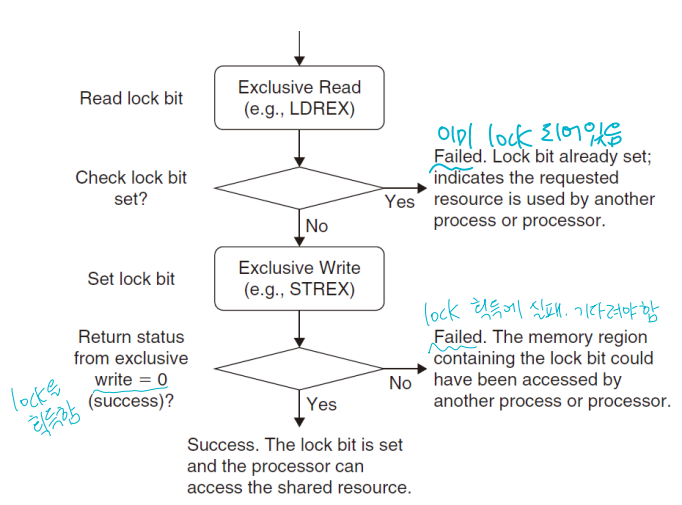

Exclusive Accesses (LDREX, STREX)

task와 handler가 안전하게 자원을 공유하기 위해서 보통 lock이 사용된다. race condition을 피하기 위한 것임.ㄴ

자원을 사용하기 전에 그 자원을 사용하기 위한 lock을 획득해야 한다. 그리고 그 자원의 사용이 끝나면 lock을 release 해야한다.

exclusive access instruction은 hardware resource를 사용할 수 있는지 확인할 수 있다.

LDREX(word), LDREXB(byte), LDREXH(halfword), STREX(word), STREXB(byte), STREXH(halfword)가 있다.

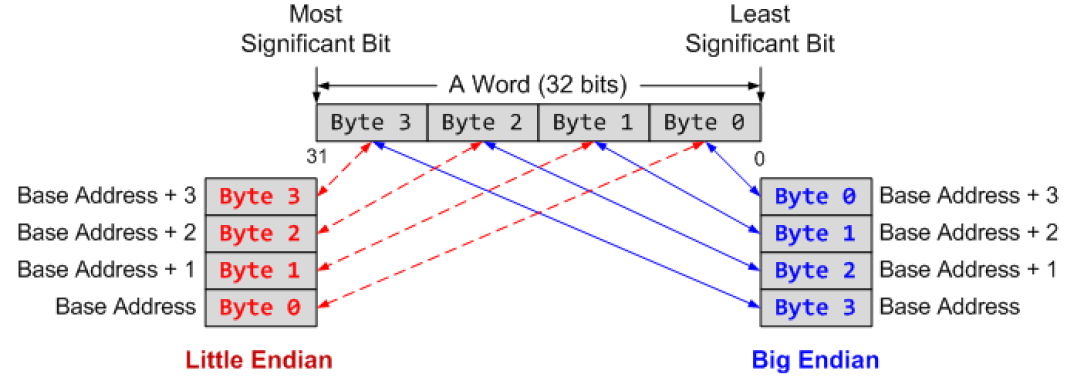

Endian Mode

Cortex-M3은 little endian(recommended)과 big endian을 모두 지원한다.

하지만 지원되는 memory type은 microcontroller의 design에 따라 다르다.

endian mode는 processor가 reset을 exit할 때 정해지며 그 이후로는 바뀌지 않는다.

endian mode는 processor가 reset을 exit할 때 정해지며 그 이후로는 바뀌지 않는다.

instruction fetch는 항상 little endian으로 수행된다.

REV/REVH를 사용하면 data를 little endian과 big endian으로 쉽게 변환할 수 있다.