Paged Virtual Memory & Context Switching Introduction

CR3 CPU 레지스터는 컨텍스트 전환 처리에 중요하다.

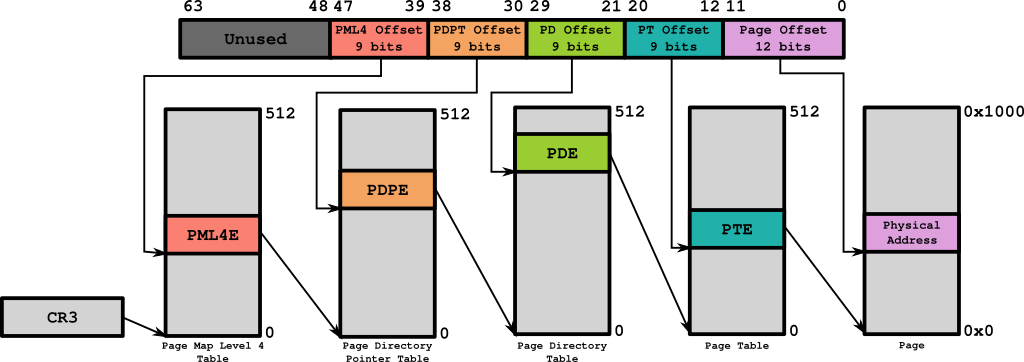

CR3 레지스터는 현재 프로세스에 대한 PML4(페이지 맵 레벨 4) 테이블의 기본 주소를 포함하도록 업데이트 된다.

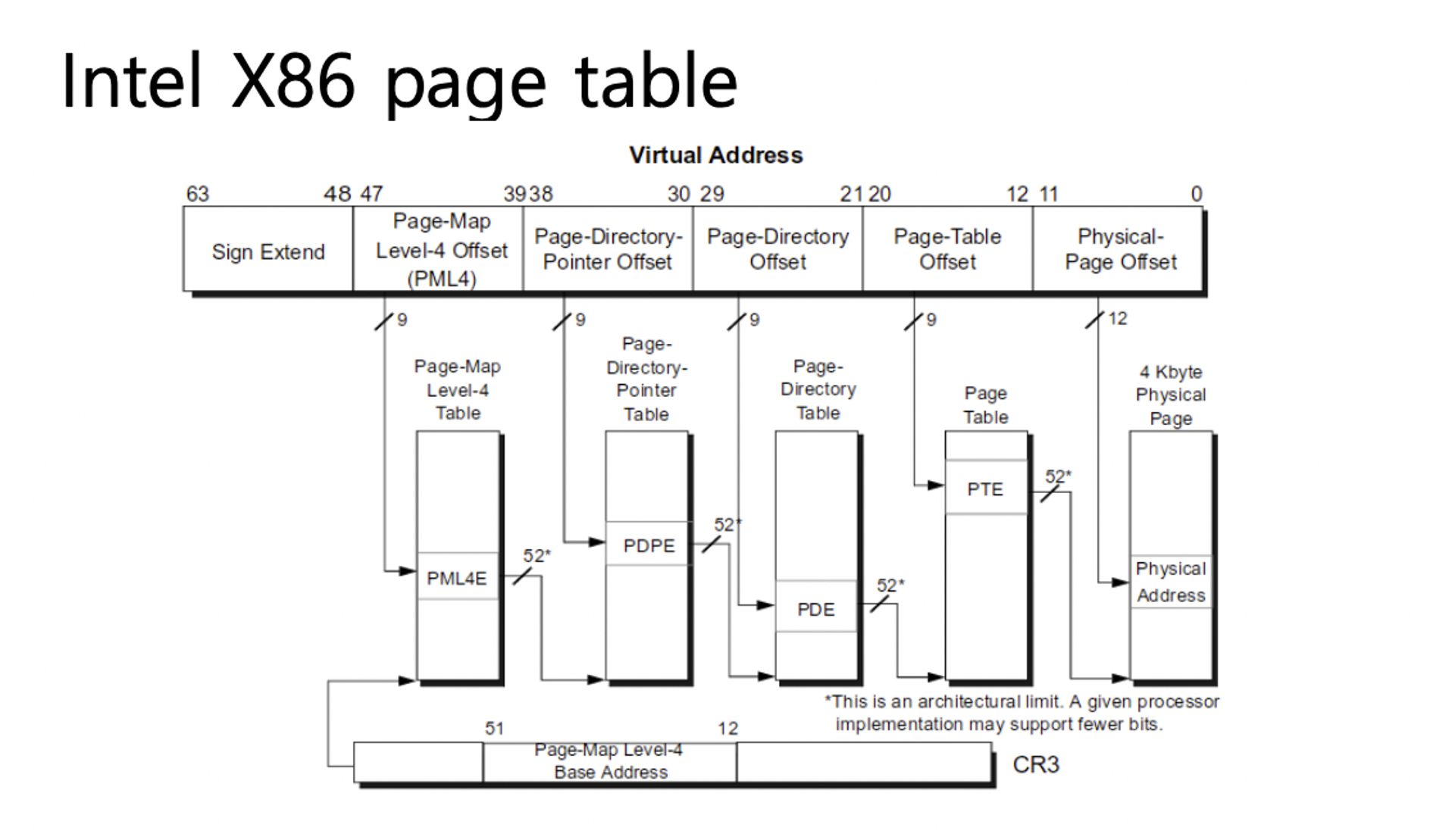

PML4 테이블은 MMU(메모리 관리 장치)가 가상 메모리 주소를 물리적 메모리 주소로 확인하는 데 사용하는 일련의 테이블 중 첫 번째 테이블이다.

각 프로세스가 자체 페이지 테이블 시리즈를 포함하는 자체 가상 메모리 공간을 가지고 있으며 CR3 레지스터가 PML4 테이블의 기본을 가리킨다는 점을 이해하는 것이 중요하다.

32비트 컴퓨터에서는 페이지 테이블이 딱 2단계만 있으면 충분했다. 각 페이지 테이블의 크기 자체도 페이지 하나의 크기를 가져야 하는데, 주소값 자료의 크기(포인터의 크기) = 4Byte(2²)인 32비트 컴퓨터에서 하나의 페이지 테이블에 들어갈 수 있는 엔트리의 개수는 1024개(2¹⁰)이다.

-> 페이지 하나의 크기가 4KB라는 것을 생각해보면 알 수 있음(2²*2¹⁰ = 2¹²)

상위 페이지 테이블인 Page-Directory는 1024개 엔트리를 가질 수 있고, 각 엔트리는 하위 페이지 테이블의 시작주소를 담고있다. 하위 페이지 테이블인 Page-Table 또한 1024개의 PTE를 가질 수 있다. 그렇다면 총 가능한 PTE의 개수가 2²⁰개가 되고, 이 PTE에 해당하는 페이지 안에서의 오프셋 또한 페이지의 바이트 크기(4KB=2¹²)만큼 가능하기 때문에 결국 가능한 주소의 개수는 2²⁰*2¹²=2³²개가 된다.

하지만 64비트 컴퓨터의 등장으로 페이지 테이블 개수가 증가할 수 밖에 없었다. 이 중 48비트만 사용한닥 해도 페이지 테이블이 4단계의 구성을 지녀야 한다. 이유는, bit의 개수 자체도 늘었을 뿐만 아니라 64비트에서는 주소값 자료의 크기가 8Byte(2³)이므로 페이지 테이블 당 엔트리 개수가(2⁹, 2³*2⁹ = 2¹²)로 줄어들기 때문이다. 결국 4단계 페이지 테이블 구성을 통해 총 가능한 PTE의 개수가 2⁹*2⁹*2⁹*2⁹=2³⁶개가 되고, 페이지 오프셋 개수 2¹²를 곱해주면 가능한 주소의 개수는 정확히 2³⁶*2¹²=2⁴⁸개가 된다.

그래서 4단계의 페이지 테이블 구성을 통해 64비트 컴퓨터의 가상 주소가 동작한다.

페이지 테이블 유형

4가지 페이징 모드

- 32비트 페이징

- PAE(물리적 주소 확장) 페이징

- 4단계 페이징

- 5단계 페이징

pintOS project 3. 가상 메모리에 본격적으로 들어가기 앞서 나는 64비트 프로세서를 사용한 4레벨 페이징에 중점을 둘 것이다.

4단계 페이징 개요

네 가지 레벨의 페이지 테이블이 사용된다.

각 페이지 테이블에는 512개의 항목이 있다. 인텔 메뉴얼에 딸면 4레벨 페이징은 48비트 주소를 사용한다. 따라서 4096바이트(4kb) 페이지가 있는 경우 각 프로세스에서 참조하는 최대 2^36(2^48 / 2^12)개의 페이지 테이블 항목이 있을 수 있다. 4개 수준 모두에서 각 페이지 테이블 유형은 우리가 보게 될 것과 매우 유사한 구조를 가지고 있다.

페이지 테이블의 네 가지 유형은 아래와 같다.

- page-map-level-4 table (PML4T)

- page-directory-pointer table (PDPT)

- page-directory table (PDT)

- page table (PT)

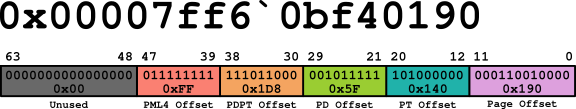

가상 주소

각 페이지 테이블 구조 오프셋의 길이는 9비트이다.

이는 오프셋 값이 0을 이진수로 최소 000000000, 511을 이진수로 최대 111111111 일 수 있음을 의미한다. 이는 각 페이지 테이블 구조에 최대 512개의 항목이 포함될 수 있다는 것을 의미한다. 각 항목의 길이는 0x08->8바이트이다.

페이지 오프셋은 더 크며 최소값 0과 최대값 4095를 포함할 수 있다. 4096 바이트는 4kb 단위의 바이트 수이다. 이는 이 예에서 최대 페이지 크기가 4kb임을 의미한다. 또한 페이지 테이블 오프셋과 달리 이 오프셋은 페이지 테이블 항목 번호가 아닌 페이지 기본 주소의 바이트 수를 나타낸다.

1. Page Map Level 4 Table (PML4T) 기본 주소 찾기

PML4T 주소의 기본 주소는 CR3 레지스터에 저장되며 각 프로세스는 자체 가상 주소 공간을 가진다.

따라서 각 프로세스의 컨텍스트 내에서 고유한 값이 CR3 레지스터에 저장된다.

Page Map Level 4 Entry (PML4E) 주소 찾기

PML4T 오프셋은 0xFF(255)이다.

255번째 PML4T 항목의 주소를 찾으려면

1. PML4E 의 바이트 수 (8바이트)에 오프셋 값(255)을 곱해야 한다.

2. 그 결과는 PML4T의 기본 주소에 추가된다.

Page Directory Pointer Table (PDPT) 기본 주소 찾기

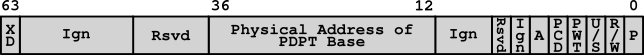

PML4E에 저장된 값은 0x0A000000`70c87867 이다.

이 값에서 PDPT의 기본 주소를 파생하려며 4kb 페이지에 매핑되는 페이지 테이블 항목의 구조를 이해해야 한다.

- PML4E 구조

Page Directory Pointer Entry (PDPE) 찾기

PDPT에서 PDPE를 찾는 과정은 본질적으로 PML4T에서 PML4E를 찾는 과정과 동일하며, PML4T와 마찬가지로 PDPT에서도 각각 길이가 0x08 바이트인 512개의 항목이 있다.

Page Directory Table (PDT) 기본 주소 찾기

PD의 기본 주소를 찾는 과정은 PDPT의 기본 주소를 찾는 과정과 동일하다.

Page Directory Entry (PDE) 찾기

PDE는 이전 단계에서 얻은 PDT의 기본 주소와 가상 주소의 오프셋을 사용하여 찾을 수 있다. 계산은 PML4E 및 PDPTE가 수행된 것과 동일한 방식으로 수행된다.

Page Table (PT) 기본 주소 찾기

PML4T, PDPT 및 PD 기본 주소를 찾는 데 사용된 계산은 마지막으로 PT의 기본 주소를 찾는 데 사용된다.

Page Table Entry (PTE) 찾기

Page 기본 주소 찾기

가상 주소를 해결하는 데 마지막 계산 다음이다. 이 단계에서는 페이지의 기본 주소를 찾는다. 다음 단계는 실제 주소를 찾는 것이다.

물리 주소 찾기

마지막 단계는 실제 주소 찾기이다. Page의 기본 주소에 페이지 오프셋을 추가하면 physical address를 찾을 수 있다. 이 단계에서는 프로세스가 페이지 테이블 항목 계산에서 설정된 패턴에서 벗어나는 단계이다.