pipelining?

: 명령어를 순차적으로 실행하는 프로세서에 적용하는 기술,

한 번에 하나의 명령어만 실행하는 것이 아닌,

동시에 여러 개의 명령어를 처리하여 throughput을 늘리는 것.

참고자료1

참고자료2

1. Instruction Execution Steps

-> RISC-V instructions classically take 5 steps

-> 이 스탭을 : pipeline stage라 부름

1) IF : 메모리로 부터 명령어 인출

2) ID : rd,rs,opcode 등 명령어 해독 및 레지스터 파일 읽기

3) EX : 실행 및 주소 계산

4) MEM : Access Memory

5) WB : 레지스터에 쓰기

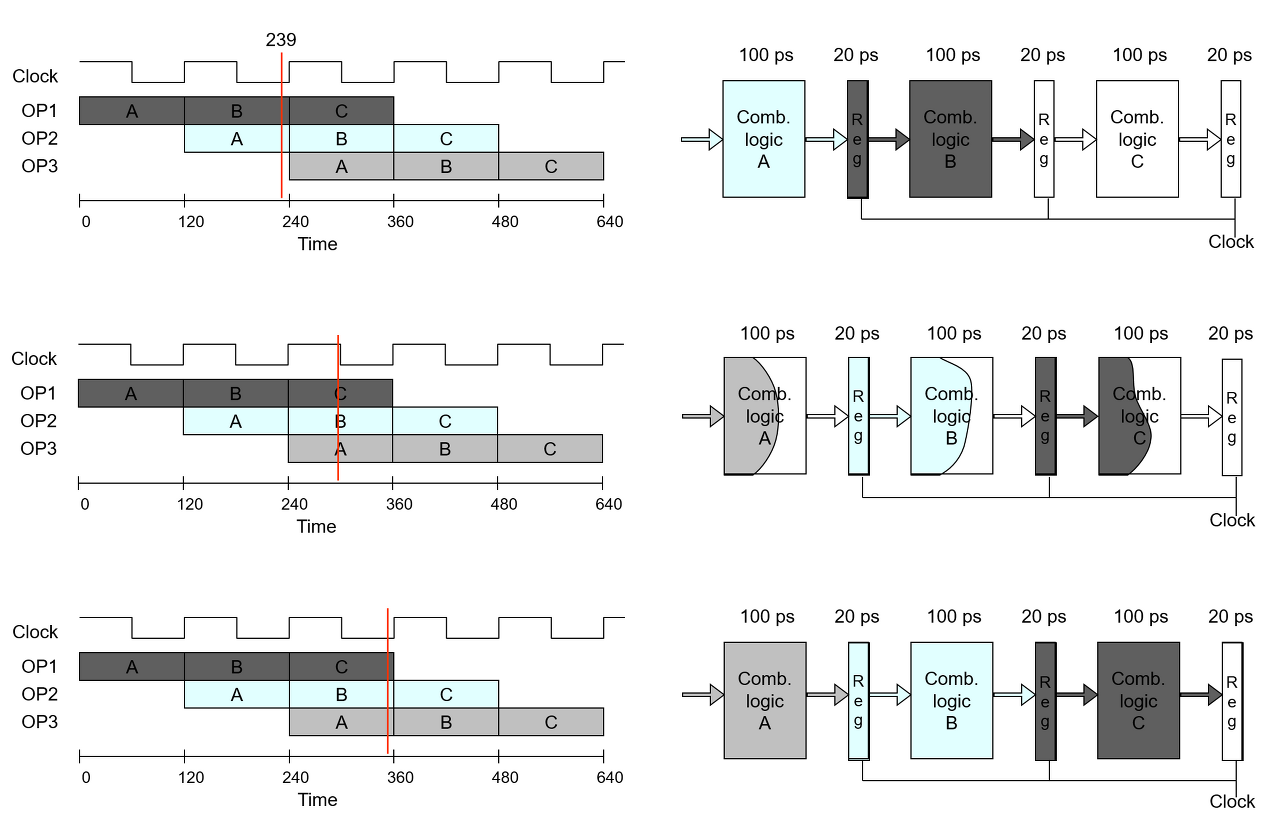

2. 파이프라인 동작 방식

★ 각 stage마다 2가지의 경우 기억하자

- 모든 stage가 balanced -> 동일한 시간

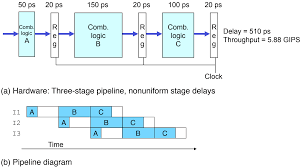

- 각 stage 마다 unbalanced lengths ---> Reduces speedup (왜? 가장 딜레이가 긴 단계에 맞춰서 클락주기 설계)

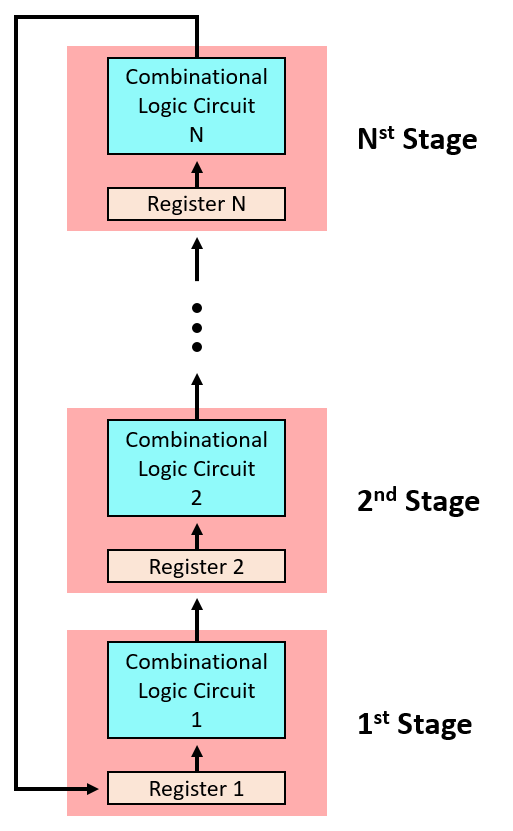

★ 단계별로 존재하는 파이프라인 레지스터

: 특정 단계의 파이프라인 레지스터는 직전 단계의 CLC에서 계산되어 전달받은 값들 저장됨. 그 값들을 바탕으로 CLC가 다음 단계로 전달할 값들 계산함.

★ 단계를 늘리면,

Overall latency increases -> 단계별 레지스터를 계속 두니까~

3. Speedup

- increased throughput

- don't help latency of single task

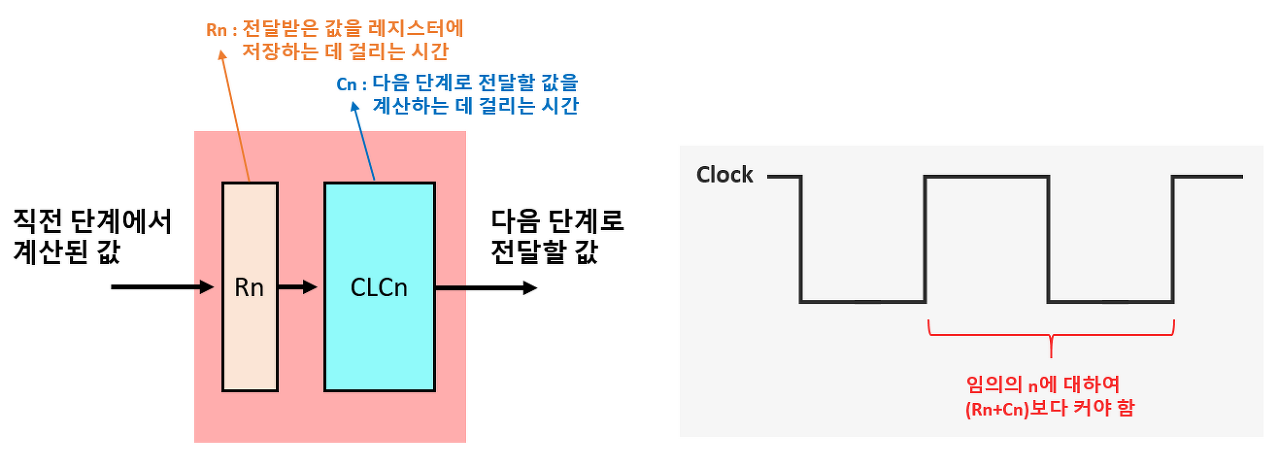

① Rn = 전달받은 값을 레지스터에 저장하는 데 걸리는 시간

② Cn = 다음 단계로 전달할 값을 계산하는 데 걸리는 시간

③ 총 지연 시간 (Overall Latency) = ∑(Rn+Cn)

④ 클락의 주기 = T ≥ max(Rn+Cn)

⑤ 처리량 (Throughput) = 1/T

이런 예제 연습해두자!!

If pipelining adds 0.2 ns to the machine clock cycle, calculate the amount of speedup in instruction execution from pipelining

4. 성능이슈

1) Nonuniform Delays

Throughput limited by slowest stage

2) Register Overhead

stage 개수를 늘릴수록, 한순간에 처리되는 명령어가 많아지고, 클럭 주기 짧아진다.

but,

파이프라인 레지스터 개수가 증가하면서 latency(총 지연시간) 증가함. 하지만 얘가 주는 장점이 확실해서 현대 프로세서들 through very deep pipelining

5. 주요 이슈

◆ instruction pipeline에서의 문제점

- 각 segment의 수행시간이 다르다. execute 단계의 시간이 가장 오래 걸리기 때문에, clock 속도를 제일 오래 걸리는 segment인 execute에 맞추어 주어야 한다.

- instruction에 따라서 일부 단계(특정 segment)는 스킵될 수 있다.

1) structural hazards

- 프로세서 자원 부족해서 발생

- resource conflicts

: 메모리 access는 한 순간에 하나의 레지스터만 접근. 명령어를 병렬처리하는 도중에 두 개의 segment에서 메모리에 access라고 한다면 resource conflict가 발생한다. (아,,, 운영체제에서 얼핏 배웠다.. 하하)

2) data hazards

- 직전 명령어의 실행 결과에 해당하는 레지스터의 값을 현재 명령어에서 사용해야 할 때 발생

- 해결 방법 2가지

- Forwarding : 직전 명령어의 실행 결과를 계산되는 즉시 현재 명령어에게 전달해주는 방식

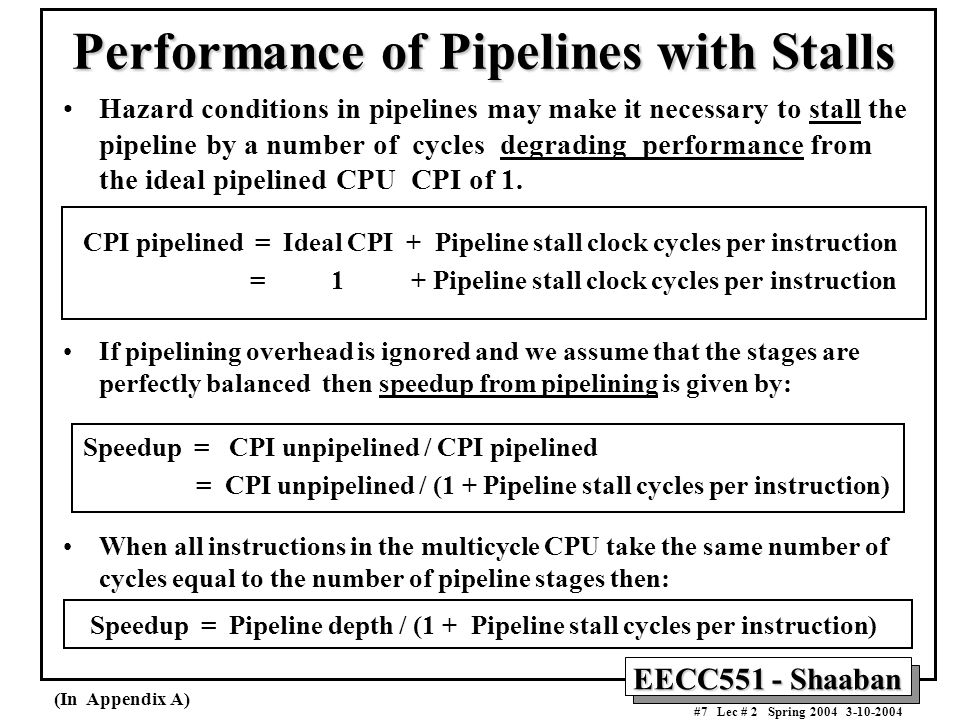

- Stalling : 직전 명령어의 실행 결과가 레지스터에 저장이 될 때까지 버블을 끼워 넣으며 기다리는 방식

3) control hazards

- 문제는 Fetch 단계에서 다음에 실행할 명령어의 주소를 정확히 알 수 없는 경우-> ex) branch, jump..

결론, 4과,,, 교재 예제를 풀어보든,,, ppt 예제라도 이해하자