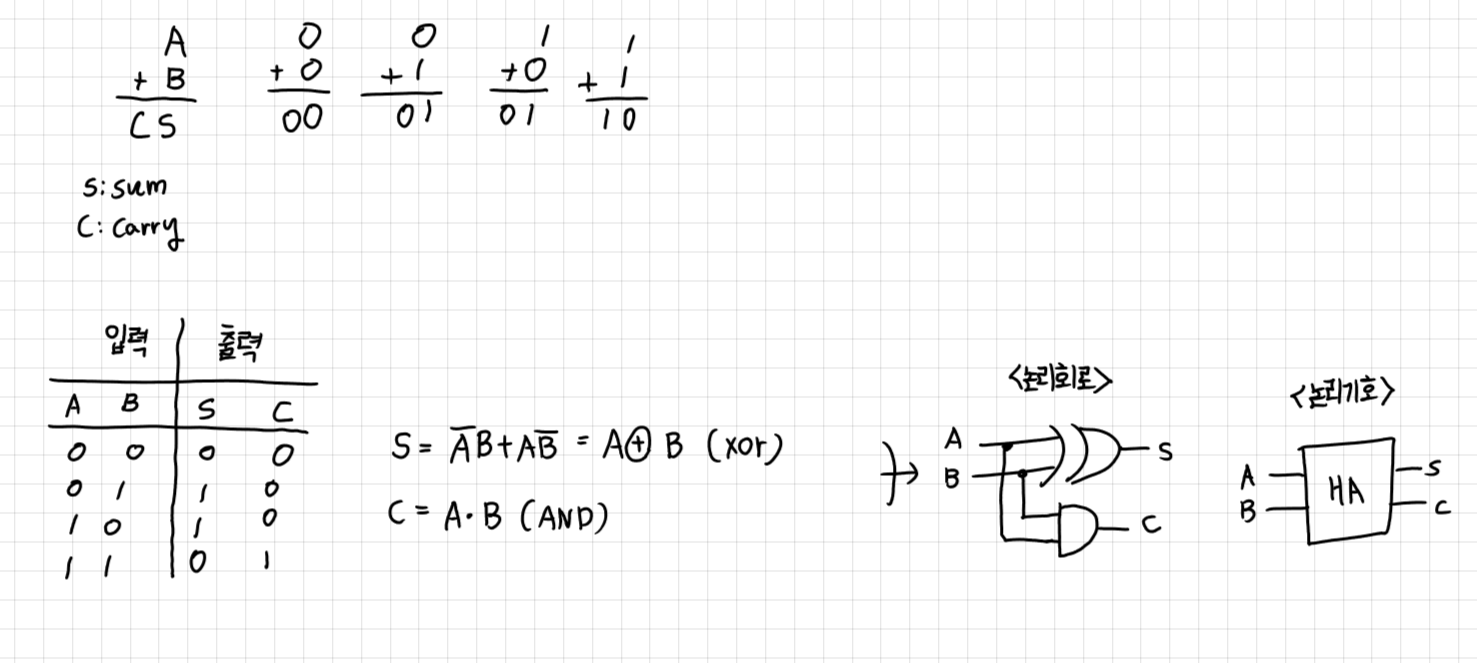

반가산기

이진수의 한자리수를 연산하고, 자리올림수는 자리올림수 출력(carry out)에 따라 출력

반가산기 설계 - 게이트 레벨 모델링

module HA(S,C,A,B);

input A,B ; // 입력 A,B

output S,C; // 출력 S(SUM),C(CARRY)

xor(S,A,B);

and(C,A,B);

endmodule

반가산기 설계 - 데이터 플로우 모델링

module HA(S,C,A,B);

input A,B ; // 입력 A,B

output S,C; // 출력 S(SUM),C(CARRY)

assign S = A^B; // XOR 게이트

assign C = A&B; // AND 게이트

endmodule

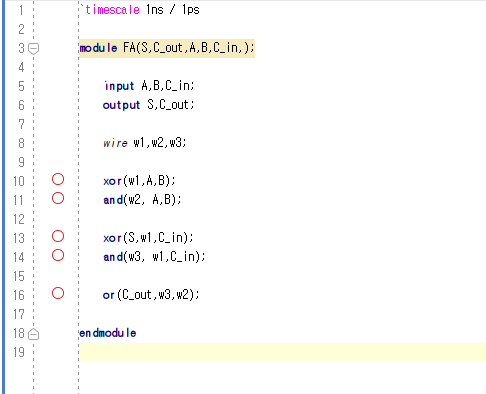

전가산기

자리 올림수(Carry)를 고려하여 만든 덧셈 회로

반가산기 2개와 OR게이트를 이용해 구성

net 선언

첫번째 HA의 XOR 게이트 출력 및 AND 게이트 출력

두번째 HA의 AND 게이트 출력

전가산기 설계 - 게이트 레벨 모델링

module FA(S,C_out,A,B,C_in);

input A,B,Cin ; // 입력 A,B

output S,C_out;

wire w1,w2,w3;

xor(w1,A,B);

and(w2,A,B);

xor(S,w1,C_in);

and(w3,w1,C_in);

or(C_out,w3,w2);

endmodule

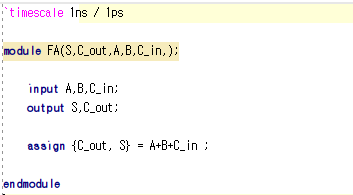

전가산기 설계 - 데이터 플로우 모델링

module FA(S,C_out,A,B,C_in);

input A,B,Cin ; // 입력 A,B

output S,C_out;

wire w1,w2,w3;

assign w1 = A^B;

assign w2 =A&B;

assign S = w1 ^ C_in;

assign w3 = w1 & C_in;

assign C_out = w3 | w2;

endmodule

module FA(S,C_out,A,B,C_in);

input A,B,Cin ; // 입력 A,B

output S,C_out;

assign {C_out,S}=A+B+C_in; // 할당과 결합 연산자로 간단히 표현가능

// bit 단위가 넘어가면 자동으로 C_out 결과값에 저장.

endmodule

wire가 없어진 것을 확인 가능.

assign을 선언하고 결합 연산자로 한줄로 표현.

bit 단위가 넘어가면 C_out에 결과값이 저장되게 됨.

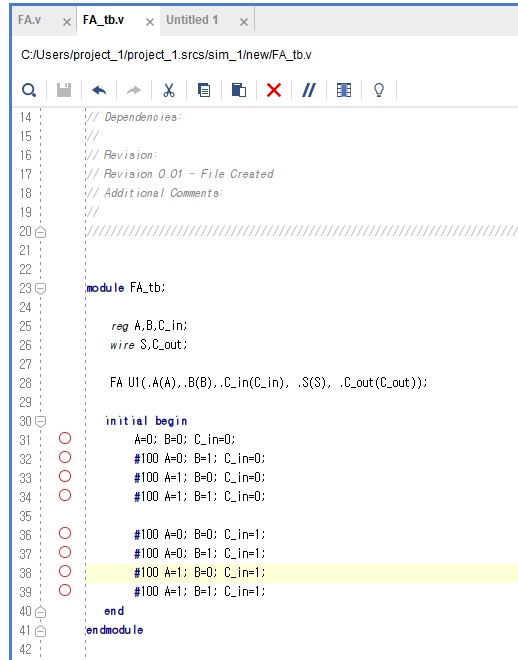

전가산기 Testbench 생성

- 위치에 의한 포트 연결

module testbench;

FA U0(S,C_out,A,B,C_in)l

endmodule - 이름에 의한 포트 연결

module testbench;

FA U0(.S(S), .C_out(C_out), .A(A), .B(B), .C_in(C_in));

// .모듈 선언 포트(testbench 선언 포트)

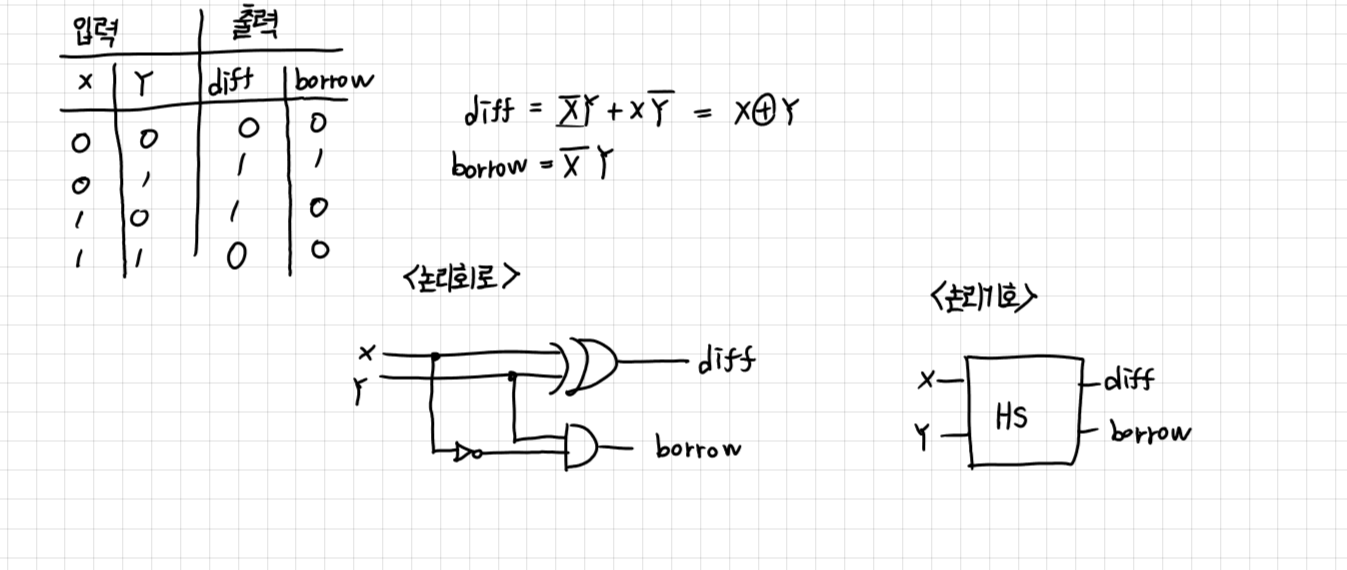

endmodule반감산기

2진수로 표시된 2개의 수의 차로 얻어진 감산기

입력 X, Y의 감산에 의해 얻어진 차(Difference)와 자리내림(Borrow) 발생

반감산기 설계 – 게이트 레벨 모델링

module HS(diff, borrow, X, Y);

input X, Y; // 입력 X, Y

output diff, borrow; // 출력 difference, borrow

wire w1;

xor (diff, X, Y); // XOR 게이트

and (borrow, Y, w1); // AND 게이트

not (w1, X); // NOT 게이트

endmodule반감산기 설계 – 데이터 플로우 모델링

module HS(diff, borrow, X, Y);

input X, Y; // 입력 A, B

output diff, borrow; // 출력 difference, borrow

assign diff = X^Y; // XOR 게이트

assign borrow= (~X)&Y; // NOT게이트와 AND 게이트

endmodule

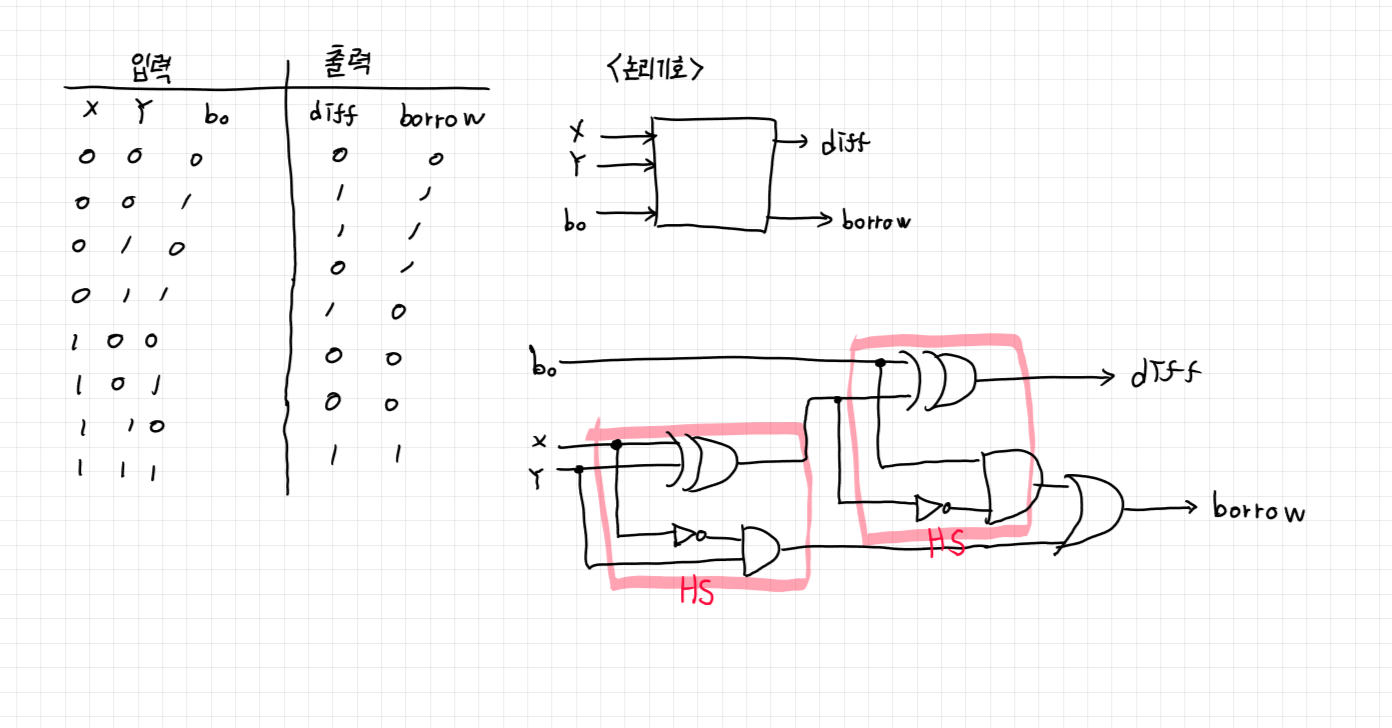

전감산기

net 선언

첫번째 NOT 게이트 출력 w1

AND 게이트 출력 w2

XOR 게이트 출력 w3

두번째 NOT 게이트 출력 w4

두번째 AND 게이트 출력 w5

전감산기 설계 – 게이트 레벨 모델링

module FS(diff, borrow, X, Y, b0);

input X, Y, b0; // 입력 X, Y, b0

output diff, borrow; // 출력 difference, borrow

wire w1, w2, w3, w4, w5; // net(wire) 선언

not (w1, X); // NOT 게이트

and (w2, w1,Y); // AND 게이트

xor (w3, X, Y); // XOR 게이트

not (w4, w3); // NOT 게이트

and (w5, w4, b0); // AND 게이트

xor (diff, w3, b0); // XOR 게이트

or (borrow, w2, w5); // OR 게이트

endmodule전감산기 설계 – 데이터 플로우 모델링

module FS(diff, borrow, X, Y, b0);

input X, Y, b0; // 입력 X, Y, b0

output diff, borrow; // 출력 difference, borrow

assign diff=X^Y^b0; // difference 할당

assign borrow=(~X&Y)|(~(X^Y)&b0); // borrow 할당

endmodule

전가산기 설계

1. 게이트 플로우 모델링

test bench

2. 데이터 플로우 모델링

test bench는 게이트 플로우 모델링과 동일

실행시 에러 날 때

module에서 port list 및 입출력 port 이름이 같은지 확인

port와 gate 선언 부분에서 대 소문자 구별 및 오타 확인

module 및 testbench에서 port 선언 부분 이름이 같은지 확인

📃참조

데이터 플로우 모델링

논리합성(데이터 플로우 수준의 설계를 게이트 수준의 설계로 생성) 기법이 있기 때문에 게이트 수준의 모델링보다 데이터 플로우 모델링으로 보다 쉽게 설계

연속 할당문

하나의 값을 net에 할당

assign <신호강도><지연 값><인수 목록> = <인자 값>;