1. Basic Elements

-

Processor (CPU 혹은 중앙 처리 장치)

1). 컴퓨터의 연산을 처리 및 관리

2). data processing functions을 수행 -

I/O Modules (입출력 모듈)

1). 컴퓨터와 외부 환경 간의 데이터 교류를 매개함.

ex) HDD와 같은 저장 장치, Terminals, 통신 장비 등 -

Main Memory (주 기억 장치)

1). 데이터와 프로그램을 저장.

2). 휘발성을 가짐 (컴퓨터가 종료되면 메모리의 내용이 손실됨). -

System bus

1). CPU, I/O Modules, 메모리간 통신을 도움.

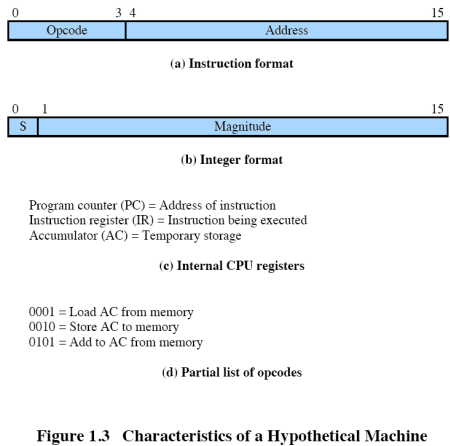

2. Instruction Execution

프로그램은 Instruction의 조합으로 구성되어 있으며, 메모리에 저장된다.

-

CPU는 명령어 레지스터 (IR)로 명령어를 로드함.

-

CPU는 명령어를 해석하고 적절한 동작을 수행함.

1). Processor - Memory

2). Processor - I/O

3). Data Processing

4). Control

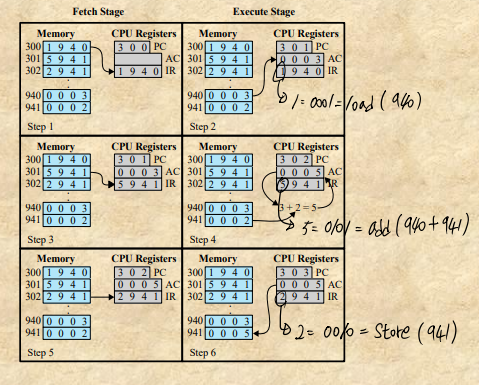

step 1 : Memory에서 IR로 첫 번째 (address = 300)명령어를 읽어옴.

step 2 : 1940 = 940을 AC로 (1 = 0001 = load)load하라는 명령어

step 3 : Memory read (address = 301)

step 4 : 5941 = 941을 AC에서 (5 = 0101 = add)add하라는 명령어.

step 5 : Memory read (address = 302)

step 6 : 2941 = 941에 AC의 데이터를 (2 = 0010 = store) memory에 store하라는 명령어.

3. Interrupts

다른 모듈이 프로세서의 정상적인 실행 순서를 방해하는 메커니즘. 어떤 Event가 발생했을 때, 이를 처리하기 위해 CPU에 알려주는 것이다. 인터럽트는 시스템의 반응성을 높이고, I/O 장치와 효율적인 통신, 시스템의 멀티태스킹 능력 향상, Multi Programming 구현 등 다양한 목적으로 사용된다.

-

프로세스 사용률을 향상시키기 위해 사용됨

-

현재 실행되고 있는 프로세스보다 먼저 실행되어야 할 프로세스가 존재한다면, Interrupt를 통해 실행 순서를 조절할 수 있음.

-

Program Interrupts (Trap) : 프로그램 명령어 실행의 결과로 인터럽트가 발생함. 이는 주로 프로그램의 오류(Divide by zero) 또는 System call, Debugging 등의 이유로 발생한다. OS는 이를 처리하기 위한 특정 루틴을 실행한다.

ex) overflow, divide by zero, attempt to execute an illegal machine instruction, reference outside a user's allowed memory space... -

Timer interrupts : 프로세서 내부의 타이머에 의해 발생하는 인터럽트.

-

I/O Interrupts : I/O 컨트롤러에 의해 발생.

-

Hardware failure : power failure, memory parity error 등에 의해 발생한다.

Trap / Interrupt

- 공통점

1). 둘 다 정상적인 프로세스 실행의 흐름을 중단시킨다.

2). 특정 작업을 수행한 뒤 원래의 작업으로 돌아온다.

3). OS는 Interrupt or Trap을 처리하기 위해 사전에 정의된 루틴(Interrupt Handler, Exception Handler)을 실행한다.

- 차이점

1). Interrupt는 주로 하드웨어 이벤트에 의해 발생하지만 Trap은 프로그램 내부 명령어에 의해 발생한다.

2). Interrupt는 언제든지 발생할 수 있으며 비동기적이지만, Trap은 프로세스 실행 중 특정 조건에 도달했을 때 발생하며 동기적이다.

3). Interrupt는 시스템의 반응성과 멀티태스킹을 위한 목적, Trap은 오류 처리 및 System call과 같은 프로그램의 특정 동작을 지원하기 위한 목적이다.

** 비동기적 (비순차적 실행) : 인터럽트와 같이, 프로세서가 현재

수행중인 작업과는 관계없이 다른 작업을 처리하는 것을 의미한다.

** 동기적 (순차적 실행) : 트랩과 같이, 작업들이 순차적으로

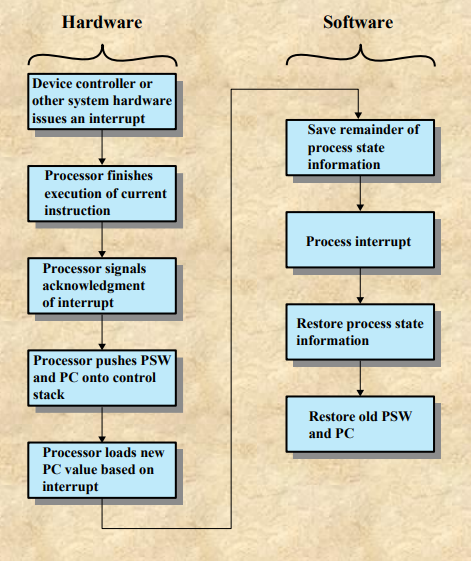

수행되며 각 작업의 시작과 종료가 연속적이다.- Interrupt 처리 과정

1). 인터럽트 발생 및 신호 전달 : I/O 장치 또는 다른 외부 요인으로 인해 인터럽트가 발생 CPU에 인터럽트 신호 전달

2). 현재 명령어 완료 : 인터럽트 신호를 전달받은 CPU는 해당 신호를 보낸 장치에 확인 신호를 보낸다. 확인 신호를 받은 장치는 인터럽트 발생 신호를 제거한다.

3). 현재 상태 저장 : 프로세서는 인터럽트 지점에서 현재 프로그램을 재개하는 데 필요한 정보를 저장한다. 이때 저장되어야 하는 최소한의 정보는 PSW(프로그램 상태 단어), 실행될 다음 Instruction의 위치이다 (location 정보는 Program Counter에 있음).

4). DMA Controller 작동 : I/O 인터럽트의 경우, DMA 컨트롤러가 활성화되어 메모리와 I/O 장치간의 데이터 전송을 관리한다. CPU는 이 과정에 직접적으로 관여하지 않기때문에, 다른 프로세스의 작업을 수행할 수 있다.

5). 인터럽트 처리 완료 : I/O 인터럽트의 경우, DMA 컨트롤러가 데이터 전송을 완료하면, 프로세서에 인터럽트 처리 완료 신호를 보낸다.

6). 인터럽트 처리 루틴 실행 : 인터럽트 처리 완료 신호를 받은 프로세서는 인터럽트 처리 루틴의 시작 위치로 프로그램 카운터(PC)를 업데이트한다. 프로세서는 발생한 인터럽트 신호에 포함된 정보 (인터럽트 벡터 테이블)를 참조하여 인터럽트를 처리할 루틴을 결정한다 (IDT를 이용해 ISR을 호출한다).

7). 작업 재개 : 인터럽트 처리 루틴 실행이 완료되면, 프로세서는 이전에 저장했던 프로세스의 상태를 복구한 뒤 작업을 재개한다.

- Trap 처리 과정

1). 트랩 발생 : 프로그램이 실행 중 특정 조건을 만족하거나, 예외 상황이 발생하여 트랩 발생.

2). 현재 상태 저장

3). 제어 전환 : 트랩이 발생하면 제어는 OS로 전환된다. 운영체제는 트랩 벡터를 참조하여, 해당 트랩을 처리하는 루틴의 주소를 찾는다.

4). 트랩 처리 루틴 실행

5). 작업 재개

I/O Interrupt와 같은 외부 Interrupt가 발생했을 때, 프로세서는 I/O Processing에 개입하지 않는다. 이를 처리하는 장치는 따로 존재하므로, I/O Processing이 이루어지는동안 프로세서는 디른 프로세스 작업을 수행할 수 있다. (DMA)

Trap과 같은 내부 인터럽트가 발생했을 때는, 프로세서가 이를 직접 처리해아한다.

- IDT(Interrupt Descriptor Table) : IDT는 인터럽트 서비스 루틴(ISR)의 주소를 저장하는 테이블이다. 인터럽트가 발생했을 때, OS는 IDT를 사용해 각 인터럽트 타입에 해당하는 처리 루틴을 빠르게 찾아 실행할 수 있다.

1). IDT의 구조 : IDT는 다수의 엔트리로 구성되며, 각 엔트리는 특정 인터럽트 또는 Trap에 대응하는 인터럽트 서비스 루틴의 주소를 가리킨다. 이 테이블은 메모리에 저장되며, CPU는 IDTR(Interrupt Descriptor Table Register)라는 레지스터를 사용해 IDT의 위치를 저장하고 있다.

2). IDT 엔트리의 구성 : IDT 엔트리는 일반적으로 인터럽트 게이트, 트랩 게이트가 존재한다. 이들은 인터럽트 혹은 트랩이 발생했을 때, 실행될 코드의 세그먼트 선택자와 주소를 포함한다. 또한 이들 게이트는 Descriptor Privilege Level (DPL)을 포함하고 있는데, 해당 ISR이 어떤 권한 레벨에서 실행될 수 있는지를 지정한다.

3). IDT의 역할 : IDT는 시스템의 안정성과 보안을 유지하는 데 중요한 역할을 한다. 예를 들어, 사용자 모드에서 실행중인 프로그램이 커널 모드의 메모리 영역에 접근하려고 시도할 때 예외가 발생한다. OS는 IDT를 통해 해당 예외 처리 루틴을 실행시킨다.

4). IDT의 설정 : OS가 부팅될 때, 커널은 IDT를 초기화하고 각 인터럽트 또는 트랩에 대응하는 ISR의 주소를 IDT에 설정한다.

4. Vi 명령 실행 과정

1). Keyboard device driver 작동 (typing vi)

2). Command interpreter 작동

3). Loader (vi 명령을 메모리에 load)

4). fork() System call Vi Process creation

5). Cpu Scheduling : process의 작동 순서를 cpu가 배정

6). open() System call file open

7). editing (= Vi)

8). close() System call file close

9). exit() System call process에 할당된 resource 회수

- 결론

명령어 입력 System call Instruction code (ex c) Compiler binary code to executable code

** 논리 주소 (logical address) : 프로그램이 참조하는 주소

** 물리 주소 (Physical address) : 실제 메모리 상의 위치를 나타내는 주소

** executable code : binary code가 logical address에서

physical address로 address translation

** CPU가 메모리에서 Process를 처리할 때, physical address를

참조하여 작업을 수행한다. 따라서 논리 주소를 실제 메모리 상의

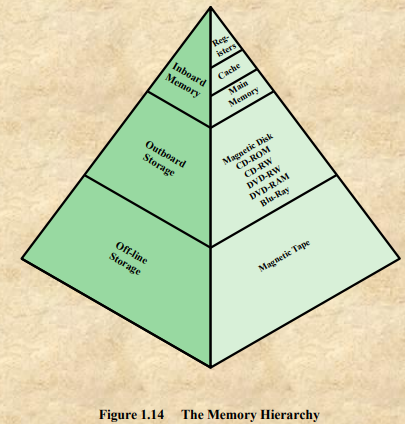

물리 주소로 변환하는 과정이 필요하다.5. Memory Hierarchy

메모리 계층구조(Memory Hierarchy)는 비용 대비 효율적으로 빠른 접근 속도와 큰 저장 용량을 제공하는 것을 목적으로 한다. 이 계층구조는 속도, 용량, 비용의 차이를 기반으로 구성되는데, 상위 계층으로 갈수록 용량이 작고 비싸지고, 빨라진다.

-

메모리가 프로세서의 속도를 따라가지 못하면, 시스템 전체 성능이 저하될 수 있다.

메모리는 프로세서가 데이터에 빠르게 접근할 수 있을만큼 충분한 속도를 제공해야 함. -

이상적인 메모리는 용량이 크면서 속도가 빠른 것인데, 현실적으론 너무 비싸다.

메모리는 고성능과 비용 효율성 사이의 균형을 잘 찾아야한다.

1). 레지스터 (Register) : CPU 내부에 위치하며, 가장 빠른 접근 속도를 가지지만 용량이 매우 작다. CPU가 현재 처리중인 명령어와 데이터를 저장한다.

2). 캐시 메모리 (Cache Memory) : CPU와 메인 메모리 사이에 위치하며 자주 사용되는 데이터와 명령어를 저장한다. 캐시는 여러 레벨(L1, L2, L3)로 구성될 수 있으며, 레벨이 낮을수록 CPU에 가깝고 빠르다.

3). 주 메모리 (Main Memory) : RAM으로 불리기도 한다. 프로그램과 현재 사용되는 데이터를 저장한다. CPU와 저장장치 사이에 위치해 있다.

4). 보조 메모리 (Secondary Storage) : HDD, SDD와 같은 비휘발성 저장 장치이다. 주 메모리보다 접근 속도가 느리다.

메모리 하이라키 구조는 시스템 전체 성능과 비용대비 효율성을 최적화하기 위해 고안된 구조이다.

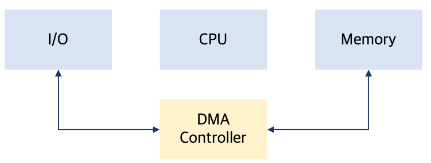

6. Direct Memory Access (DMA)

데이터가 이동할 때마다 모든 과정에 프로세서가 관여하면, 시스템 전체의 작업 효율이 떨어질 수 있다. DMA는 작업의 효율성 증가와 프로세서를 효율적으로 활용하기 위해서 고안된 기법이다. 시스템 버스에 별도의 모듈로 수행될 수도 있고, I/O 모듈에 통합된 형태일 수도 있다.

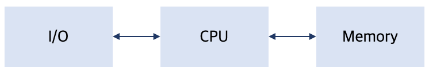

- 기본적인 입출력 제어 방식

1). 저장 장치에서 Data를 꺼내옴.

2). System bus를 통해 CPU Register에 Data가 옮겨짐.

3). CPU Register에 있던 Data가 System bus를 통해 Memory로 이동함.

모든 메모리 접근 연산이 CPU에 의해서 이루어짐. 따라서 CPU 작동이 자주 방해받음. 효율성 감소.

- Direct Memory Access (DMA)

1). 명령 발행 : 프로세서는 DMA 모듈에 데이터 전송을 요청하는 명령을 발행한다.

2). DMA 설정 : DMA 모듈은 프로세서가 요청한 정보들의 데이터 전송 작업을 설정한다.

3). CPU 할당 해제 : DMA 모듈이 설정을 완료하여 CPU는 다른 작업을 수행할 수 있다. 데이터 전송 과정에서 CPU의 개입은 필요없다.

4). 데이터 전송 : DMA 모듈은 설정된 정보에 따라 메모리와 I/O 장치간에 직접 데이터를 전송한다.

5). 전송 완료 및 인터럽트 : 데이터 전송이 완료되면, DMA 모듈은 전송 완료 인터럽트를 CPU에 보내 작업 완료를 알린다.

6). 후처리 : CPU는 작업 완료 인터럽트를 받고 필요한 후처리 작업을 수행할 수 있다 (데이터 전송 결과 확인, 다른 데이터 전송 작업 요청 등).

DMA기법은 DMA Controller가 데이터 블록의 전송을 직접 관리한다. 주변장치와 메모리 사이의 통신에 CPU의 개입을 최소화하기 때문에 CPU의 작업 효율성을 증가시킨다.

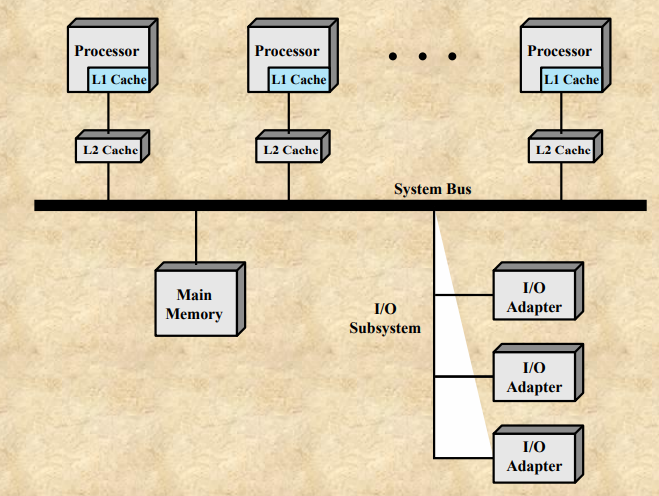

7. Symmetric Multiprocessors (SMP)

대칭형 멀티 프로세서(SMP)는 여러 개의 프로세서가 메모리와 I/O 장치를 공유하는 컴퓨터 시스템 아키텍처이다. SMP는 멀티프로세싱을 구현하는 방식 중 하나로, 각 프로세서가 동일한 작업 능력을 가지며 시스템 내에서 평등하게 작동한다.

1). 프로세서 공유 : SMP 시스템에는 두 개 이상의 프로세서가 존재하며, 이 프로세서들은 메인 메모리와 I/O 장치를 공유한다.

2). OS의 역할 : SMP 시스템은 통합된 OS에 의해 제어된다. OS는 프로세서간의 작업 분배, 메모리 접근 동기화, I/O 접근 관리 등을 관리하며 프로세서와 프로그램간의 상호 작용을 조율한다.

3). 확장성과 성능 : SMP는 시스템의 처리 능력을 쉽게 확장할 수 있게 해준다. 동시에 더 많은 작업을 처리할 수 있으며, 이는 당연히 시스템 전반의 성능 향상을 이끌어낸다.

- SMP 시스템의 이점

1). 병렬 처리 : 2개 이상의 프로세서가 작업을 병렬로 수행하기 때문에 작업 처리 능력이 증가한다.

2). 안정성(가용성) : 한 프로세서에 오류가 발생하더라도, 나머지 프로세서들이 작업 수행을 유지할 수 있어 시스템 전체의 안정성이 증가한다. 따라서 서버 및 중요 업무용 시스템에 적합.

3). 점진적 성능 향상 : 시스템의 성능을 향상시키기 위해 추가 프로세서를 쉽게 설치할 수 있음.

4). 확장성 : 제조업체는 다양한 가격 및 성능을 가진 제품을 제공함으로써, 다양한 고객의 요구를 충족시킬 수 있다.

SMP 시스템은 성능 확장성, 시스템의 안정성, 높은 성능을 필요로 하는 비즈니스, 서버 혹은 과학 연구 분야에서 유용함.