CS에 대해서 잘 알아야 프로그래밍을 더 효율적으로 짤 수 있기도 하고,

면접 준비도 필요하기 때문에 오늘부터 CS를 공부해보기로 한다!

우선 CS공부는 이 사이트에 나와있는 거 먼저 싹 훑어보고 점차 디테일하게 공부해나갈 예정이다.

그리고 그냥 눈으로 보는 것 보다 자료를 찾으면서 블로그에 정리하는 게 훨씬 기억에 잘 남아서 공부하는 내용을 블로그에 정리하려고 한다.

컴퓨터 구조

-

하드웨어

- 컴퓨터 시스템이 작동하는 데 필요한 물리적 구성 요소

- 중앙처리장치(CPU), 기억장치(RAM, HDD), 입출력 장치(마우스, 프린터) 등

-

소프트웨어

- 하드웨어의 동작을 지시하고 제어하는 명령어 집합

- 시스템 소프트웨어(운영체제, 컴파일러), 응용 소프트웨어(워드프로세서, 스프레드시트)로 나누어짐

하드웨어

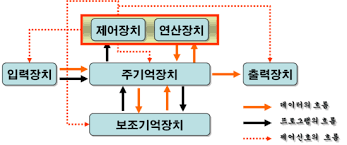

하드웨어는 cpu, 기억장치, 입출력장치로 구성돼있다.

그리고 이들은 시스템 버스를 통해서 데이터와 제어 신호를 각 장치에 전달하게 된다.

1. CPU (중앙처리장치)

사람으로 따지면 두뇌와 같은 역할을 한다.

각종 연산을 수행하고 기억장치에 기억되어 있는 명령어들을 수행하는 핵심부품이다.

주기억장치에서 프로그램 명령어와 데이터를 읽어와 처리하고 명령어의 수행 순서를 제어한다.

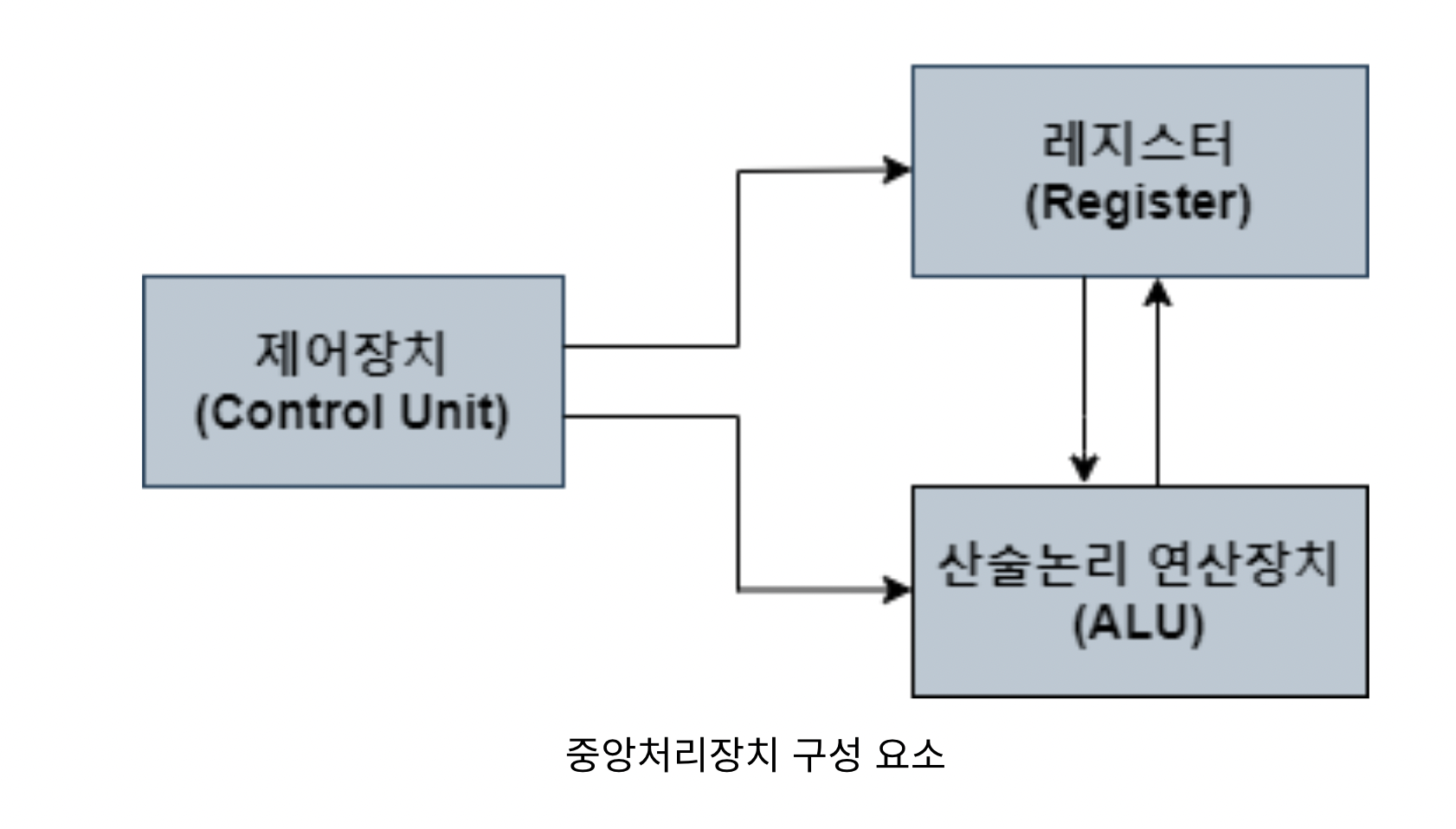

산술논리연산장치(ALU)와 제어장치, 레지스터로 구성돼 있다.

산술논리 연산장치(Arithmetic Logic Unit)

- 산술연산과 논리연산 수행

- 연산에 필요한 데이터를 레지스터에서 가져오고, 연산 결과를 다시 레지스터로 보낸다.

- 제어장치의 명령에 따라 실제로 연산을 수행하는 장치이다.

- 캐시나 메모리로부터 읽어 온 데이터는 레지스터에 저장되며, ALU는 레지스터에 저장된 데이터를 이용하여 덧셈, 곰셈 등과 같은 산술 연산을 수행한다

제어장치

- 명령어를 순서대로 실행할 수 있도록 제어하는 장치

- 주기억장치에서 프로그램 명령어를 꺼내 해독하고, 그 결과에 따라 명령어 실행에 필요한 제어 신호를 기억장치, 연산장치, 입출력장치로 보내고 이들 장치가 보낸 신호를 받아, 다음에 수행할 동작을 결정함

- 명령어의 해석과 실행을 담당

- 컴퓨터에 있는 모든 장치들의 동작을 지시하고 제어하는 장치

- 명령 레지스터에서 읽어 들인 프로그램 코드(명령어)를 해석하고, 해당하는 장치에 제어 신호를 보내 정확하게 실행하도록 지시한다.

레지스터

- 속도가 빠른 cpu내부의 데이터 기억장소(메모리)

- CPU에서 바로 처리할 수 있는 데이터를 담고 있다

- CPU 내부에서 처리할 명령어나 연산의 결과나 주소 등을 일시적으로 기억하는 임시 기억 장소이다

- 주로 산술 연산 논리장치에 의해 사용되는 범용 레지스터(General-Purpose Register)와 PC 등 특수 목적에 사용되는 전용 레지스터(Dedicated-Purpose Register)로 구분할 수 있다.

- 프로그램의 수행 순서를 제어하는 프로그램 계수기(program counter), 현재 수행중인 명령어의 내용을 임시 기억하는 명령 레지스터(instruction register), 명령 레지스터에 수록된 명령을 해독하여 수행될 장치에 제어신호를 보내는 명령해독기(instruction decoder)로 이루어져 있다.

범용 레지스터 : 연산에 필요한 데이터나 연산 결과를 임시로 저장

특수목적 레지스터 : 특별한 용도로 사용하는 레지스터

특수 목적 레지스터 중 중요한 것들

MAR(메모리 주소 레지스터) : 읽기와 쓰기 연산을 수행할 주기억장치 주소 저장

PC(프로그램 카운터) : 다음에 수행할 명령어 주소 저장

IR(명령어 레지스터) : 현재 실행 중인 명령어 저장

MBR(메모리 버퍼 레지스터) : 주기억장치에서 읽어온 데이터 or 저장할 데이터 임시 저장

AC(누산기) : 연산 결과 임시 저장

2. 기억장치

특정 프로그램을 실행하면 컴퓨터는 보조기억장치에 저장된 데이터를 주기억장치로 불러오고 CPU가 해당 데이터를 처리하게 된다.

프로그램, 데이터, 연산의 중간 결과를 저장하는 장치이다.

주기억장치와 보조기억장치로 나누어진다.

주기억장치

- 용량이 크고 처리 속도가 빠르다.

- 실행중인 프로그램에 필요한 데이터를 일시적으로 저장한다.

- 컴퓨터 내부에서 현재 CPU가 처리하고 있는 내용을 저장하고 있는 기억장치

- 예로는 RAM과 ROM이 있음

- ROM: 전원이 끊어져도 기록된 데이터들이 소멸되지 않는 비휘발성 메모리(Non-Volatile Memory), 데이터를 한번 저장하면 특별한 방법을 쓰지 않는 한 수정을 할 수가 없음

- RAM: 읽고 쓰기가 가능, 전원이 끊어지면 데이터가 전부 지워지는 휘발성 메모리(Volatile Memory)

보조기억장치

- HDD(기계식), SSD(전자식)

- CPU에서 직접 접근이 불가능한 기억장치, 접근하려면 디바이스 드라이버와 시스템 콜을 통하여 기억장치의 특정 위치의 내용을 주기억장치로 로드(Load)한 뒤 읽어야 한다.

- 주기억장치에 비해 속도는 느리지만 많은 자료를 영구적으로 보관할 수 있는 장점이 있다.

캐시 메모리(Cache Memory)

- CPU와 주기억 장치 사이의 속도 차이를 완화시키기 위해 고속 버퍼(임시) 메모리이다.

- CPU와 주기억장치 사이에 존재한다.

- 속도가 빠르지만 용량이 적고 가격이 비싸다.

- CPU가 주기억장치에서 저장된 데이터를 읽어올 때, 자주 사용하는 데이터를 캐시 메모리에 저장한 뒤,

다음에 이용할 때 주기억장치가 아닌 캐시 메모리에서 먼저 가져오면서 속도를 향상시킨다.

캐시메모리에 대한 추가 설명은 여기서 보면 된다.

정리가 매우 잘 돼 있다.

3. 입출력장치

입력과 출력 장치로 나누어진다.

입력 장치는 컴퓨터 내부로 자료를 입력하는 장치 (키보드, 마우스 등)

출력 장치는 컴퓨터에서 외부로 표현하는 장치 (프린터, 모니터, 스피커 등)

4. 시스템 버스

하드웨어 구성 요소를 물리적으로 연결하는 선이다.

CPU와 기타 장치 사이에서 데이터를 전달한다.

각 구성요소가 다른 구성요소로 데이터를 보낼 수 있도록 통로가 된다.

용도에 따라 데이터 버스, 주소 버스, 제어 버스로 나누어진다.

기본 동작

컴퓨터는 기본적으로 읽고 처리한 뒤 저장하는 과정으로 이루어진다.

이 과정을 진행하면서 끊임없이 주기억장치(RAM)과 소통한다.

이때 운영체제가 64bit라면, CPU는 RAM으로부터 데이터를 한번에 64비트씩 읽어온다.

쓰기 동작 과정 : 버스 사용권을 획득, 주소와 데이터 및 쓰기 신호를 전송

읽기 동작 과정 : 버스 사용권을 획득, 주소와 읽기 신호를 보내고 데이터가 전송되어

올 때까지 대기

데이터 버스

- 중앙처리장치와 기타 장치 사이에서 데이터를 전달하는 통로

- 데이터버스의 크기는 CPU가 한 번에 전송 가능한 데이터의 크기와 같다.

- 기억장치와 입출력장치의 명령어와 데이터를 중앙처리장치로 보내거나, 중앙처리장치의 연산 결과를 기억장치와 입출력장치로 보내는 '양방향' 버스이다.

주소 버스

- CPU가 주기억 장치나 I/O 장치로 기억장치 주소를 전달하는 통로

- 중앙처리장치가 주기억장치나 입출력장치로 기억장치 주소를 전달하는 통로이기 때문에 '단방향' 버스이다.

- 예) 프로세서에서 001010010이란 위치에 데이터를 보내려면 데이터 뿐만 아니라 목적지인 001010010도 주소 버스를 통해서 보낸다.

제어 버스

- 데이터 버스와 주소 버스를 제어하기 위해 제어 신호들을 전송하는 통로

- 주소 버스와 데이터 버스는 모든 장치에 공유되기 때문에 이를 제어할 수단으로 사용된다.

- 중앙처리장치가 기억장치나 입출력장치에 제어 신호를 전달하는 통로이다.

- 제어 버스는 읽기 동작과 쓰기 동작을 모두 수행하기 때문에 '양방향' 버스이다.

- 제어 신호 종류 : 기억장치 읽기 및 쓰기, 버스 요청 및 승인, 인터럽트 요청 및 승인, 클락, 리셋 등

기억장치 쓰기 신호 : 버스에 실린 데이터를 주소가 지정하는 기억장소에 저장 되도록 하는 제어 신호

기억장치 읽기 신호 : 주소가 지정하는 기억장소의 내용을 읽어서 버스에 실리게 하는 제어 신호

I/O 쓰기 신호 : 버스에 실린 데이터를 지정된 I/O 장치로 출력되게 하는 제어 신호

I/O 읽기 신호 : 지정된 I/O 장치로부터 데이터를 읽어서 데이터 버스에 실리게 하는 제어 신호

5. CPU의 동작 과정

- 주기억장치는 입력장치에서 입력받은 데이터 또는 보조기억장치에 저장된 프로그램 읽어 온다.

- CPU는 프로그램을 실행하기 위해 주기억장치에 저장된 프로그램 명령어와 데이터를 읽어와 처리하고 결과를 다시 주기억장치에 저장한다.

- 주기억장치는 처리 결과를 보조기억장치에 저장하거나 출력장치로 보낸다.

- 제어장치는 1~3 과정에서 명령어가 순서대로 실행되도록 각 장치를 제어한다.

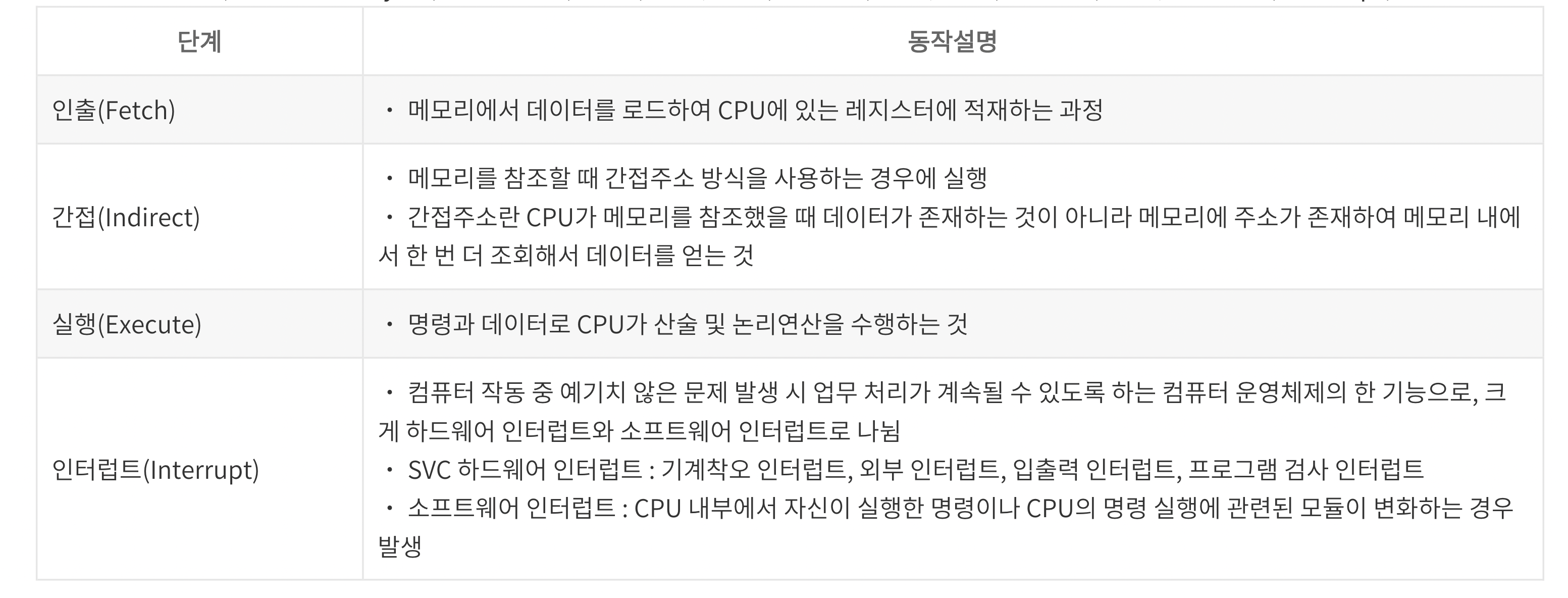

명령어 사이클

- CPU가 주기억장치에서 한번에 하나의 명령어를 인출하여 실행하는데 필요한 일련의 활동

- 인출(Fetch) 단계, 간접(Indirect) 단계, 실행(Execute) 단계, 인터럽트(Interrupt) 단계

- 주기억장치의 지정된 주소에서 하나의 명령어를 가져오고, 실행 사이클에서는 명령어를 실행한다.

하나의 명령어 실행이 완료되면 그 다음 명령어에 대한 인출 사이클 시작

명령어 세트란?

CPU가 실행할 명령어의 집합

연산 코드(Operation Code) + 피연산자(Operand)로 이루어짐

연산 코드 : 실행할 연산, 연산, 제어, 데이터 전달, 입출력 기능을 가짐

피연산자 : 필요한 데이터 or 저장 위치, 주소, 숫자/문자, 논리 데이터 등을 저장

인출 사이클과 실행 사이클에 의한 명령어 처리 과정

인출 사이클

- PC에 저장된 주소를 MAR로 전달

- 저장된 내용을 토대로 주기억장치의 해당 주소에서 명령어 인출

- 인출한 명령어를 MBR에 저장

- 다음 명령어를 인출하기 위해 PC 값 증가시킴

- 메모리 버퍼 레지스터(MBR)에 저장된 내용을 명령어 레지스터(IR)에 전달

T0 : MAR ← PC

T1 : MBR ← M[MAR], PC ← PC+1

T2 : IR ← MBR실행 사이클

ADD addr 명령어 연산

T0 : MAR ← IR(Addr)

T1 : MBR ← M[MAR]

T2 : AC ← AC + MBR오늘은 여기까지

조금 더 하고 싶지만 며칠전에 라섹을 했더니 아직 앞이 제대로 안보인다ㅠㅠ

참고자료