🔊 ARM

- Load Store architecture로 load와 store 명령어를 통해서만 메모리에 접근이 가능하다.

Three classes

- Single Register Data Tranfer (LDR / STR)

- Block Data Transfer (LDM / STM)

- Single Data Swap (SWP)

🔈 Single register data tranfer

<LDR|STR> {<cond>} {<size>} Rd, <address>

- LDR/STR - Load/Store word

Addressing mode

- Base registers

- PC에 있는 General-pupose register

- offset

- Immediate

- unsigned 12 bit value

- Register

- General-pupose register (not PC)

- Scaled register

- General-pupose register shifted by immediate value

- 모두 base register로부터 더하거나 빼질 수 있다.

- Immediate

memory address

- Offset

- 명령어 실행 전 base register에 offset을 더한 후 그 값을 load

- Pre-indexed

- 명령어 실행 전 base register에 offset을 더한 후 그 값을 load

- 마지막에 ! 붙여 Auto-indexing으로 되어 base register 값이 update된다.

- Post-indexed

- 명령어 실행 후 base register에 offset을 더한 후 base register 값을 update된다.

- R1은 base register이고 그 위에오는 것이 offset이다.

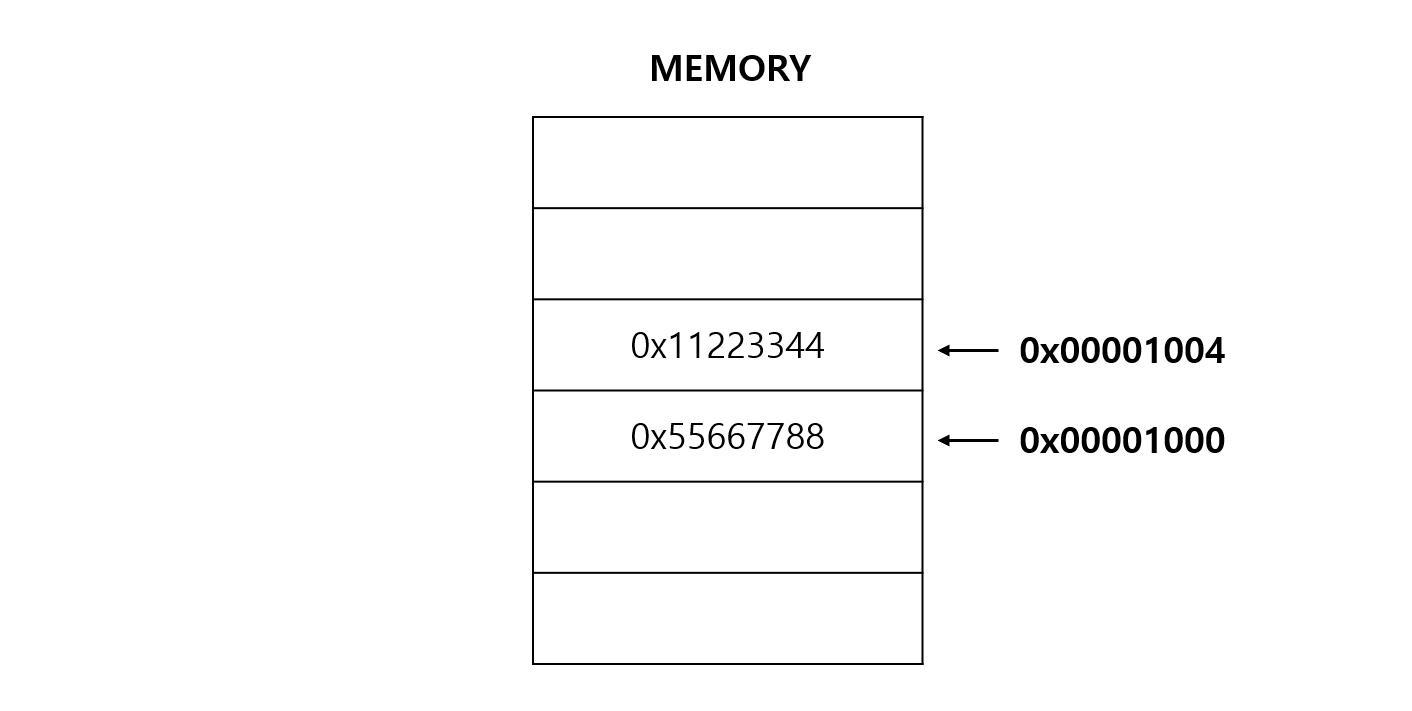

offset

LDR R0, [R1, #4]R1은 0x00001000이고 R0은 R1 + 4 주소에 있는 값인 0x11223344가 된다.

pre-indexed

LDR R0, [R1, #4]!R1 + 4 주소값에 있는 값을 R0에 저장한 후 R1(base register)를 R1 + 4(0x00001004)로 update한다.

post-indexed

LDR RO, R1, #4현재 R1의 값을 load하여 R0에 저장하여 R0는 0x55667788이 되고, 실행 이후 R1은 0x00001000에서 0x00001004로 update된다.