💡 본 게시글은 아래 기술 블로그를 참고하였습니다.

출처 :

https://maloveforme.tistory.com/152

https://velog.io/@apphia39/%EC%BB%B4%ED%93%A8%ED%84%B0%EA%B5%AC%EC%A1%B0ISA-CISC-vs.-RISC

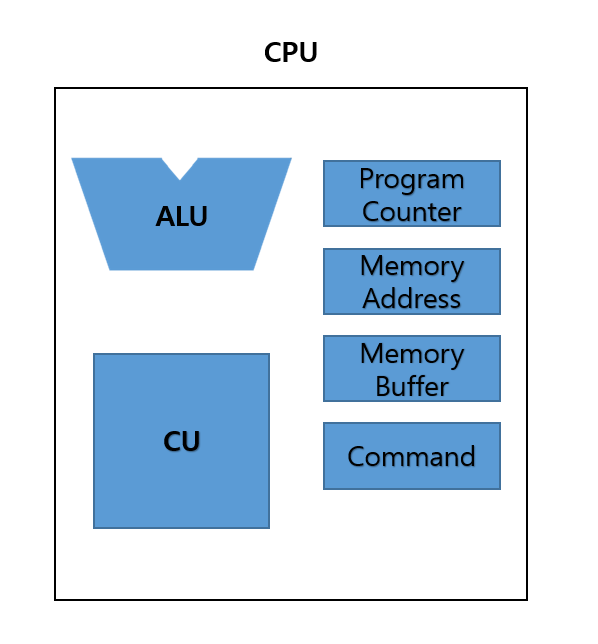

CPU란?

CPU(Central Processing Unit 중앙처리장치)는 컴퓨터 및 MCU의 핵심 연산 장치로서, 메모리에서 명령어를 읽어와 이를 해석하고 수행하는 작업을한다.

즉, 사람의 두뇌와 같이 컴퓨터의 모든 시스템을 제어, 처리하는 가장 핵심적인 장치라고 할 수 있다.

CU가 명령을 가져오고 해석한 후, ALU에서 연산을 수행하고, 결과를 레지스터나 메모리에 저장하는 흐름!

주요 구성 요소

-

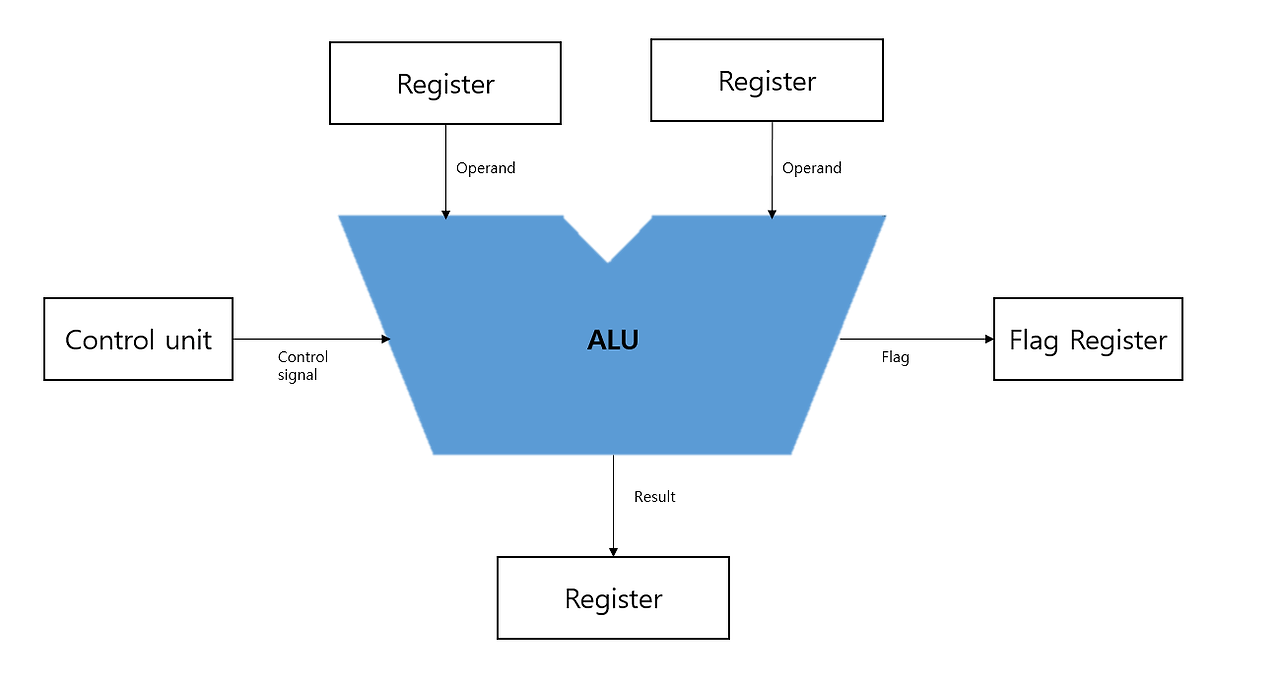

ALU (Arithmetic Logic Unit, 연산 논리 장치)

다양한 산술 연산 및 논리 연산을 처리한다.

- 레지스터를 통해 입력받은 피연산자와 제어 유닛으로 부터 받은 명령에 따라 ALU는 연산을 수행하고, 이 결과는 다시 레지스터에 저장되어 필요에 따라 메모리에 전송된다.

- CPU와 메모리 간의 데이터 전송 속도가 상대적으로 느리기 때문에 레지스터를 활용한다.

- 또한, ALU의 연산 결과를 플래그 레지스터에 저장함으로써, 추가적인 상태 정보를 제공한다. (부호, 오버플로우 등)

- 부호 플래그 (결과의 부호)

- 제로 플래그 (결과가 0인지)

- 캐리 플래그 (결과가 올림수, 빌림수인지)

- 오버플로우 플래그 (오버플로우가 발생했는지)

- 인터럽트 플래그 (인터럽트가 가능한지)

- 슈퍼바이저 플래그 (커널 모드로 실행 중인지, 사용자 모드로 실행 중인지)

-

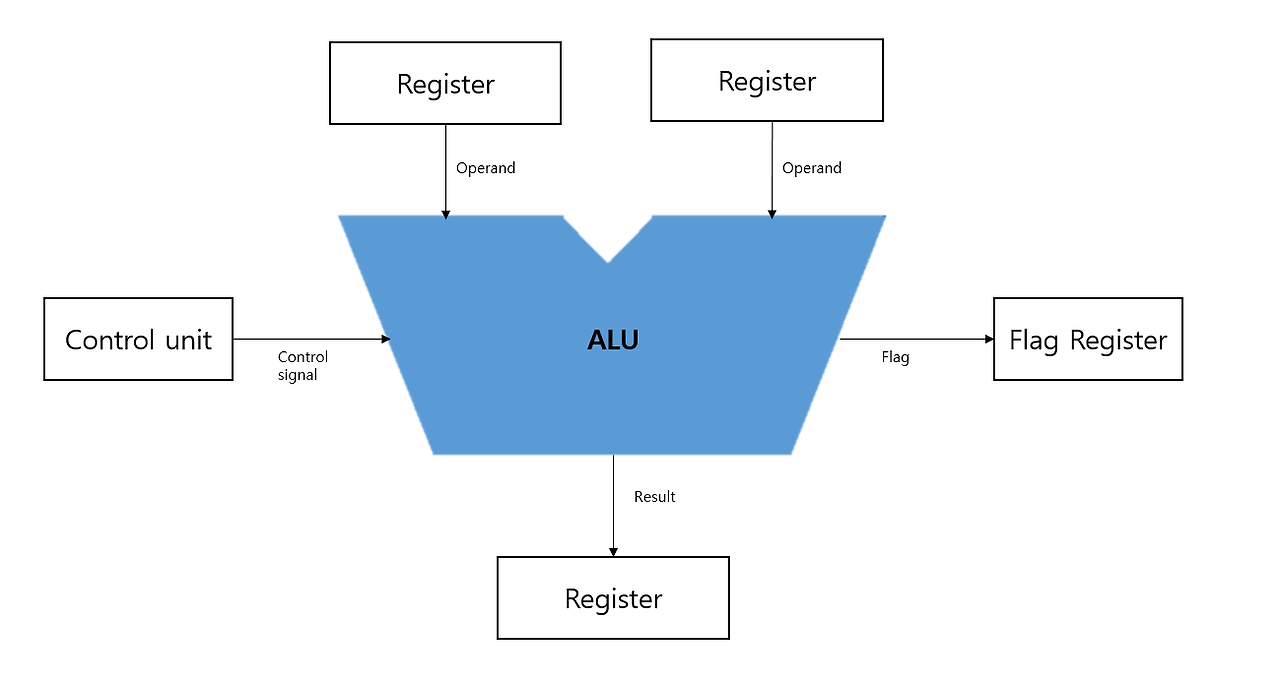

CU (Control Unit, 제어 장치)

다양한 하드웨어 구성 요소들을 조율하고 관리하는 역할을 한다. 이는 시스템 전체의 효율적인 작동을 위해 전기적 제어 신호를 발생시키고, 이를 통해 다른 컴퓨터 부품들의 동작을 제어한다.

- 클럭 신호를 받아들인다. (클럭이란, 컴퓨터에서 특정한 간격으로 반복되는 신호를 의미한다.)

- 클럭 신호는 일종의 타이밍 신호로서, 컴퓨터의 각 부품이 동기화되어 동작하도록 만드는 역할을 한다.

- 모든 컴퓨터 부품이 동일한 클럭 속도로 작동하는 것은 아니다.

- 클럭 속도가 빠르다고 해서 모든 작업의 속도가 반드시 빨라지는 것도 아니다. 일부 작업들이 병렬 처리가 불가능하거나, 다른 부품의 지연 시간에 의해 제한될 수 있기 때문이다.

- 명령어 레지스터에서 명령어와, 플래그 레지스터에서 플래그를 받아들인다.

- 명령어 레지스터는 CPU가 해석해야 할 명령어를 저장하고, 이를 제어장치에 전달한다.

- 제어장치는 이를 해석하고 필요한 제어 신호를 발생시킨다.

- 이 때, 플래그 값이 참조되어 제어 신호의 생성에 영향을 끼친다.

- 플래그는 CPU의 이전 연산 결과 및 상태 등을 갖고있는데, 다음 연산이 어떻게 수행될 것인지를 결정하는 데 중요한 역할을 한다.

- 제어 버스로 전달된 제어 신호를 받아들인다.

- 제어 신호는 CPU말고 I/O 같은 외부 장치에서도 발생한다.

- 즉, 제어 버스를 통해 다른 컴퓨터 부품들로부터 제어 신호를 받아들일 수 있다.

- 이런 제어 신호를 통해 제어 장치는 CPU의 작동을 조율하고, 필요한 경우 적절한 응답을 생성한다.

- 클럭 신호를 받아들인다. (클럭이란, 컴퓨터에서 특정한 간격으로 반복되는 신호를 의미한다.)

-

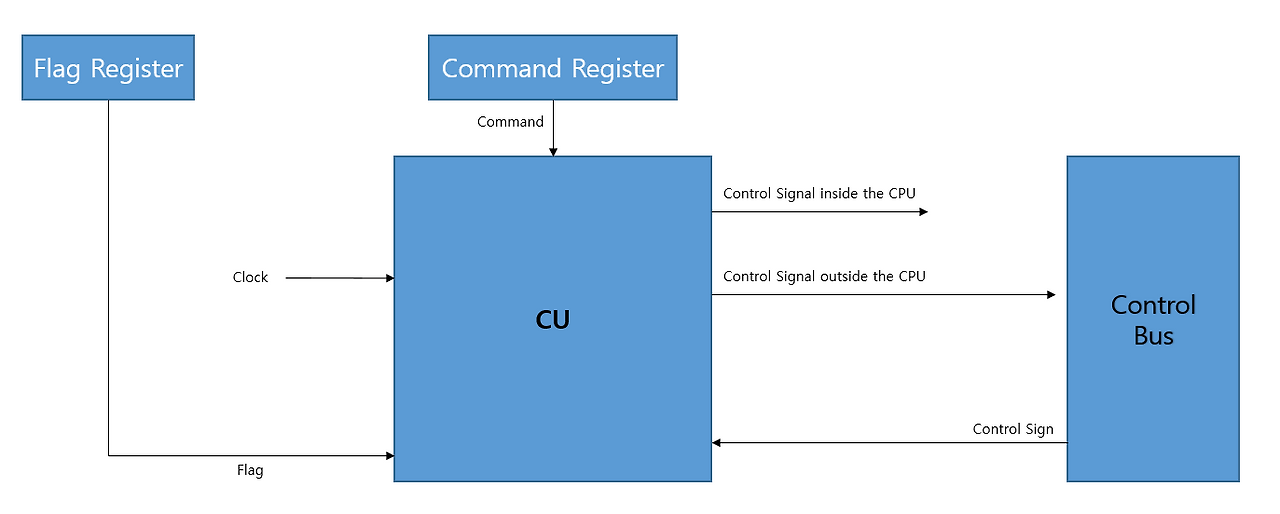

Register (레지스터)

프로그램 속 명령어와 데이터는 실행 전후로 반드시 레지스터에 저장된다. 레지스터는 CPU 내부에서 연산을 위해 사용되는 초고속 메모리, 캐시는 CPU와 RAM 사이에서 자주 사용하는 데이터를 저장하여 속도를 높이는 중간 저장소이다. (L1은 코어 내부, L2는 내부 또는 외부에, L3은 여러 코어가 공유하여 외부에 있음)

-

프로그램 카운터 (Program Counter, PC)

✅ 메모리에서 읽어 들일 명령어의 주소를 저장하는 레지스터 -

명령어 레지스터 (Command Register, Instruction Register, IR)

✅ 현재 CPU가 해석하고 있는 명령어를 저장하는 레지스터이다.메모리에서 읽어온 명령어는 먼저 이 레지스터에 저장되고 CPU는 이곳에서 명령어를 읽고 해석하고 실행한다.

-

메모리 주소 레지스터 (Memory Address Register, MAR)

✅ 메모리의 주소를 저장하는 레지스터이다.CPU가 메모리의 특정 위치에서 데이터를 읽어야 할 경우, 그 주소는 이 레지스터에 먼저 로드되고, 이후 메모리 접근 시 이 레지스터의 정보를 사용하여 해당 위치를 찾는다.

-

메모리 버퍼 레지스터 (Memory Buffer Register, MBR)

✅ 메모리와 주고 받을 데이터와 명령어를 저장하는 레지스터이다.CPU가 메모리에서 데이터를 읽을 때, 해당 데이터는 이 레지스터에 저장되고, CPU는 이 레지스터를 통해 데이터를 가져온다. 또한, CPU가 메모리에 데이터를 쓸 때, 데이터는 이 레지스터에 저장되고, 메모리가 이 레지스터에서 데이터를 가져온다.

-

범용 레지스터 (General Purpose Register)

✅ 다양한 목적에 맞게 사용할 수 있는 레지스터이다.산술 연산, 논리 연산, 메모리 주소 저장 등에 활용된다. 이 레지스터의 크기와 수는 CPU의 설계에 따라 차이가 있다. 이 레지스터는 CPU의 작업 효율성을 크게 향상하는 역할을 하는데, 임시 데이터 저장소로 활용되거나 연산 과정에서의 중간 결과 유지 등의 용도로 쓰인다. 때문에! CPU가 메모리에 직접 접근하는 것보다 더 빠르게 데이터에 접근하게 해, 처리 속도를 향상한다.

-

플래그 레지스터 (Flag Register)

✅ CPU가 수행한 최근 연산에 대한 정보, 그리고 CPU의 현재 상태를 나타내는 여러 플래그를 저장한다. -

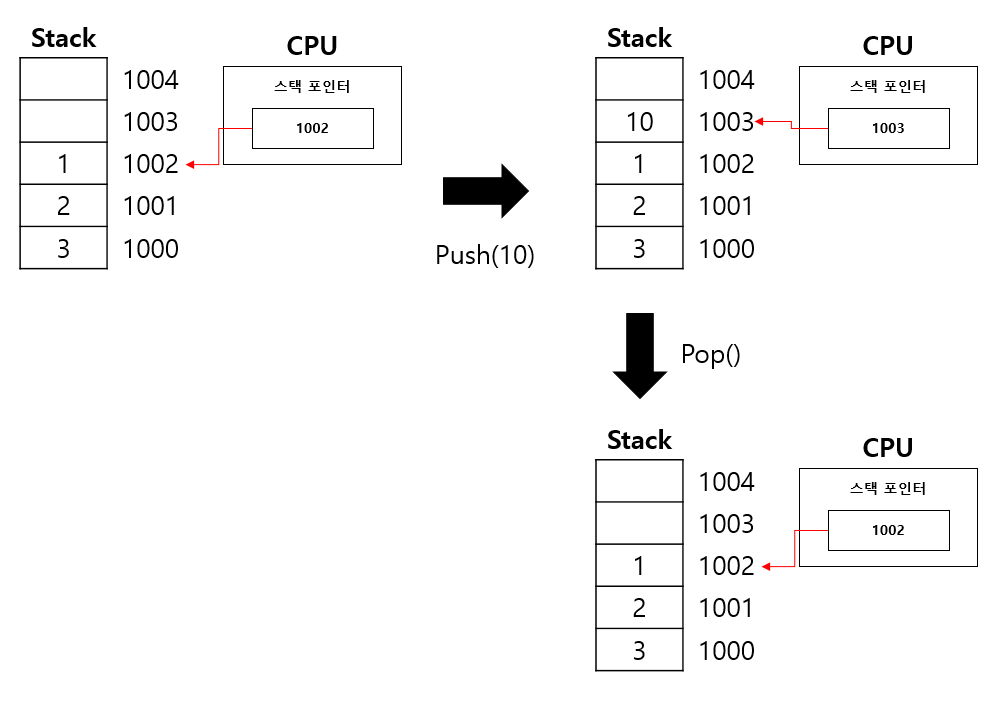

스택 포인터 (Stack Pointer)

✅ 스택의 가장 위를 가리키는 레지스터이다. (현재 스택의 최상단 주소)

-

CPU의 동작 방식

CPU는 명령어 주기 (Intstruction Cycle)을 통해 명령어를 실행한다.

✅ 1) Fetch (가져오기) → 메모리에서 명령어를 가져옴

✅ 2) Decode (해석하기) → 명령어를 해석하여 실행 준비

✅ 3) Execute (실행하기) → 연산 수행 (ALU 계산, 데이터 이동 등)

✅ 4) Write Back (저장하기) → 결과를 레지스터 또는 메모리에 저장

위 과정은 클럭에 맞춰 반복된다.

ISA (Instruction Set Architecture)

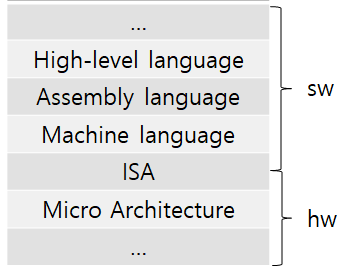

소프트웨어와 하드웨어 사이의 약속 (인터페이스)

개발자들은 high level language로 코드를 짠다. (C, C++ 등등) 하지만 컴퓨터가 이를 이해하기 위해서는 빌드 과정을 거쳐 어셈블리어 -> 기계어로 번역된다. 이렇게 번역된 기계어로 HW에게 명령을 내려줘야 하는데, 이 때 SW와 HW를 연결해주는 것이 ISA이다.

즉, ISA는 SW와 HW가 서로 통신할 수 있게 해주는 명령어들의 집합과 구조이다.

- 프로그램이 어떤 명령어를 사용해야 하는지 정의

- 하드웨어가 어떻게 명령을 실행해야 하는지 정의

✅ ISA = 프로그래밍 가능한 CPU의 명령어 세트 + 하드웨어가 실행하는 규칙

- ISA 아래에 있는 Micro Architecture는 Micro processor가 사용하는 명령어 처리 방식이다. 이 때, Micro processor는 우리가 아는 CPU로 생각하면 된다.

다시 말해, CPU가 실행할 수 있는 명령어와 동작 방식을 정의하는 것을 ISA라고 한다.

ISA는 크게 2종류로 나뉜다.

CISC (Complex Instruction Set Computing)과

RISC (Reduced Instruction Set Computing)으로 구분된다.

CISC (Complex Instruction Set Computing)

- SW 의존도를 낮추고 하드웨어에서 모든 기능을 수행하려 함. (하드웨어가 복잡하고 전력 소모가 큼)

- 메모리에서 직접 연산 가능

- 복잡한 명령어 지원 (한 개의 명령어가 여러 개의 연산 수행 가능 : 메모리 접근 + 연산 + 데이터 이동 등)

- 명령어 길이가 가변적 (1 ~ 15 바이트)

- 실행 속도가 상대적으로 느림 (명령어 해석 복잡)

- 명령어 실행 방식 : MUL, A, B -> 하드웨어가 직접 곱셈 연산 수행

- ex) x86 (Intel, AMD)

RISC (Reduced Instruction Set Computing)

- SW 의존도를 높이고, 단순한 명령어를 빠르게 실행하여 성능을 최적화하려 함. (하드웨어가 단순하고 전력 소모가 낮음)

- 단순하고 최소한의 명령어 지원 (한 개의 명령어는 한 가지 연산만 수행)

- 명령어 길이가 고정적 (32비트, 파이프라이닝 최적화 가능)

- 실행 속도가 빠름

- 로드/스토어 방식 (연산은 레지스터에서만 수행)

- 명령어 실행 방식 : LOAD R1, A -> LOAD R2, B -> MUL R3, R1, R2 -> STORE R3, C

- ex) ARM (Cortex-M, A) : 스마트 폰, MCU, 임베디드 장치

RISC-V : 오픈소스 RISC 아키텍처, 다양한 연구 및 상용 제품에 사용

MIPS : 네트워크 장비, 임베디드 시스템