What do WE mean by "Synthesis"?

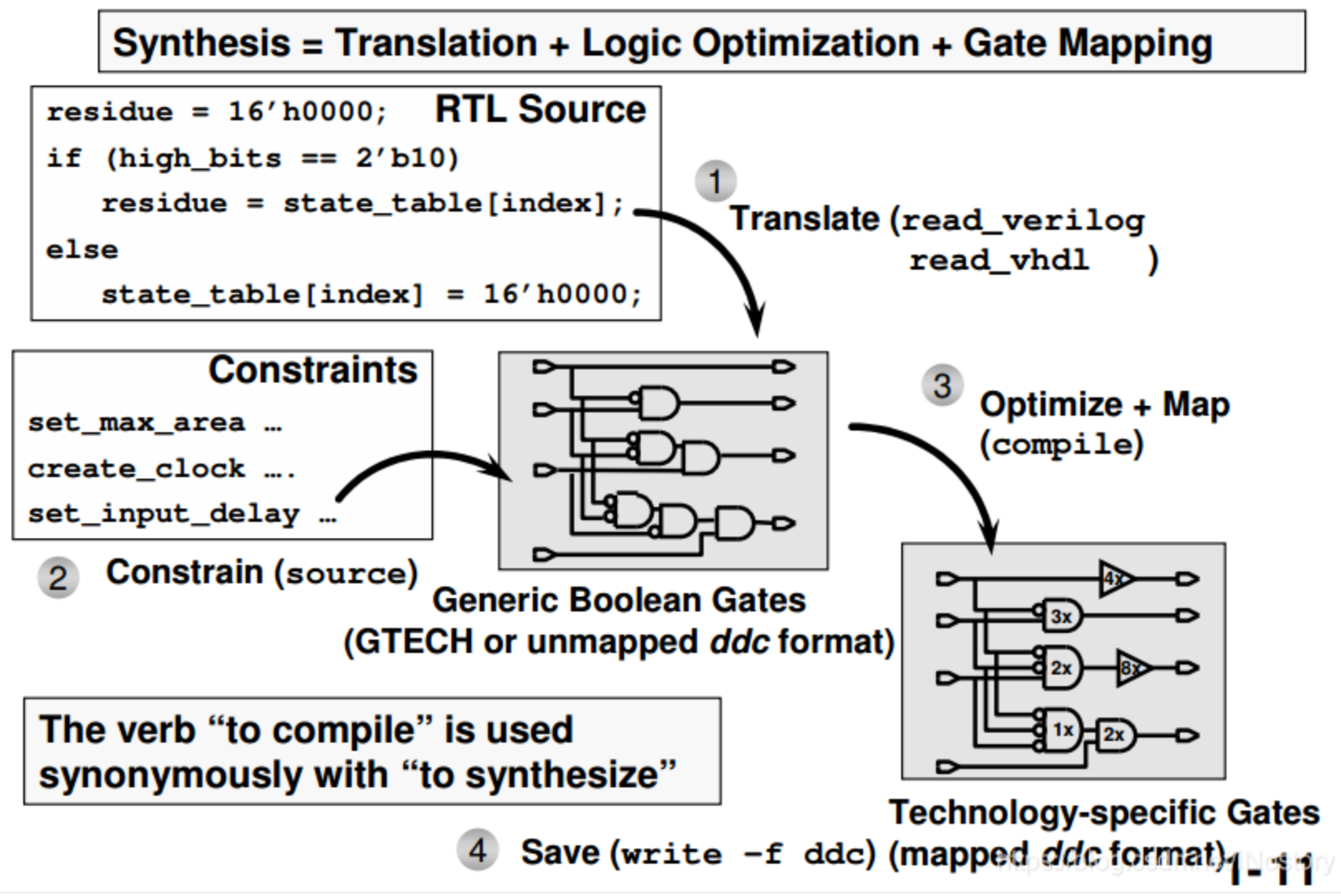

Synthesis = Translation + Logic Optimization + Gate Mapping

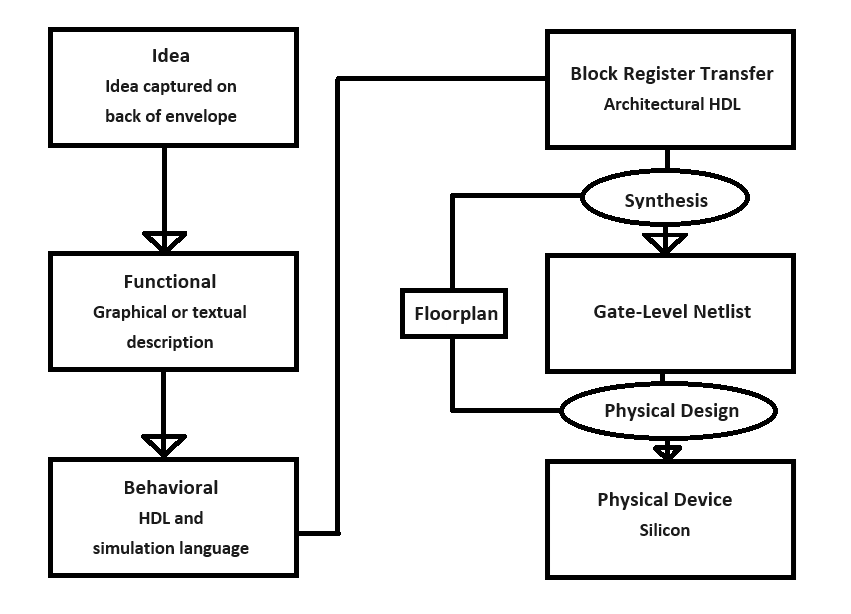

Functional Description

- 목적 : 새로운 디자인의 의도를 검증하는 데 사용됩니다.

- 사용 시점 : 초기 설계 단계에서 기능 요구 사항을 검증할 때 사용됩니다.

- 기능 : 설계의 주요 기능을 설명하고 이를 통해 설계가 의도된 대로 동작하는지 확인합니다.

- 방법 : 설계의 기능을 기술한 문서나 설명서를 작성하며, 이는 시뮬레이션이나 테스트 벤치를 통해 검증됩니다.

Behavioral

- 목적 : 시스템 레벨에서 설계를 모델링하고 주요 알고리즘과 대안적 아키텍처를 포착합니다.

- HDL(Hardware Description Language): Verilog, VHDL 등을 사용하여 작성됩니다.

- 사용 시점 : 초기 설계 단계에서 시스템의 동작을 모델링할 때 사용됩니다.

- 기능 : 전체 시스템의 동작을 고수준에서 설명합니다. 이 단계에서는 구체적인 하드웨어 구현보다는 설계의 동작 논리에 초점을 맞춥니다.

- 주요 요소 : 알고리즘, 데이터 흐름, 상태 기계 등 시스템의 주요 동작을 설명합니다.

Register Transfer Level (RTL)

- 목적: 설계를 상세히 모델링하여 합성할 수 있는 충분한 세부 정보를 제공합니다.

- 사용 시점: 설계의 상세 구현 단계에서 사용됩니다.

- 기능: 클럭 신호, 레지스터, 데이터 경로 등을 포함한 상세한 하드웨어 구조를 설명합니다.

- trade-off: area과 timing의 trade-off를 합성할 수 있을 정도의 세부 정보가 포함됩니다. (area와 timing은 반비례관계)

Place & Route (P&R)

-

목적 : Gate-Level Netlist를 실제 칩으로 구현하기 위해 물리적 레이아웃을 설계합니다.

-

입력 : Gate-Level Netlist

-

기능 : 각 게이트의 위치를 결정하고, Routing(게이트 간의 연결을 물리적으로 배선)

-

출력 : GDSII 파일 (Graphic Data System II).

- GDSII 파일 : 이 파일은 최종 칩 제조를 위한 photomask를 만드는 데 사용됩니다. 설계의 모든 레이어 정보가 포함되어 있습니다.

-

단계

- Floorplanning : 주요 블록들의 위치를 정하고 전원 및 클럭 분배 네트워크를 설계합니다.

- Placement : 각 셀을 최적의 위치에 배치합니다.

- Clock Tree Synthesis (CTS) : 클럭 신호를 각 레지스터에 안정적으로 분배합니다.(주로 backend,,, 셀깔고 그다음 배선을 깔기에)

- Routing : 신호를 연결하고 최적의 배선을 찾습니다.

- Sign-off : 타이밍, 전력, 신뢰성 등을 검증하여 설계가 제조 가능하도록 합니다.

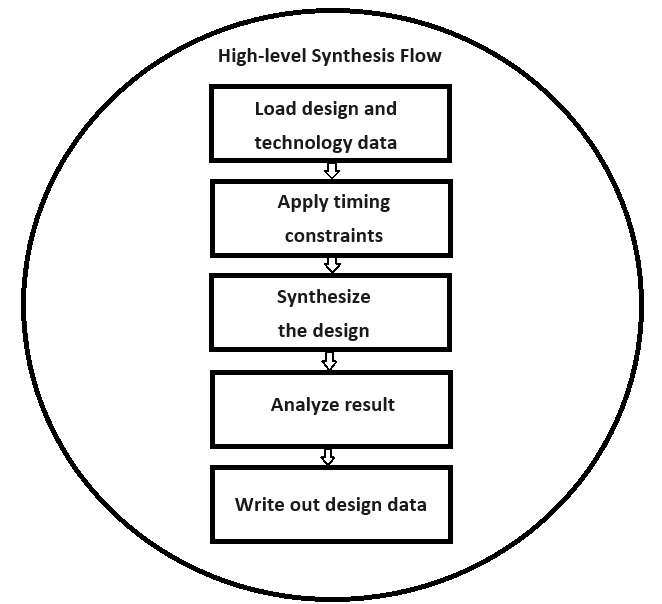

High-Level Synthesis Flow

- Load design and technology data

- Apply timing constraints

- Synthesize the design

- Analyze results

- Write out design data

Synthesis Transformations

- Translate (read_verilog, read_vhdl, read_sverilog)

-

기능 : RTL 소스를 읽어들여 논리적 표현으로 변환합니다.

read_verilog: Verilog로 작성된 RTL 소스를 읽어들입니다.read_vhdl: VHDL로 작성된 RTL 소스를 읽어들입니다.read_sverilog: SystemVerilog로 작성된 RTL 소스를 읽어들입니다.

이 과정에서는 RTL 소스가 GTECH 형태의 일반적인 불린 게이트로 변환됩니다. 이 상태는 아직 특정 기술 라이브러리와 매핑되지 않은 상태(unmapped ddc format)이라고 합니다.

* GTECH: GTECH(Gate Technology) 라이브러리는 논리 합성 도구가 사용하는 기본 게이트 라이브러리입니다. 이는 특정 기술에 종속되지 않으며, 기술 매핑 전에 사용됩니다.

** mapped ddc format: 이는 특정 기술 라이브러리에 매핑된 형태의 넷리스트를 나타냅니다. 여기에는 특정 제조 공정에 맞는 게이트들이 포함됩니다.

- Constrain (source)

-

기능 : 설계에 대한 제약 조건을 설정합니다.

set_max_area: 설계의 최대 면적을 설정합니다.create_clock: 클럭 신호를 정의합니다.set_input_delay: 입력 신호의 지연을 설정합니다.

- Optimize + Map (compile_ultra)

- 기능: 설계를 최적화하고 기술 라이브러리와 매핑합니다.

compile_ultra: 이 명령은 최적화와 매핑을 수행하여 논리적 게이트를 기술 라이브러리의 구체적인 게이트로 변환합니다.

이 과정에서 생성되는 결과는 mapped ddc format이라고 하며, 이는 기술별 게이트로 매핑된 넷리스트입니다. 이 단계에서 설계의 성능, 면적, 전력 소비 등이 최적화됩니다.

- Save (write -f ddc)

-

기능: 합성된 설계를 파일로 저장합니다.

write_icc2_files: ICC2(Physical Design Tool)에서 사용할 수 있도록 파일을 저장합니다.

이 과정은 최적화되고 매핑된 설계를 물리적 설계 도구에서 사용할 수 있도록 하기 위한 것입니다. 최종적으로 생성된 파일은 칩 제조를 위한 GDSII 파일 생성에 사용됩니다.

**write_icc2_files : 이 명령어는 합성된 설계를 ICC2(Integrity Chapter 2, Synopsys의 물리적 설계 도구) 형식으로 저장하여 물리적 설계 도구에서 사용할 수 있도록 합니다.

Two Modes for RCs

WLM (Weighted Load Model) Mode

- 특징: 배선의 영향을 모델링하기 위해 가중치된 부하 모델 사용, 실제 배선 경로를 고려하지 않고, 통계적 또는 경험적 데이터를 기반으로 배선의 부하를 추정합니다.

- 장점: 빠른 계산이 가능하여 복잡한 배선 경로를 시뮬레이션하지 않습니다.

- 용도: 초기 설계 단계에서 유용하며, 빠르게 타이밍 분석을 수행할 수 있어서 대략적인 설계 검증에 유리합니다.

- 단점: 정확도가 떨어질 수 있습니다.

over-buffered gate: 필요 이상으로 많은 버퍼가 추가되어 회로의 면적과 전력 소비가 증가합니다.

under-buffered gate: 필요한 버퍼가 충분히 추가되지 않아 타이밍 문제나 신호 전달 문제가 발생할 수 있습니다.

- Pre-Layout

Pre-layout 단계는 실제 물리적 레이아웃이 생성되기 전의 설계 단계를 의미합니다. 이 단계에서는 논리 설계와 합성이 주로 이루어집니다.

- 논리 합성: RTL (Register Transfer Level) 소스를 사용하여 게이트 수준의 넷리스트를 생성합니다.

- 초기 타이밍 분석: WLM (Weighted Load Model) 또는 추정된 RC 모델을 사용하여 타이밍 분석을 수행합니다.

- 설계 검증: 기능적 검증과 기본적인 타이밍 검증을 수행합니다.

- 제약 조건 설정: 설계 목표에 따라 타이밍, 전력, 면적 등의 제약 조건을 설정합니다.

- 빠른 피드백: 설계의 초기 검증 단계로, 빠르게 피드백을 받을 수 있어 설계 수정이 용이합니다.

Topographical Mode

- 특징 : 실제 레이아웃 정보와 유사한 방식으로 배선 모델링하여 타이밍 분석 수행, 실제 배선 경로를 반영합니다. Design Compiler Ultra(DC Ultra)에서만 사용할 수 있습니다.

- DC Ultra: coarse placement를 수행하여 congestion-aware routing을 하고 이를 기반으로 RC 값을 계산합니다.

- 장점: 정확도가 높고, 물리적 레이아웃의 제약과 특성을 고려하여 최종 레이아웃에 근접한 분석 결과를 얻을 수 있습니다. -> 타이밍과 면적이 pre-layout에 비해 좋아질 수 있습니다.

- 단점: WLM 모드에 비해 계산 시간이 길어질 수 있습니다.

- Post-Layout

Post-layout 단계는 실제 물리적 레이아웃이 생성된 후의 설계 단계를 의미합니다. 이 단계에서는 레이아웃을 기반으로 한 정확한 타이밍 분석과 검증이 이루어집니다.- 물리적 설계: 셀 배치(placement), 배선(routing), 클럭 트리 합성(CTS) 등이 이루어집니다.

- 정밀 타이밍 분석: 실제 배선 경로와 RC 추출을 기반으로 타이밍 분석을 수행합니다.

- 전력 분석: 실제 배선 길이를 고려한 전력 분석을 수행합니다.

- 신호 무결성 검증: 신호 지연, 교차 간섭 등의 신호 무결성 문제를 검증합니다.

- Post-Layout

한줄요약

WLM mode : 초기 설계 단계에서 빠른 검증을 위해 사용되며, 정확도가 떨어질 수 있지만 시간이 절약됩니다.

Topographical mode : 실제 레이아웃을 반영하여 정확한 타이밍 분석을 수행하며, 최종 설계에 근접한 결과를 얻을 수 있지만, 계산 시간이 더 오래 걸립니다.

DC_Shell & Design Vision & Topographical Mode

- DC Shell 및 Design Vision: Design Compiler의 인터페이스로, 사용자가 Design Compiler를 어떻게 사용할지를 정의.

- DC Shell: 명령줄 인터페이스.

- Design Vision: 그래픽 사용자 인터페이스.

- Topographical Mode: Design Compiler의 작동 모드로, 설계의 정확한 타이밍 분석 및 최적화를 위한 설정.

DC Shell과 Design Vision은 Design Compiler를 사용하기 위한 두 가지 다른 인터페이스입니다.

Topographical Mode는 Design Compiler에서 실제 레이아웃을 반영한 정확한 타이밍 분석을 수행하기 위한 작동 모드입니다.

Topographical Mode는 DC Shell이나 Design Vision에서 사용할 수 있으며, 둘 중 어느 인터페이스를 사용하더라도 모드를 설정할 수 있습니다.

따라서, DC Shell과 Design Vision은 인터페이스의 종류이고, Topographical Mode는 작동 모드입니다. 이 둘은 같은 것이 아니라, 상호 보완적으로 사용됩니다.