STA & DTA

Static Timing Analysis (STA)

- 시뮬레이션 불필요: 입력 벡터가 필요 없으며, 논리 경로에 대한 모든 가능한 타이밍 조합을 분석.

- 빠른 속도: 대규모 회로에서도 효율적.

- 경로 기반 분석: 최대 경로 지연(Critical Path) 및 최소 경로 지연(Setup/Hold Time Violation)을 수학적으로 검토.

- Setup Time Check: 클럭 주기 내에 데이터가 안정적으로 도달하는지 확인.

- Hold Time Check: 데이터가 너무 빨리 도착해 충돌하지 않는지 확인.

Dynamic Timing Analysis (DTA)

- 입력 벡터 필요: 분석하려면 테스트 벡터(입출력 데이터 패턴)가 필요합니다.

- 정확성 높음: 실제 회로 동작을 반영하며, 글리치, 노이즈, 다이내믹 효과를 포함한 복잡한 타이밍 문제를 확인.

- 느림: 입력 벡터를 기반으로 하기 때문에 대규모 회로에서는 시간이 많이 소요될 수 있습니다.

CONCLUSTION

-> STA는 회로 설계 초기에 사용되어 전체적인 타이밍 문제를 빠르게 검출하고 수정하는 데 유용.

-> DTA는 설계의 최종 단계에서 실제 회로 동작을 정밀히 검증하거나 STA에서 발견되지 않은 문제를 확인하는 데 사용.

Asynchronous VS Synchronous

Synchronous (동기식)

- 하나의 마스터 클럭 신호를 공유하는 모든 블록이 동일한 클럭 도메인 내에서 동작.

- 클럭 에지가 기준이 되어 데이터 전송 및 처리가 이루어지므로, 타이밍 분석이 상대적으로 단순.

- 모든 플립플롭의 클럭 입력은 동일한 클럭 소스(마스터)를 사용.

장점

- 하나의 마스터 클럭 신호를 공유하는 모든 블록이 동일한 클럭 도메인 내에서 동작.

- 클럭 에지가 기준이 되어 데이터 전송 및 처리하므로, 타이밍 분석이 상대적으로 단순.

- 모든 플립플롭의 클럭 입력은 동일한 클럭 소스(마스터)를 사용.

주의할점

- clock skew와 jitter를 최소화해야함.

- 클럭 트리 구조를 최적화하여 타이밍 문제를 방지.

결론

글로벌 클럭에 의존하며 타이밍 분석으로 STA로 정적 분석 가능.

Asynchronous (비동기식)

각 블록이 다른 마스터 클럭(또는 오실레이터)에 의해 동작하거나, 클럭 자체 없이 핸드쉐이크와 같은 신호를 기반으로 동작.

클럭 도메인이 다르기 때문에 데이터 전송 시 Metastability와 같은 타이밍 문제가 발생.

장점

- 전력 효율이 높음.

- 클럭이 필요 없는 시스템에서는 간단한 구현 가능.

주의할점

- 클럭 도메인 간 전환 시 CDC (Clock Domain Crossing) 문제를 해결해야함.

- STA만으로는 분석이 어렵고, 시뮬레이션이나 Formal Verification이 필요.

edge delay가 불확실하므로 타이밍 안정성을 보장하기 위해 추가 설계 기법(ex) 동기화 플립플롭)이 필요.

-> Asynchronous은 플립플롭을 구동하는 신호는 edge delay를 모르기에 모든 포트에 대해서 반드시 클럭으로 선언해야 안정성을 보장할 수 있음.

명령어 create_clock -name <clock_name> -period <period_value> <clock_pin_or_port>

- name <clock_name>: 클럭의 이름을 지정합니다.

- period <period_value>: 클럭 주기를 지정합니다(단위는 ns).

- <clock_pin_or_port>: 클럭으로 선언할 신호(포트 또는 핀).

DAT & DRT

Data Arrival Time (DAT)

Data Arrival Time (DAT) : 데이터가 특정 경로를 따라 도착하는 시간

플립플롭이나 게이트의 입력으로 데이터가 도착하는 시간을 계산하는 것으로, 주로 지연 시간(delay)을 기반으로 산출

구성

- Launch Clock Edge: 클럭 신호가 활성화된 순간.

- Combinational Path Delay: 데이터가 조합 논리 경로를 통과하는 데 걸리는 시간.

Data Required Time (DRT)

Data Required Time (DRT) : 데이터가 특정 경로의 종료점에 도달하기 위해 요구되는 시간

주로 Setup Time과 클럭 도메인을 기준으로 계산

구성

- Capture Clock Edge: 데이터가 캡처되는 클럭 엣지.

- Setup Time Requirement: 데이터가 안정적으로 캡처되기 위해 요구되는 시간.

RELATION

기본조건

- DAT≤DRT => Slack (hold report에서는 반대!)

데이터 도착 시간이 요구 시간보다 작거나 같아야 타이밍 위반이 발생 X

위반시,

- Setup Violation:

DAT>DRT인 경우, 데이터가 너무 늦게 도착하여 클럭 주기 내에 안정적으로 캡처되지 않음.- Hold Violation:

데이터가 너무 빨리 도착하여 이전 데이터가 안정적으로 유지되지 못함.

이 경우는 Hold Time을 기준으로 추가 분석이 필요.

예제

클럭 주기: 10ns, 조합 논리 지연: 7ns, Setup Time: 2ns 일 때,

계산

DAT=0+7=7ns

DRT=10-8=2ns

- DAT(7ns)≤DRT(8ns)이므로 타이밍 위반 없음.

OCV

On Chip Variation (OCV)

PVT로 인해 발생하는 지연 시간 및 전기적 특성의 변동을 의미

- 프로세스 변동 (Process Variation)

- 전압 변동 (Voltage Variation)

- 온도 변동 (Temperature Variation)

그래서, 모델링이 필요!

OCV를 모델링 방법

- Worst-Case Analysis

칩 내 모든 요소가 가장 느리거나 가장 빠르게 동작한다고 가정.

보수적이지만 설계 최적화에는 비효율적일 수 있음.- Derating Factor

OCV를 반영하기 위해 타이밍 경로에 스케일링 계수를 적용.

EX) 느린 경로에는 1.1배, 빠른 경로에는 0.9배의 지연 시간 적용.- AOCV (Advanced OCV)

경로 길이와 위치에 따라 OCV 변동을 더 정밀하게 모델링.

짧은 경로는 상대적으로 작은 변동, 긴 경로는 더 큰 변동을 적용.- POCV (Parametric OCV)

공정 및 환경 요인을 통계적으로 모델링.

변동성을 수학적으로 계산하여 더 현실적인 타이밍 분석 수행.

결론

- DAT(데이터가 출발점(Launch Path)에서 시작하여 종료점(Capture Point)에 도달하는 실제 시간)가 클수록 Worst.

-> Launch Path Delay가 길어질수록 데이터가 늦게 도착하여 Setup Time Violation의 가능성이 증가하므로 타이밍 경로의 Critical Path(가장 긴 지연 경로)를 찾아 분석하는 것이 중요함.- DRT(데이터가 안정적으로 캡처되기 위해 최소한 도착해야 하는 시간)는 데이터는 반드시 DRT보다 빠르게 도착해야 타이밍 위반이 발생하지 않음.

- Capture Path(캡처 포인트에서 플립플롭 또는 출력 포트로 데이터를 전송하는 경로)는 작을수록 Worst.

-> Capture Path Delay가 작을수록 DRT가 줄어들어 타이밍 요구사항이 더 엄격해지므로 Setup Time Violation 가능성을 높임.- EX)

-> 긴 Capture Path Delay: 여유로운 타이밍 경로로 인해 데이터가 도착해야 하는 시간이 늦춰짐.

-> 짧은 Capture Path Delay: 데이터가 더 빨리 도착해야 하므로 경로가 더 타이트해짐.

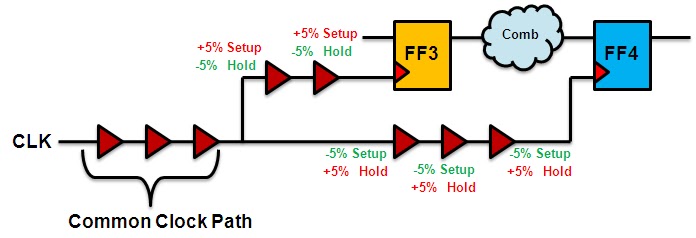

CRP(Clock Reconvergence Pessimism)

- 클럭 신호가 여러 경로로 분기되었다가 동일한 지점에서 다시 합쳐질 때 발생하는 분석상의 보수적 오류(pessimism)

- STA에서 클럭 도착 시간을 분석할 때, 동일한 클럭 소스에서 유래한 신호임에도 불구하고 분기 후의 경로에서 지연 분석이 과도하게 보수적으로 계산되는 현상

// Launch & Capture가 공통경로에서 일어난 차이

한 path내에 어떤 때에는 매우 작은 delay가 걸릴 때가 있고, 큰 delay가 걸리는 것에 대해 derate를 준 이후에 생기는 과정인가?

CRP 보정 방법 : CRPR(Common Reconvergence Pessimism Removal)을 통해 공통 지연 중복 제거.

** CRPR 주의점 : Common Point가 이론적으로 0이어야 하며, delay 차이가 나면 안됨.

타이밍 분석에 미치는 영향 보정되지 않으면 Setup/Hold Violation 가능성을 과대평가하거나 Slack이 왜곡될 수 있음.

++ frontend eng에서