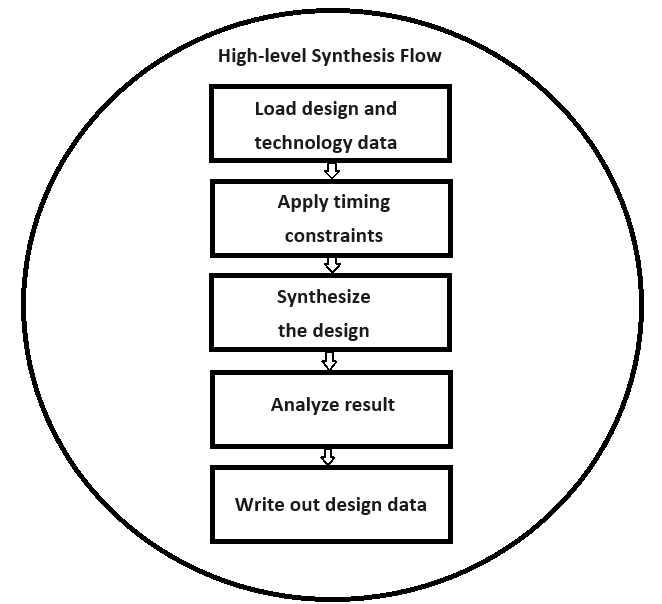

High-Level Synthesis Flow

- Load design and technology data

- Apply timing constraints

- Synthesize the design

- Analyze results

- Write out design data

Timing Path

- Startpoint

- Input port

- Clock pin of F/F or register

- Endpoint

- Output port

- D Pin (Any input pin of a sequential device, except clock pin)

Constraining Register-to-Register(R2R) Paths

What information must you provide to constrain all the R2R paths in MY_DESIGN for setup time?

-> DC automatically calculates the maximum delay for the path, starting at the clock pin of FF2 and ending at the D-pin of FF3, as 10 - 1 = 9ns.

Ex) Spec: Clock Period = 2ns, Tsetup = 0.2ns

-> Treg-to-reg, max = P - Setup_Time (assuming 0 clock skew) = 2 - 0.2 = 1.8ns

You should verify the unit of time by looking at the top of the report generated by report_lib [library_name]