Demand Paging의 Direct Paging 기법의 솔루션으로, Associative Mapping 외의 다른 방법에 대해 알아보자!

(1) Associative Mapping (Translation Look-aisde Buffer)

(2) PMT를 dedicated Register나 캐시 메모리에 저장

1. Page-table Registers

cpu register의 일부를 PMT를 저장하는 용도로 이용한다.

실제 PMT의 일부를 저장하는 것 외에도, Real Address 만드는 과정을 빠르게 하도록 과정 자체를 지원하는 로직을 갖는 레지스터일수도 있다.

➡ 프로세스의 Context Switching 때에 Page-table Registers 값까지 그 switching 대상이 되어야 한다.

➡ 페이지 테이블이 아주 작을 때에는 페이지 테이블 레지스터에 전체 모두 넣을 수 있겠지만, 크기가 아주 클 때에는 페이지 테이블 레지스터는 빠른 Computation까지 가능한 수준으로 만드는 것이 좋다.

2. Page Table의 크기와 관련된 이슈

1) Hierarchical Paging (Multi Level Paging)

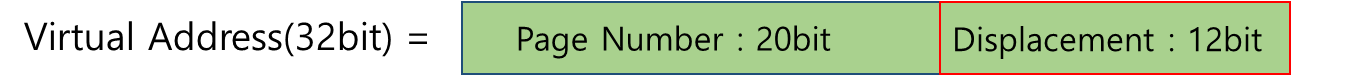

Virtual Address가 32bit이고, page 크기가 4KB인 경우, 위와 같이 구성된다.

Page 번호가 20bit이면 페이지 개수가 2의 20승개이고, 약 100만개인데 이 경우 페이지 맵 테이블의 엔트리가 100만개로서 크기가 매우 클 것이다.

따라서 Hierarchical Paging 을 이용할 수 있다.

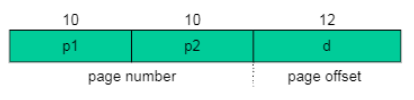

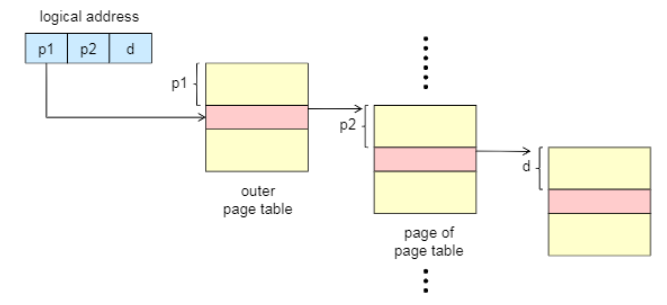

Example. 2-Level Paging

앞쪽 페이지 번호와 뒷쪽 페이지 번호로 분리한다.

p1은 outer page table이며, 0부터 1023까지의 entry가 오게 된다.

그리고 그 각각의 entry에 대해서 page of page table이 1024개 존재한다.

page map table에 대한 virtual memory 라고 생각하면 된다! (즉, page map table을 다시 paging 한 것)

2) Inverted Page Table

기존 개념 : 프로세스마다 페이지 테이블을 하나씩 갖는다.

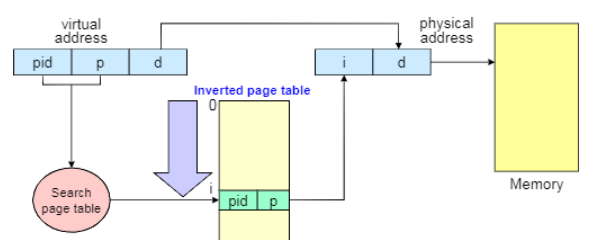

Inverted Page Table 이 개념은 시스템 전체에서 오직 하나의 major page table이 존재한다.

Physical Memory에 페이지 프레임들이 있을 때, inverted page table도 m개로 나뉘어 있다.

즉 Page Table이 페이지에 대한 것이 아니라 페이지 프레임에 대한 정보를 저장한다.

i번은 i번 페이지 프레임에 어떤 프로세스가 들어와 있는지 프로세스 id와 페이지 번호를 저장한다.

따라서 Virtual Address generation은 (p, d)로 되어 있는데 p번 페이지가 메모리에 들어와 있는지를 봐야 한다.

이 때 inverted page table에서 pid와 p 쌍에 대해서 해당 페이지가 들어와있는지 일일이 탐색해야 한다.

발견되면 page frame number인 i를 뽑아내고, physical address를 찾을 수 있다.

📌 즉, page table로 인한 공간을 줄이는 대신 address mapping의 시간이 늘어난다.

❗ 더불어 search를 했을 때 해당 (pid, p) 조합을 찾을 수 없는 경우에는 page fault인데 이 경우 매우 복잡해진다.

특정 프로세스의 virtual address space에 대한 완벽한 정보를 갖고 있지 않기 때문이다.

👇 해결방법

External Page Table을 따로 만들어서 page fault가 발생할 때마다 이 테이블을 접근하게 한다. 그러나 이 경우 또 다른 page table을 만든다는 점에서 단점이 있다.