🥔 Page Table이란?

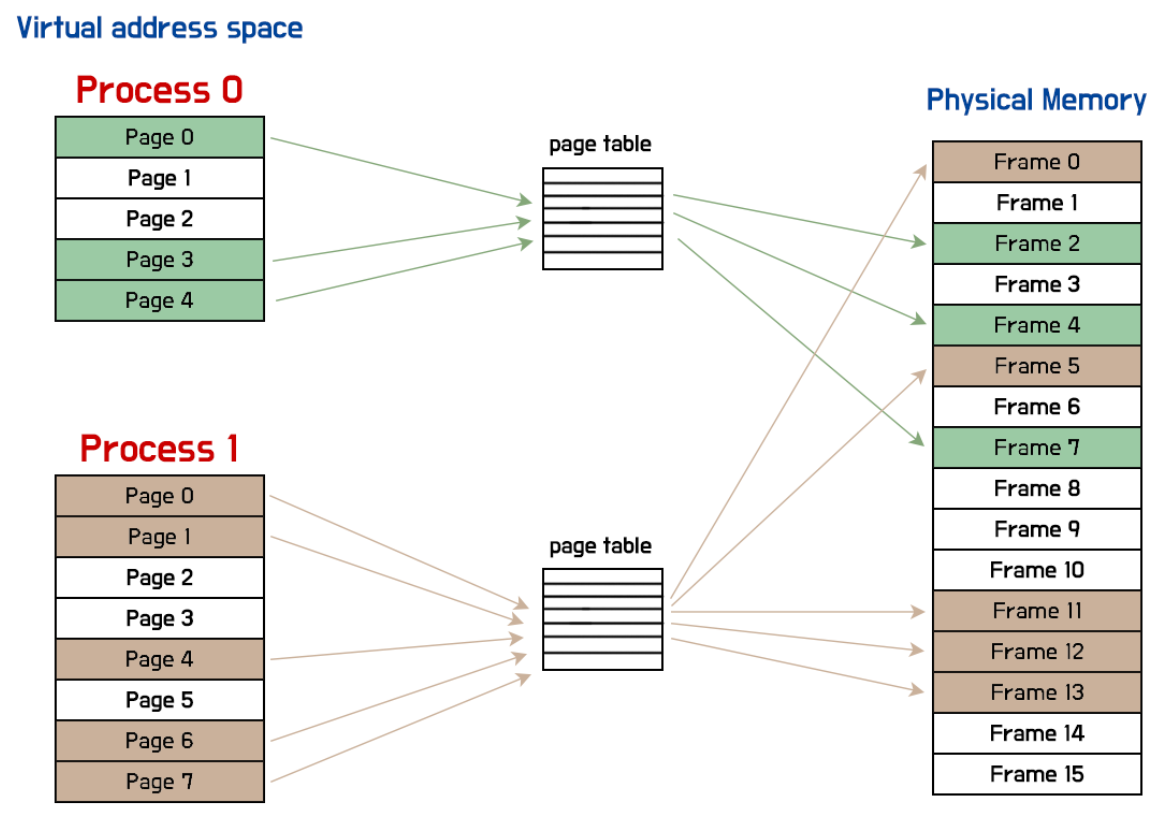

운영체제에서 가상 메모리(Virtual Memory) 를 사용하는 시스템은 CPU가 직접 물리 주소를 다루지 않는다. 대신, 가상 주소(Virtual Address) 를 물리 주소(Physical Address) 로 변환해주는 장치가 필요한데, 이 역할을 하는 것이 바로 페이지 테이블(Page Table) 이다.

페이지 테이블은 가상 주소 공간을 페이지 단위로 나누어, 각 페이지가 어떤 물리 프레임에 매핑되어 있는지를 기록하는 변환 테이블이다.

🥔 왜 페이지 테이블이 필요한가?

현대 OS는 다음과 같은 이유로 가상 메모리를 사용한다:

- 프로세스 간 메모리 격리: 각 프로세스는 독립된 주소 공간을 갖는다.

- 효율적 메모리 관리: 실제 사용된 메모리만 물리적으로 매핑한다.

- 보안성: 사용자 프로그램이 커널 영역에 접근하지 못하게 막는다.

- 추상화: 프로세스 입장에서 메모리는 연속적이며 무제한인 것처럼 보인다.

이러한 추상화는 페이지 테이블이 실질적으로 구현해낸다.

🥔 가상 주소 → 물리 주소 변환 과정

- CPU는 가상 주소를 생성한다.

- MMU (Memory Management Unit) 는 가상 주소의 페이지 번호(Page Number) 를 추출한다.

- 페이지 테이블에서 해당 페이지가 매핑된 프레임 번호(Frame Number) 를 조회한다.

- 페이지 오프셋을 붙여 물리 주소를 계산한다.

[Virtual Address] → [Page Number | Offset]

→ Page Table lookup

→ [Frame Number | Offset] → Physical Address🥔 페이지 테이블 구조

페이지 테이블은 보통 배열 형태로 구현되며, 각 Page Table Entry (PTE) 는 다음과 같은 정보를 포함한다:

| 필드 | 설명 |

|---|---|

| Frame Number | 매핑된 물리 프레임 번호 |

| Present Bit | 해당 페이지가 메모리에 존재하는지 여부 |

| Read/Write Bit | 읽기/쓰기 권한 |

| User/Supervisor Bit | 사용자/커널 접근 권한 |

| Dirty Bit | 페이지가 수정되었는지 여부 |

| Accessed Bit | 최근 접근 여부 (LRU 등 교체 알고리즘용) |

시스템에 따라 PTE는 32비트 또는 64비트로 구성된다.

🥔 계층적 페이지 테이블 (Multi-level Page Table)

가상 주소 공간이 커질수록 단일 테이블로는 너무 많은 메모리를 차지하게 된다. 이를 해결하기 위해 계층적(다단계) 페이지 테이블 구조가 사용된다.

예: x86-64 시스템의 4단계 페이지 테이블 구조

- PML4 (Page Map Level 4)

- PDPT (Page Directory Pointer Table)

- PD (Page Directory)

- PT (Page Table)

가상 주소 → [PML4] → [PDPT] → [PD] → [PT] → 물리 프레임페이지 테이블 간 이동은 메모리 참조로 이루어지므로, TLB (Translation Lookaside Buffer) 를 사용해 성능을 보완한다.

🥔 페이지 테이블의 메모리 비용 문제

32비트 주소 공간을 4KB 페이지 단위로 나누면 다음과 같다:

- 페이지 수 = 2³² / 2¹² = 2²⁰ (약 100만 개)

- 각 엔트리가 4바이트면 전체 페이지 테이블 크기 = 4MB

프로세스마다 별도의 페이지 테이블이 필요하므로, 많은 프로세스를 지원하려면 다단계 테이블 또는 역방향 페이지 테이블(Inverted Page Table) 이 필요하다.

🥔 CPU와 페이지 테이블

CPU는 현재 활성화된 페이지 테이블의 물리 주소를 특정 레지스터에 보관한다:

- x86:

CR3레지스터에 루트 페이지 테이블(PML4)의 물리 주소 저장 - ARM:

TTBR(Translation Table Base Register)

문맥 전환(Context Switching) 시 CR3도 함께 바뀌며, 이로 인해 TLB도 flush 된다.

🥔 페이지 테이블과 페이지 폴트

페이지 테이블에 present bit = 0 이면, 해당 가상 주소는 아직 물리 메모리에 매핑되지 않았다.

→ 이때 CPU는 Page Fault Exception 을 발생시키고,

→ 운영체제가 디스크에서 페이지를 로딩하고,

→ 페이지 테이블을 갱신한 뒤,

→ Fault가 발생한 명령어를 재실행한다.

🥔 TLB와의 관계

TLB (Translation Lookaside Buffer) 는 최근 사용된 가상 주소 → 물리 주소 변환 정보를 캐싱하는 메모리다.

- TLB Miss → 페이지 테이블을 직접 조회

- TLB Hit → 빠르게 주소 변환 수행

CR3변경 (Context Switch) → TLB Flush

페이지 테이블은 느리기 때문에, 성능을 위해 TLB의 역할이 매우 중요하다.

🥔 정리

- 페이지 테이블은 가상 주소 → 물리 주소 매핑 테이블이다.

- 각 PTE는 프레임 번호와 접근 권한 등의 정보를 담고 있다.

- 주소 공간이 커지면 다단계 페이지 테이블로 구조를 최적화한다.

- TLB와 함께 동작하여 주소 변환을 빠르게 수행한다.

CR3는 현재 페이지 테이블의 위치를 나타내며, 문맥 전환 시 함께 갱신된다.