🥔 TLB란?

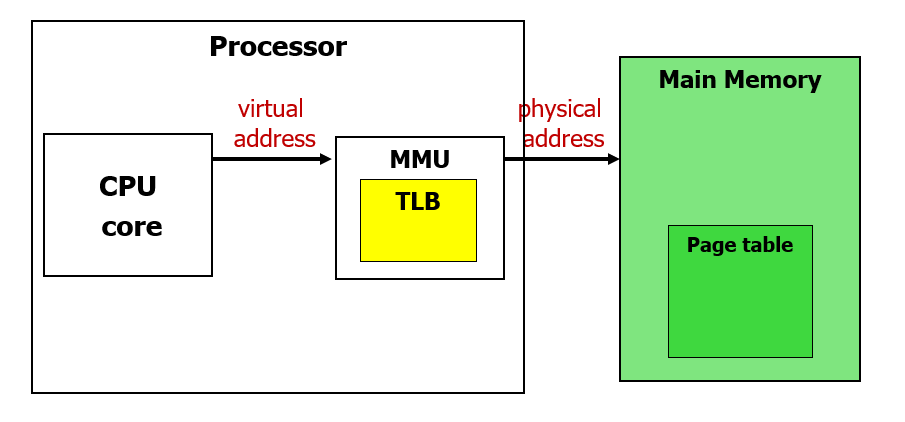

TLB(Translation Lookaside Buffer) 는 가상 주소를 물리 주소로 빠르게 변환하기 위해 사용하는 캐시 메모리다.

페이지 테이블을 매번 참조하면 느리기 때문에, 최근에 사용한 주소 변환 정보를 TLB에 저장하여 성능을 개선한다.

🥔 가상 주소 변환의 문제점

가상 메모리 시스템에서는 CPU가 사용하는 주소는 모두 가상 주소(Virtual Address) 이다. 이를 실제 물리 메모리 주소로 변환하기 위해 페이지 테이블(Page Table) 을 사용한다.

하지만 페이지 테이블은 메인 메모리에 위치하므로, 주소를 변환할 때마다 메모리를 접근해야 하며, 이는 성능 저하를 유발한다.

🥔 TLB의 역할

TLB는 페이지 테이블의 일부분을 캐시 형태로 보관한다.

최근에 변환한 가상 주소 ↔ 물리 주소 매핑을 저장함으로써 페이지 테이블 접근 없이 주소를 변환할 수 있다.

CPU가 주소를 참조할 때, 먼저 TLB를 확인하고(TLB hit), 없다면 페이지 테이블을 검색한다(TLB miss).

🥔 TLB 작동 흐름

-

CPU가 가상 주소를 생성

-

MMU(Memory Management Unit)가 TLB에서 해당 페이지 번호를 탐색

-

TLB hit: 바로 물리 주소 반환

-

TLB miss:

- 페이지 테이블 참조하여 물리 주소 획득

- 해당 매핑을 TLB에 캐시 (교체 정책에 따라 갱신)

🥔 TLB 구조

TLB는 다음과 같은 정보를 저장한다:

| 필드 | 설명 |

|---|---|

| 가상 페이지 번호 | Virtual Page Number |

| 물리 프레임 번호 | Physical Frame Number |

| 접근 권한 | 읽기/쓰기 등 권한 정보 |

| 유효 비트 | 유효한 엔트리인지 표시 |

| 참조 비트 / 사용 비트 | 교체 정책에 사용됨 |

🥔 TLB 교체 정책

TLB는 한정된 엔트리 수를 가지므로, 새로운 항목을 넣기 위해 기존 항목을 교체해야 한다.

대표적인 교체 알고리즘:

- LRU (Least Recently Used): 가장 오래 사용되지 않은 항목 제거

- FIFO (First-In First-Out): 가장 먼저 들어온 항목 제거

- Random: 무작위로 제거

🥔 TLB Miss의 종류

| 종류 | 설명 |

|---|---|

| Soft Miss | 프로세스가 사용하는 페이지지만, TLB에는 없음 (→ Page Table에서 가져옴) |

| Hard Miss | 프로세스가 한 번도 접근하지 않은 페이지 (→ Page Fault 발생) |

🥔 TLB와 Context Switching

프로세스가 전환될 때, 다른 프로세스의 주소 공간을 사용하므로 기존 TLB 정보는 무효화(invalidate) 해야 한다.

이를 해결하기 위한 방법:

- TLB flush: 모든 엔트리 초기화

- Address Space Identifier (ASID): 프로세스 식별자를 TLB에 함께 저장 → flush 없이 다중 프로세스 지원 가능

🥔 TLB와 성능

TLB hit 비율이 높을수록 성능이 향상된다.

성능 관련 공식:

Effective Memory Access Time =

(Hit Ratio × TLB Access Time) +

(Miss Ratio × (TLB Access Time + Page Table Access Time))예를 들어, TLB hit이 99%이고 TLB 접근이 1ns, Page Table 접근이 100ns라면 실질적인 접근 시간은 매우 빨라진다.

🥔 TLB 요약

| 항목 | 내용 |

|---|---|

| 목적 | 가상주소 → 물리주소 변환 속도 향상 |

| 위치 | MMU 내부 |

| 작동 방식 | 최근 주소 매핑을 캐싱 |

| Miss 발생 시 | 페이지 테이블 or 페이지 폴트 |

| 교체 알고리즘 | LRU, FIFO 등 |

| Context Switching | TLB flush or ASID 필요 |

🥔 마무리

TLB는 가상 메모리 주소 변환의 병목을 줄이는 핵심 요소이며, 운영체제와 하드웨어가 함께 관리해야 하는 중요 구성 요소다.

CPU, MMU, 페이지 테이블, TLB는 함께 작동하여 효율적인 메모리 주소 변환 시스템을 구성한다.