1. ATMEGA 128 칩

1984년 설립된 ATMEL사에서 만든 8비트 AVR로 총 64핀으로 구성되어 있다.

내부적으로 RISC구조로 이루어져 있어 대부분 1클럭에서 수행되는 어셈블리어 명령어를 가지고 있다.

● 개선된 RISC 구조

- 고성능, 저전력 8비트 마이크로컨트롤러

- 파이프라인을 통해 대부분 1클럭에서 실행

- 16Mz에서 16MIPS(Mega Instruction Per Operation) 처리율

- 32개의 8비트 범용 레지스터와 주변장치 제어를 위한 전용 레지스터를 가짐

- 시간의 흐름에따라 신호가 변하는 DRAM(Dynamic Random Access Memory)과 달리 잘 변하지 않는 SRAM(Static Random Access Memory)을 사용하여 안정적인 동작을 유지

● 다양한 메모리

- 128KB의 비휘발성 플래시 프로그램 메모리를 가지고 있어 10,000회 R/W를 보장

- 4KB의 비휘발성 EEPROM(100,000회 R/W 보장)

- 4KB 휘발정 SRAM

- 플레시 메모리 내의 데이터 보안을 위한 잠금 비트(lock bit)가능

- SPI(Serial Peripheral Interface)를 통한 프로그래밍 가능 (ISP or ICSP라고 한다)

● JTAG 지원

- JTAG(Joint Test Action Group) 표준을 지원. 하드웨어를 테스트하는 방법에 관한표준이다,

- JTAG를 사용한 하드웨어 테스트를 통해 프로그램을 마이크로컨트롤러에서 실행 시키면서 디버깅이 가능하다. 이를 온-칩 디버깅(on-chip debugging)이라 한다. 실제 마이크로컨트롤러 없이 수행할 수 있게 해주눈 도구가 에뮬레이터(emulator)이다. 하지만 실제 환경과 동일하게 구현하기에는 어려움이 있다.

- JTAG 인터페이스를 통한 Flash, EEPROM, 퓨즈, lock 비트 내용 변경가능

● 주변 장치

- 2개의 8비트 타이머/카운터와 2개의 16비트 타이머/카운터를 가지고 있다

- 독립된 오실레이터(Oscillatros-반복적인 또는 주기적인 시간 변화 신호를 생성하는 전자 회로)로 동작시킬 수 있는 실시간 카운터(Real Time Counter, RTC)를 가지고 있다

- 2개의 8비트 PWM(Pulse Width Modulation- 펄스 폭 변조)를 가지고 있다

- 2~16비트로 설정 가능한 6개의 PWM 채널을 가지고 있다

- 8채널 10비트 ADC를 가지고 있다 8개중 7개는 차동 입력이 가능하며, 8개중 2개 채널은 최대 200배의 이득(gain)을 설정할 수 있다.

- 바이트 기반의 TWI(Two Wire Interface)를 지원한다. TWI는 칩 제조사에서 사용하는 I2C(Inter Intergrated Circuit)의 다른 이름이다.

- 2개의 USART(Universal Synchronous/Asynchronous Receiver Transmitter)를 지원한다

- SPI 지원

- 별도의 오실레이터로 동작하는 워치도그(watchdog) 타이머를 가지고 있다

- 하드웨어로 구현한 아날로그 비교기를 가지고 있다

● 주변 장치

- 충분한 전력이 공급되고 있는지를 감지하느 브라운아웃 감지기능 제공

- 내부 오실레이터를 가지고 있어 외부 클럭의 공급 없이도 동작 가능

- 다양한 인터럽드 제공

- 사용 전력 제어가 가능하도록 여섯 가지의 슬립모드 제공

- 소프트웨어적으로 클로 주파수 제어가능

- 각 핀의 풀업 저항 개별 제어 및 한꺼번에 금지 가능

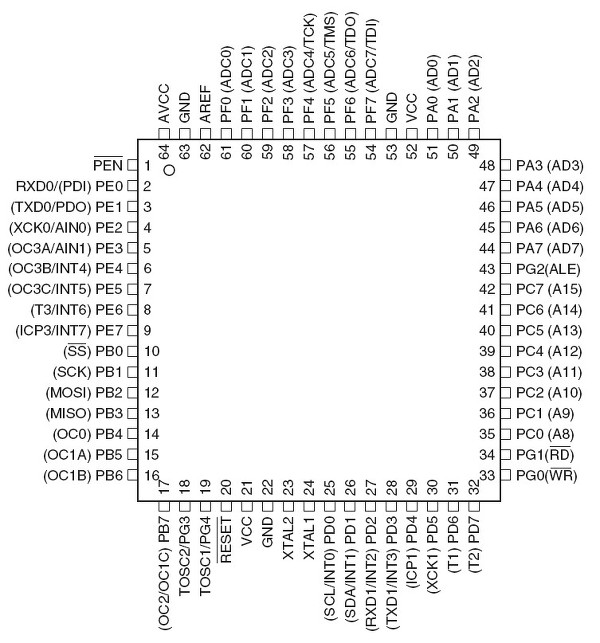

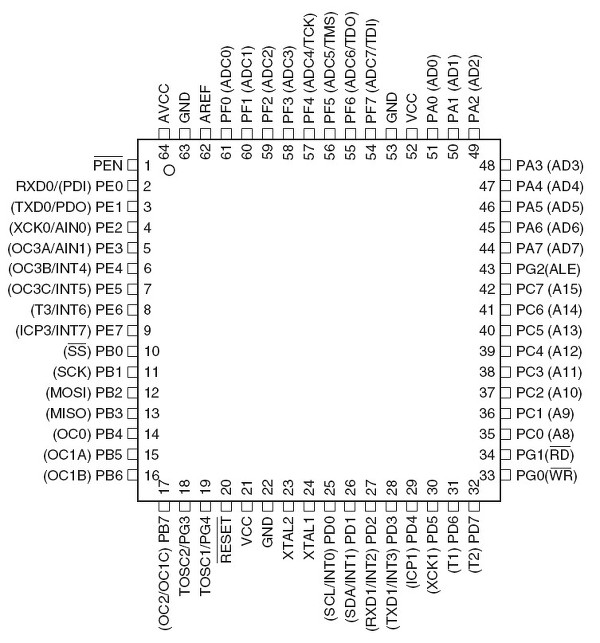

ATMEGA 128 핀 구성

| 용도 | 핀 이름 | 핀 수 | 설명 |

|---|---|---|---|

| 리셋 | RESET | ||

| 포트 | PAn | n=0~7 | |

| 포트 | PBn | n=0~7 | |

| 포트 | PCn | n=0~7 | |

| 포트 | PDn | n=0~7 | |

| 포트 | PEn | n=0~7 | |

| 포트 | PFn | n=0~7 | |

| 포트 | PGn | n=0~4 | |

| 전원 | VCC | ||

| 전원 | GND | ||

| 전원 | AVCC | ADC 및 포트 F에 대한 공급 전압 | |

| 전원 | AREF | ADC 레퍼런스 전압 | |

| 클록 | XTALn | n = 1, 2 | 1: 반전 발진 증폭기 및 내부 클록에 대한 입력 2:반전 발진 증폭기로부터의 출력 |

| 외부 메모리 인터페이스 | ADn | n = 0~7 | 하위 주소 버스 및 데이터 버스 |

| 외부 메모리 인터페이스 | AD | n = 8~15 | 상위 주소 버스 |

| 외부 메모리 인터페이스 | ALE | 외부메모리에 접근할 때 PA에서 출력되는 하위주소값을 래치할 수 있도록 1레벨값을 출력해준다. | |

| 외부 메모리 인터페이스 | RD | 외부 데이터 신호 읽을때 사용되는 스토로브 신호 출력 단자 신호 | |

| 외부 메모리 인터페이스 | WR | 외부데이터 메모리에 쓸때 사용되는 스토로브 신호 출력 단자 신호 | |

| AD 변환기 | ADCn | n = 0~7 | 아날로그 디지털 변환 입력 채널 |

| 아날로그 비교기 | AINn | n = 0, 1 | 로그 디지털 변환 입력 채널 |

| 외부 인터럽트 | INTn | n = 0~7 | 외부 인터럽트 소스 |

| 타이머 카운터 | ICPn | n= 1, 3 | 타이머/카운터 입력 캡처 핀 |

| 타이머 카운터 | OCn | n = 0, 2 | 타이머/카운터 비교일치 혹은 PWM 출력 |

| 타이머 카운터 | OCnX | n = 1, 3 X=A, B, C | 타이머/카운터 비교일치 혹은 PWM 출력 |

| 타이머 카운터 | Tn | n= 1, 2, 3 | 타이머/카운터 외부입력 |

| 타이머 카운터 | TOSCn | n = 1, 2 | 타이머/카운터 오실레이터 핀 |

| 시리얼 프로그래밍 | PDI | 프로그래밍 데이터 입력 | |

| 시리얼 프로그래밍 | PDO | 프로그래밍 데이터 출력 | |

| 시리얼 프로그래밍 | PEN | 프로그래밍 허용 | |

| UART | RXDn | n = 0, 1 | USART 수신 |

| UART | TXDn | n = 0, 1 | USART 송싱 |

| UART | XCKn | n = 0, 1 | USART 외부 클럭 INPUT/OUTPUT |

| SPI | MISO | 마스터 입력 노예 출력 | |

| SPI | MOSI | 마스터 출력 노예 입력 | |

| SPI | SCK | 마스터 디바이스에소의 클럭 발생기 출력 핀 노예 시그널 받는 입력핀 | |

| SPI | SS | or CS 노예 선택 핀 마스터는 노예수만큼 SS 핀을 가진다 | |

| I2C | SCL | 시리얼 클럭 | |

| I2C | SDA | 시리얼 데이터 | |

| JTAG | TCK | JTAG 테스트 클럭 | |

| JTAG | TDI | JTAG 테스트 데이터 입력 | |

| JTAG | TDO | JTAG 테스트 데이터 출력 | |

| JTAG | TMS | JTAG 테스트 모드 선택 |