컴퓨터의 기본 구조

컴퓨터 구조

하드웨어

- 전자 회로 및 기계 장치로 되어 있음

- ex. 입출력 장치, 중앙처리장치(CPU), 기억장치 등

소프트웨어

하드웨어를 제어하며 작업을 수행하는 프로그램

컴퓨터의 기본 구성 요소

입력 장치

- 컴퓨터가 처리할 수 있는 형태로 데이터와 명령을 받아들이는 물리적인 장치

- ex. 마우스, 키보드 등

출력 장치

- 처리된 데이터를 사람이 이해할 수 있는 형태로 출력하는 물리적인 장치

- ex. 모니터, 프린터 등

중앙처리장치(CPU)

- 산술/논리 연산 장치(ALU): 덧셈 수행

- 제어 장치: 프로그램에 따라 명령과 제어 신호를 생성해서 각종 장치의 동작 제어

- 레지스터: CPU의 내부 메모리로, CPU에서 사용하는 데이터를 일시적으로 저장

저장 장치

주기억장치

- 데이터나 프로그램을 보관하기 위한 일차 기억 장치

- 프로그램 수행을 위해 필요한 정보에 비해 중앙처리장치 내에 구비되어 있는 레지스터의 용량이 너무 작기 때문에, 주 기억 장치에 정보를 저장해 두었다가 필요할 때 읽음

- ex. RAM, ROM

보조기억장치

- 주 기억 장치를 보조하는 기억 장치

- 주 기억 장치에 비해 정보를 읽는 속도는 느리지만 대용량의 정보를 저장할 수 있음

- 현재 사용하지 않는 프로그램을 저장

- ex.

- 자기 디스크: 플로피 디스크, 하드 디스크

- 광 디스크: CD, DVD

- 플래쉬 메모리: USB, SSD

CPU

폰 노이만 구조

- 중앙처리장치(CPU), 기억장치(주기억장치, 보조 기억 장치), 입출력장치로 구성

- 중앙처리장치(CPU)를 통해서 연산을 수행하게 되는 구조

- 중앙처리장치(CPU)는 각종 연산을 수행하고 기억장치에 기억되어 있는 명령어들을 수행하는 컴퓨터 시스템을 이루는 핵심 부품

CPU의 구조

레지스터(Register)

- 중앙처리장치(CPU) 내부에 있는 기억장치

- 종류

- 범용 레지스터(General-Purpose Register)

- 주로 산술 연산 논리장치에 의해 사용

- 전용 레지스터(Dedicated-Purpose Register)

- PC 등 특수 목적에 사용

- 범용 레지스터(General-Purpose Register)

- 구성

- IR (Instruction Register)

- 현재 수행 중에 있는 명령어 부호를 저장하고 있는 레지스터

- PC (Program Counter)

- 명령이 저장된 메모리의 주소를 가리키는 레지스터

- AC (Accumulator)

- 산술 및 논리 연산의 결과를 임시로 기억하는 레지스터

- IR (Instruction Register)

산술/논리 연산 장치(Arithmetic Logic Unit, ALU)

- 산술적인 연산과 논리적인 연산을 담당하는 장치

- 가산기, 보수기, 누산기, 기억 레지스터, 데이터 레지스터 등으로 구성

- ALU는 레지스터에 저장된 데이터를 이용하여 덧셈, 곰셈 등과 같은 산술 연산을 수행

- 부동소숫연산장치(FPU)와 정수연산장치, 논리연산(AND, OR 등)장치 등이 있음

제어 장치(Control Unit, CU)

- CPU가 자신 및 주변기기들을 컨트롤하는 장치

- 구성

- 프로그램 계수기(program counter)

- 프로그램의 수행 순서를 제어

- 명령 레지스터(instruction register)

- 현재 수행중인 명령어의 내용을 임시 기억

- 명령해독기(instruction decoder)

- 명령 레지스터에 수록된 명령을 해독하여 수행될 장치에 제어신호를 보냄

- 프로그램 계수기(program counter)

- 구현 방식

| Hardwired | Micro Program |

|---|---|

| - 제어신호가 Hardwired Circuit 에 의해서 생성되도록 하드웨어 구성 - 상태계수기와 PLA(Programmable Logic Array ) 회로로 구성 | 발생 가능한 제어 신호들의 조합을 미리 구성하여 ROM 에 저장했다가 필요시 신호를 발생시키는 Software 방식 |

| 고속 처리, 고가 | 하드웨어 방식에 비해 속도도 낮고 가격도 저렴 |

| RISC 시스템에 적용 | CISC 에 적용 |

CPU의 기능

- 명령어 인출 및 해독

- 모든 명령어들에 대하여 공통적으로 수행하며 기억 장치로부터 명령어를 읽음

- 데이터 인출 및 처리, 쓰기

- 명령어에 따라 필요할 때만 수행

명령어

시스템이 특정 동작을 수행시키는 작은 단위로 코드로 구성

- 구성 요소

- 동작 코드(Op-code): 각 명령어의 실행 동작을 구분하여 표현

- 오퍼랜드(Operand): 명령어의 실행에 필요한 자료나 실제 자료의 저장 위치를 의미

- 명령어 수행 과정

- 읽기(Fetch Instruction, FI): 메모리에서 명령을 가져옴

- 해석(Decode Instruction, DI): 명령을 해석함

- 실행(Execute Instruction, EI): 명령을 수행함

- 기록(Write Back, WB): 수행한 결과를 기록함

명령어 처리 방식

| 기준 | RISC(Reduced Instruction Set Computer) | CISC(Complex Instruction Set Computer) |

|---|---|---|

| 사이클의 개수 | 하나의 사이클로 명령어를 처리 | 여러 사이클로 명령어를 처리 |

| 명령의 개수 | 메모리 Load / Store 명령만 처리 | 많은 명령어가 메모리를 참조 |

| 파이프라이닝 사용 | 파이프라이닝, 슈퍼스칼라 사용 가능 | 파이프라이닝 사용 어려움 |

| 구조 | 복잡한 컴파일러 구조 | 복잡한 마이크로 프로그램 구조 |

Memory

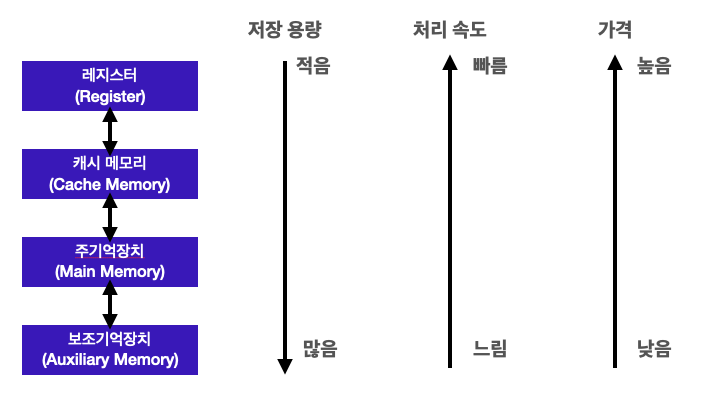

메모리 성능

- 속도가 빠를수록 좋은 성능을 가짐

- 엑세스: 메모리가 CPU와 데이터를 주고받는 시간으로 메모리 속도의 기준

- 단위: ns(nano-second) – 10억분의 1초

- 기준

- 리프레시 시간

- 정보를 기억하기 위해 메모리를 재충전하는 일정 기간

- 메모리에서 한번 읽고 나서 다시 읽을 수 있는 사이 시간

- 메모리 액세스 시간

- 데이터를 읽어오라는 명령을 받고 데이터를 읽기 시작하기까지의 시간

- CPU에서 명령어를 처리할 때 명령어가 갖는 주소를 보내고 CPU에 그 주소에 해당하는 값을 가져오기까지 걸리는 시간

- 사이클 시간(리프레시 시간 + 메모리 액세스 시간)

- 메모리 작업 완료와 동시에 대기 신호를 내놓은 후 다음 신호를 받을 준비가 되었다는 신호를 주기까지의 시간

- 리프레시 시간

메모리 종류

메모리 분류별 특징

주기억장치

- RAM(Random Access Memory): a.k.a 컴퓨터 메모리, DRAM

- 컴퓨터의 전원이 끊어지면 내용이 휘발되어 보조 저장 장치가 반드시 필요함

- RAM의 크기는 프로그램의 수행 속도에 영향을 줌

- CPU에서 직접 접근이 가능한 유일한 저장 장치

- 종류

- SRAM: 리프레쉬가 필요 없고 전력 소모가 적으나 고가

- DRAM: 리프레쉬가 필요하고 SRAM보다 저가이며 많이 사용되는 편

- ROM(Read Only Memory)

- 대부분 읽을 수만 있는 장치로 구성되어 있으며 전원이 끊겨도 내용이 보존됨

보조기억장치

- 자기 디스크

- 원판 표면의 철 입자의 방향(N/S극)으로 0과 1을 표현

- 자기 디스크로부터 데이터를 읽는 주변 장치인 디스크 드라이브 사용

- ex. 플로피 디스크(FDD), 하드 디스크(HDD)

- 광 디스크(optical disc, OD)

- 빛의 반사를 이용하여 자료를 읽어내는 저장 매체

- 1세대 CD, 2세대 DVD, 3세대 블루레이 디스크, 차세대 디스크 테라 디스크나 HVD등

- 플래시 메모리

- 전자적으로 데이터를 지우고 쓸 수 있는 비휘발성 메모리로 충격에 강하여 휴대용 기기에 널리 사용

- ex. USB, SSD

- SSD는 HDD와 달리 디스크, 헤더와 같은 기계적 장치는 빠졌지만 저전력, 저소음, 저중량

캐시 메모리(Cache Memory), SRAM

- CPU 내 또는 외에 존재하는 메모리로, 메인 메모리와 CPU 간의 데이터 속도 향상을 위한 중간 버퍼 역할

- 빠른 CPU 의 처리속도와 상대적으로 느린 메인 메모리에서의 속도의 차이를 극복하는 완충 역할

- 성능 결정 요인

- 블록사이즈나 워드 사이즈가 캐시의 성능에 영향

- 캐시 메모리는 메인 메모리의 일정 블록 사이즈의 데이터를 담아 두었다가 CPU에 워드 사이즈만큼 데이터를 전송

- 블록사이즈나 워드 사이즈가 크다면 그만큼 Cache의 Hit Ratio율이 높아지기 때문

- 블록사이즈나 워드 사이즈가 캐시의 성능에 영향

Hit Ratio(Hit Ratio)

원하는 데이터가 Cache에 있을 확률

- Cache Hit: CPU가 필요한 데이터가 Cache Memory 내에 들어와 있는 경우

- Cache Miss: 접근하고자 하는 데이터가 없을 경우

| 요인 | 내용 |

|---|---|

| Cache 크기 | Cache Memory의 Size의 크기가 크면 Hit Ratio율과 반비례 관계 |

| 인출 방식 (Fetch Algorithm) | 요구 인출(Demand Fetch): 필요 시 요구하여 인출하는 방식 선 인출(Pre-Fetch): 예상되는 데이터를 미리 인출하는 방식 |

| 쓰기 정책 (Write Policy) | Write-Through: 주기억 장치와 캐시에 동시에 쓰는 방식으로, Cache와 메모리의 내용이 항상 일치하며 구성 방법이 단순 Write-Back: 데이터 변경만 캐시에 기록하는 방식으로, 구성방법이 복잡함 |

| 교체(Replace) 알고리즘 | Cache Miss 발생시 기존 메모리와 교체하는 방식. FIFO, LRU, LFU, Random, Optimal Belady’s MIN(향후 가장 참조 되지 않을 블록을 교체) 등이 있음 |

| 사상(Mapping) 기법 | 주기억장치의 블록을 적재할 캐시 내의 위치를 지정하는 방법 직접 매핑(direct mapping), 어소시에이티브 매핑(associative mapping), 셋 어소시에이티브 매핑(set associative mapping) 등이 있다. |