이 문서는 https://asic-world.com/을 번역하여 정리한 글입니다.

Intro

베릴로그는 hardware descriptive language, HDL입니다. 즉 디지털 시스템(예를 들어 flipflop, microprocessor, memory..)을 설명하기 위한 언어입니다. 베릴로그는 Behavior level, register transfer (RTL)level, gate level, switch level에서 디지털 디자인을 가능하게 한다. 적어도 한 프로그래밍 언어를 알면 베릴로그를 배우는데는 일주일이면 충분하다고..한다..(나도 가능하겠지?)

Design Styles

Bottom-up Design

- 전통적인 디자인 방식

- 회로가 복잡해지면서 불가능해짐

Top-down Design

- 빠른 테스팅을 가능케 하는 장점이 있다.

- 그러나 어려운 방식

- 보통 두 방식을 섞어서 쓴다.

Behavioral level

RTL level

Gate level

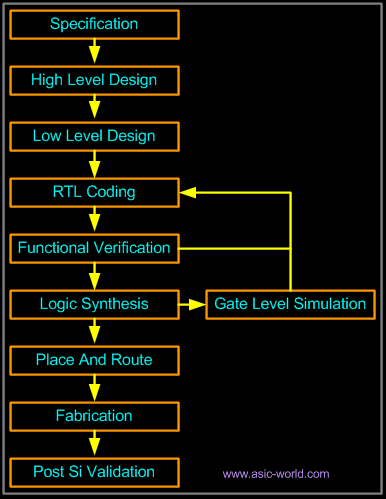

Verilog design cycle

- Specifications (specs)

- High level design

- Low level (micro) design

- RTL coding

- Verification

- Synthesis.

Module

Ports

input clock;

output s0;

inout[7:0] a0;

wire and reg

wire: 두 포인트를 연결하나 값 저장 x

reg: 값을 저장가능.

if-else

if (enable == 1'b1) begin

data = 10; // Decimal assigned

address = 16'hDEAD; // Hexadecimal

wr_enable = 1'b1; // Binary

end else begin

data = 32'b0;

wr_enable = 1'b0;

address = address + 1;

end

case

case(address)

0 : $display ("It is 11:40PM");

1 : $display ("I am feeling sleepy");

2 : $display ("Let me skip this tutorial");

default : $display ("Need to complete");

endcase

while

while (free_time) begin

$display ("Continue with webpage development");

end

for

for (i = 0; i < 16; i = i +1) begin

$display ("Current value of i is %d", i);

end

Repeat

repeat (16) begin

$display ("Current value of i is %d", i);

i = i + 1;

end

Initial blocks

initial begin

clk=0;

reset=0;

end

Always blocks

initial block과 다르게 한 번만 실행됨. @로 언제 실행할 지 알림. wire타입은 쓸 수 없다.

always @(a or b or sel) //sensitive list

begin

y=0;

if(sel==0) begin

y=a;

and else begin

y=b;

end

end

위 코드는 2:1 mux 코드이다. always block안의 코드들은 입력이 바뀔 때마다 실행되어야한다. 입력은 sensitive list 안의 변수들을 의미한다.

sensitive list에는 level sensitive와 edge sensitive가 있다

always @(posedge clk)

if(reset==0) begin

y<= 0;

end else if(sel==0) begin

y<= a;

end else begin

y<= b;

end

sequential block은 <=를 쓰고, comvinational block은 =을 쓴다.

Assign Statement

combinational logic에만 쓰인다

assign out= (enable)? data : 1'bz;

Function and Tasks

task는 delay를 가질 수 있고, function은 아니다.