안녕하세요 오늘은 combinational logic의 2번째 편인 Multiplexers에 대한 내용을 다룰려고 합니다.

지금까지 잘 따라 오셨다면 금방 이해하시리라 생각합니다.

그럼 바로 시작하도록 하겠습니다.

2-to-1 multiplexer

매우 간단한 2-to-1 mux입니다.

이건 삼항연산자를 쓰면 금방 끝나겠지요?

module top_module(

input a, b, sel,

output out );

assign out = (!sel) ? a:b;

endmodule2-to-1 bus multiplexer

이번에는 vector신호를 multiplexing하는 circuit을 작성해보라고 하는군요.

위의 문제와 다를것 없습니다.

module top_module(

input [99:0] a, b,

input sel,

output [99:0] out );

assign out = sel ? b:a;

endmodule9-to-1 multiplexer

이번에는 9-to-1 mux를 작성해보라고 하는군요.

덩치가 좀 큰 녀석이군요.

입력이 9개가 들어오고 이를 제어하는 것이니 sel신호는 4bit가 되어야겠지요?

물론 나머지 6개의 경우는 사용하지 않는 것으로 되겠습니다.

덩치가 큰 mux는 어떻게 작성하냐에 따라 기본 2-to-1 mux를 사용하는 갯수가 달라집니다.

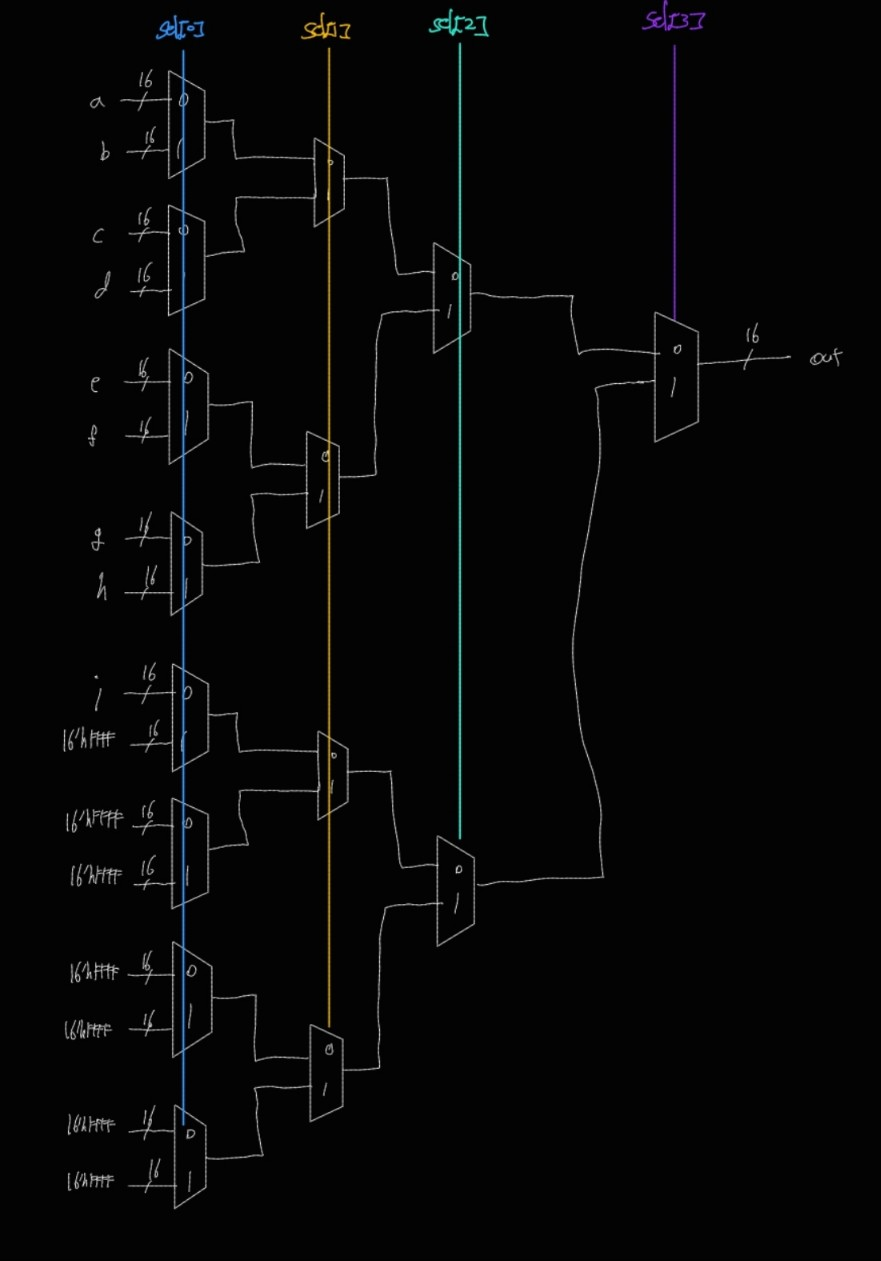

그림1 : 9-to-1 mux

그림1 : 9-to-1 mux

네 이렇게 그림을 그려볼 수 있겠습니다.

조금 조잡해 보이는군요...제가 그림을 잘 그리는 편이 아니라 하하하

네 그냥 보도록 합시다...^^;;

보면 문제에서 원하는대로 sel이 decimal로 0이면 a, 1이면 b...이런식으로 선택할 수 있도록 그려보았습니다.

이대로 HDL 코드를 작성하시면 됩니다!

갑자기 생각이 나서 한번 다른 내용을 언급하고 넘어가도록 하겠습니다.

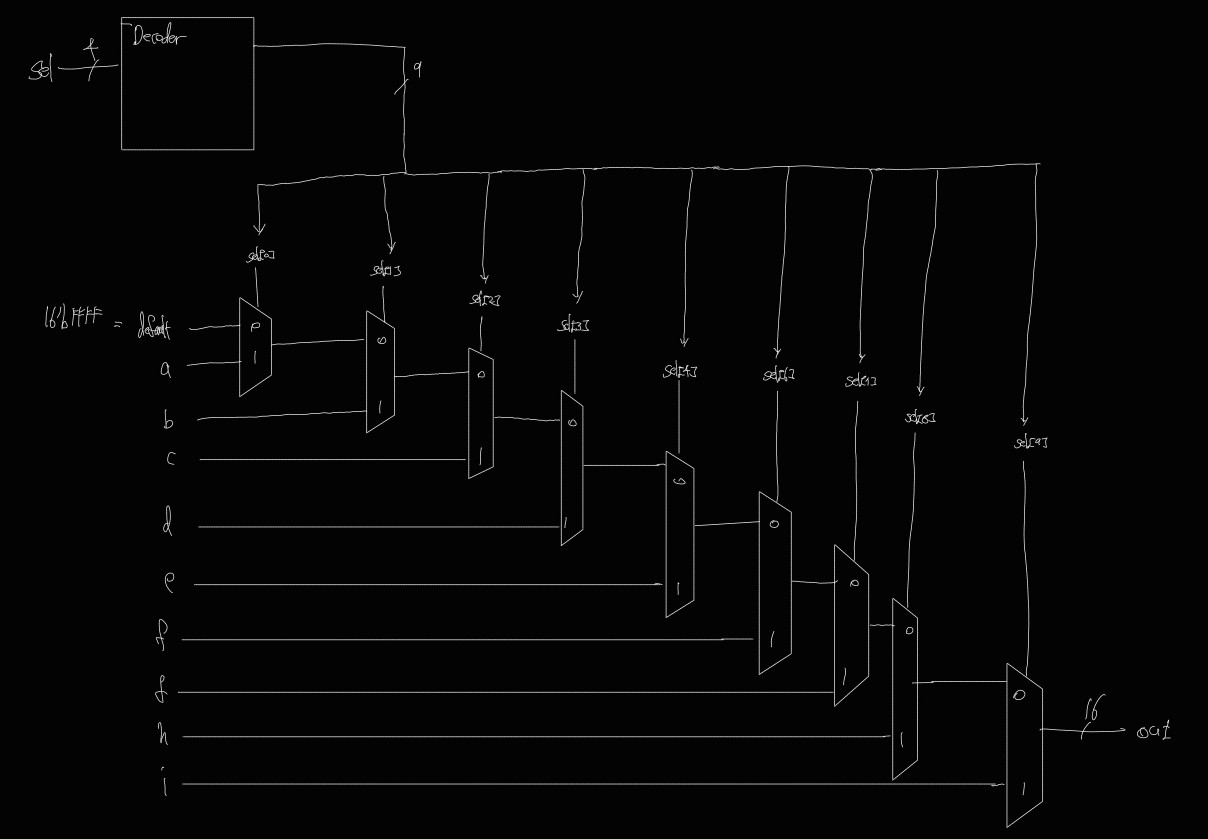

그림2 : mux2

그림2 : mux2

그림1과 그림2의 차이는 무엇일까요?

네 물론 그림이 다르죠

그림1의 logic gate의 path는 균일하게 4개의 mux를 통과합니다.

그림2의 logic gate의 path는 최악의 경우 9개의 mux를 통과합니다.

그림1에서는 mux를 좀 더 쓴 대신에 어떤 경우이든 path delay가 균일합니다,

하지만 그림2에서는 경우에 따라 path delay가 달라지지요?

모든 경우를 자주 많이 쓴다면 그림1이 좀 더 performance측면에서 좋겠지요?

반면 그림2는 몇몇 case가 빈번하게 발생하는 경우에 쓴다면 적절하겠지요?

위와 같이 생각하면 완전 큰 오산을 한 것입니다!

왜 그렇냐?

결국 이렇게 작성된 combinational logic은 clock에 동기화된 register들 사이에 배치될텐데 combinational logic에서 critical path가 그 회로의 최대 동작 주파수를 결정합니다.

따라서 그림2가 몇몇 case가 빈번하게 발생하는 경우에 쓰면 적절하겠다?

clock에 동기화된 system에서?

애초에 말이 되지 않습니다.

그럼 clock이 path delay가 긴 경우에 길어집니까?

아니죠

설령 디코더로 그림2처럼 만들었다해도 좋은 것은 아닐 겁니다.

디코더 내부의 logic gate delay + mux의 critical path하면 회로의 최대 동작 주파수는 낮아질 것입니다.

sw적으로 생각하다보면 그림2가 몇몇case에서는 좋은거 아니냐라고 생각할 수 있을것입니다...

각 case별로 조건분기문을 실행하면 그림2를 생각할 수 있겠지요

하지만 이건 sw가 아니라 hw를 설계하는 부분이라는 것을 잊지 말길 바랍니다.

사실 이런건 딱히 크게 걱정하지 않아도 될거 같습니다.

합성도구가 이런 부분을 최적화하기 때문입니다.

그래도 다단 mux로 생각하다보니 혹시나 이런 생각을 하지는 않을까 하는 마음으로 작성해봤습니다.

혹시나 이 내용이 이상하거나 문제가 있다면 댓글을 남겨주십시오...

저도 공부하면서 생각하면서 작성하는 것이라..

문제는 이렇게 작성하시면 해결할 수 있습니다!

module top_module(

input [15:0] a, b, c, d, e, f, g, h, i,

input [3:0] sel,

output [15:0] out );

assign out = (sel==4'd0) ? a : (sel==4'd1) ? b : (sel==4'd2) ? c : (sel==4'd3) ? d : (sel==4'd4) ? e : (sel==4'd5) ? f : (sel==4'd6) ? g : (sel==4'd7) ? h : (sel==4'd8) ? i : 16'hffff;

endmodule256-to-1 multiplexer

이번 문제에서는 256bit vector에서 bit select하는 mux를 작성하라고 합니다.

module top_module(

input [255:0] in,

input [7:0] sel,

output out );

assign out = in[sel];

endmodule이렇게 한줄로 끝낼 수 있습니다.

256-to-1 multiplexer

이번 문제는 1024bit vector에서 4bit씩 select하는 mux를 작성하라고 합니다.

module top_module(

input [1023:0] in,

input [7:0] sel,

output [3:0] out );

assign out = {in[4*sel+8'd3],in[4*sel+8'd2],in[4*sel+8'd1],in[4*sel]};

endmodule이렇게 indexing으로 하면 쉽게 작성할 수 있습니다.

이번 mux편은 여기까지이며, mux이외에 timing과 관련된 critical path의 내용을 추가로 언급하였습니다.

combinational logic을 간단하게 구성하는 것이, 회로의 동작을 빠르게 하기 위한 여러 방법 중 하나이며, critical path를 줄이는 방법 중 하나이기도 합니다.

다음에는 arithmetic Circuits편으로 찾아오록하겠습니다!

감사합니다!

연재가 끊겨서 아쉽지만 잘봤습니당