1-1. I/O Process

사용자가 컴퓨터를 활용한다는 것은 곧 여러 인터페이스를 통해(Input) 디바이스와 소통(Output)하는 과정을 의미합니다.

컴퓨터의 연산 처리는 CPU가 진행하고, 주기억 장치인 레지스터를 활용합니다.

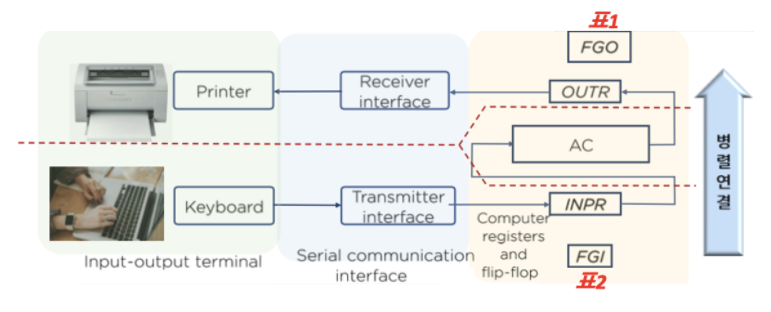

아래 Keyboard의 Input data를 받아 Printer를 통해 Output을 출력하는 과정을 알아보겠습니다.

1-2. I/O Process에 활용하는 주기억 장치

레지스터

레지스터는 CPU가 실제로 활용할 데이터 및 해당 데이터가 할당되어있는 주소를 잠시 저장하는 공간입니다.

이 과정에서 CPU는 주기억장치라는 하나의 책상을 통해 여러 연산 및 처리작업을 진행하며, 주기억장치 영역의 레지스터가 필수적으로 활용됩니다.

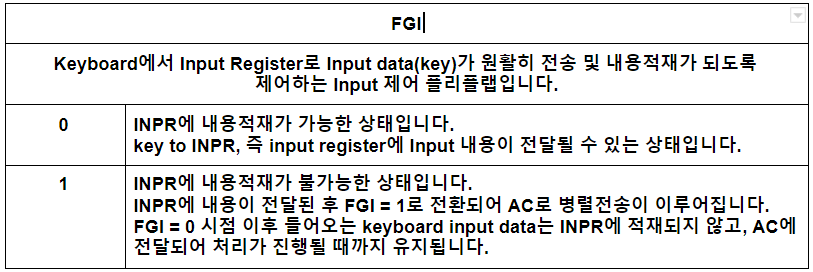

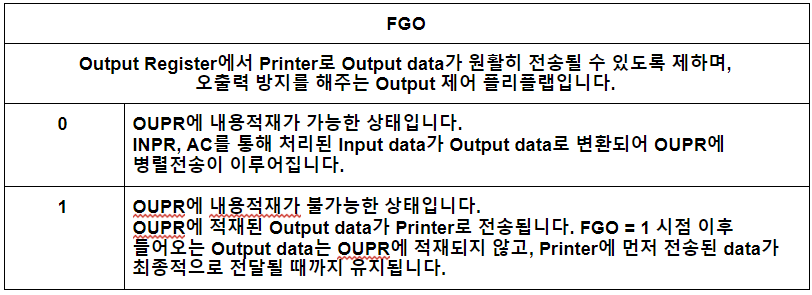

FGO / FGI

이 과정에서 연산처리의 오류방지, Input/Output 처리지연방지 및 처리소요시간 편차로 인한 결과오출력 방지, 덮어쓰기 방지 등 전체적인 처리 흐름을 제어하기 위해 각 Input/Output Register에는 FGI/FGO 플리플랩(레지스터의 집합)이 존재합니다. 이 플리플랩은 위 목적대로 처리 흐름을 제어하는 장치이며, flag bit를 활용합니다.

1-3. I/O Process 과정

Keyboard와 Printer는 사용자와 대면하는 단일장치입니다. 각각 Input과 Output의 시작과 종료지점, 다른 말로 Terminal device라고도 합니다.

Keyboard를 통해 들어온 Input은 INPR(Input Register)까지 직렬통신으로 전송되며, 전송되는 data의 형식은 보통 8bit/1code로 변환되어 전달됩니다.

이후 AC(Accumulator)레지스터에 처리결과를 일시저장하여 OUTR(Output Register)에 data를 전송하는데, 각 Transmitter interface에 의해 data가 컴퓨터가 이해할 수 있는 기계적 언어(bit, key)로 변환하는 과정을 거치게 됩니다.

INPR로 전송된 data가 AC를 거쳐 OUTR로 도달하기까지는 병렬통신로 전달되며, 순차적으로 전달되는 직렬통신과 달리 여러개의 데이터들이 일괄적으로 전송될 수 있습니다.

전달된 Input bit는 Receiver interface를 거쳐 data로 변환되어 직렬통신을 통해 Printer에게 전달되고, 최종 출력(Output, 결과물 산출)됩니다.

1-4. Register (flag bit)

CPU가 I/O Process 처리과정에서 활용하는 FGI/FGO Register와 이에 대한 flag bit가 있습니다.

1-5. 인터럽트의 도입

CPU는 프로세스를 처리하고 실행하는 주체입니다.

CPU가 다른 프로세스를 우선적으로 처리해야하는 등의 상황에서, CPU가 처리해야할 프로세스를 알려주는(혹은 처리하도록 유도하는) 주체는 운영체제나 스케쥴러입니다.

이러한 운영체제나 스케쥴러가 프로세스 우선순위를 정하고, 프로세스 종료시점에 맞추어 알맞은 연산처리가 진행될 수 있도록 처리시점을 알려주는 이벤트가 바로 인터럽트입니다.

I/O device간 처리(파일 입출력)에서 인터럽트는 매우 중요한 개념입니다.

인터럽트는 외부 인터럽트, 내부 인터럽트 등 종류가 매우 여러가지인데, 입출력 장치와 같이 시스템 처리 속도에 차이가 나는 처리에 대해선 H/W인터럽트가 사용됩니다.

보통 컴퓨터 프로세스 처리속도가 입출력장치 처리속도보다 월등히 빠르기 때문에, 플래그를 이용한 비효율적 처리 과정을 없애고자 인터럽트 개념이 도입되었습니다.

보통 IEN으로 표현되며, 내부적인 제어전송 대신 외부장치 전송이 준비상태일 때 운영체제나 스케쥴러에게 인터럽트를 발생시키게 됩니다.

기본적으로 CPU는 인터럽트의 상태를 기반으로 처리되므로, 프로그램 실행 과정 중 플래그 체크는 하지 않습니다.

다시 말해 인터럽트가 set 되면 현재 실행 중인 프로그램을 block하고, 입출력 장치를 우선적으로 처리한 후 기존 프로세스 처리에 복귀하게 됩니다.

이러한 처리 과정은 CPU 선점방식 및 정책에 따라 달라질 수 있지만, 기본적인 인터럽트 기조는 유지하여 처리가 진행됩니다.

1-6. 인터럽트를 이용한 I/O Process

인터럽트 발생 시점 이후에 CPU는 flag bit를 활용하여 처리를 진행합니다.

컴퓨터의 프로세스 처리는 크게 두가지로 나눌 수 있습니다.

※ fetch-and-execute cycle time : 20μs(하나의 instruction, 내부적인 연산을 처리하는데 20μs 소요)

※ 입출력 장치 처리 : 100 문자/초입니다. (0.01초마다 1 문자가 입/출력, I/O device에 접근 및 처리하는 외부적인 연산)

이때 CPU가 수행할 수 있는 instruction은 아래의 4가지입니다.

내부연산 및 입출력 장치 연산의 구분

해당 프로세스의 처리는 내부적인 연산과 입출력장치 연산으로 크게 나눌 수 있습니다.

내부적인 연산은 Input data를 받고 전송하는 과정과 이를 AC에서 Output data로 변환하는 과정, 레지스터를 처리하는 과정 등이 있습니다.

입출력장치 연산은 Input/Output 디바이스에서의 입력/출력값 도출, Data 전송 등이 있습니다.

각 연산은 처리속도 차이가 많이 나므로 인터럽트를 통한 처리가 필요하며, Input data 발생 시 인터럽트가 최초 발생되어 IEN register가 1로 할당되어 활성화됩니다.

이후 CPU는 flag가 set되어 프로세스 처리시 flag를 참조하면서 진행하게 됩니다. 이때 내부연산을 할 경우 명령어 레지스터 배치(이동) 및 실행 까지 fetch/execute cycle을 진행합니다.

본 기술에서는 fetch/execute cycle의 세부과정을 생략하고 바로 해당 명령이 처리되는 결과만 기재하겠습니다.

Keyboard → INPR → AC

-

a가 입력장치로 부터 입력되면, 외부입출력 처리가 필요한 과정이므로 인터럽트가 발생하게 됩니다. 이때 IEN = 1로 활성화됩니다.

※수행시간 : 내부적인 처리, 20μs -

인터럽트 발생을 인지하여 기존 프로세스 처리를 block한 후 입출력장치 처리를 우선적으로 진행합니다. CPU는 flag를 확인하면서 진행하게 되고, IEN = 1 시점 이후 입력장치로부터 문자를 입력받고 전송합니다.

※수행시간 : 외부입력장치의 데이터 전송, 0.01s (내부적인 처리시간은 이에 비해 0으로 수렴하는 수준이므로 제외) -

입력장치로부터 전송받은 데이터를 INPR에 전송합니다. 이때 CPU는 INPR에 key를 전송할 수 있는지 FGI flag bit를 확인합니다.

※flag 확인 : 1회 / 수행시간 : 내부적인 처리, 20μs -

INPR에 key를 전달한 후 FGI = 1 set합니다.

※flag 확인 : 2회 / 수행시간 : 내부적인 처리, 20μs -

FGI = 1 set 상태를 확인 후, INPR에 적재된 내용을 AC에 전송합니다. 이때 AC는 OUTR가 적재할 수 있는 Output data로 변환처리합니다.

※flag 확인 : 3회 / 수행시간 : 내부적인 처리, 20μs -

AC에 전송 후 INPR은 내용 적재가 가능한 상태가 되므로 FGI = 0 set 합니다.

※flag 확인 : 최종 4회 / 수행시간 : 내부적인 처리, 20μs -

AC 전송 이후에도 여러 문자열이 입력될 것이며, 이에 따라 지속적인 flag 확인이 이루어집니다.

AC → OUTR → Printer

-

Input key가 AC 연산처리를 통해 Output data로 변환되어 OUTR에 해당 내용이 적재됩니다. 이때 CPU는 내용적재가 가능한 상태인지 flag를 확인합니다.

※flag 확인 : 1회 / 수행시간 : 내부적인 처리, 20μs -

OUTR에 내용이 적재된 후, FGO = 1 set합니다.

※flag 확인 : 2회 / 수행시간 : 내부적인 처리, 20μs -

CPU는 FGO = 1 set 확인후 printer로 data 전송합니다. printer는 해당 data를 확인하고 출력합니다.

※flag 확인 : 3회 / 수행시간 : 외부출력장치로 데이터 전송, 0.01s(내부적인 처리시간은 이에 비해 0으로 수렴하는 수준이므로 제외) -

printer에서 최종 data 출력이 되었음을 확인 후, FGO = 0 set합니다. 이때 OUTR은 내용 적재 가능한 상태로 변환됩니다.

※flag 확인 : 최종 4회 / 수행시간 : 내부적인 처리, 20μs -

입출력장치 처리가 완료되어 IEN = 0 합니다. 인터럽트 처리가 모두 완료되어, CPU는 block된 기존 프로세스 처리를 지속합니다.

2-1. 오류검출(패리티비트)

컴퓨터는 기본적으로 데이터 전송 과정에서 처리오류가 없었는지 오류검출과정을 거치게 됩니다.

이때 가장 기본적인 오류검출 방법으로 패리티 비트를 활용한 방법이 있습니다.

패리티 비트는 데이터 전송 과정에서 bit 1개의 오류여부를 검출하는데 활용되는 비트입니다.

보통 최고비트(MSB, Most Significant bit) 및 최후비트(LSB, Least Significant bit) 를 패리티비트로 활용하며, 검출 bit수에 따라 홀수패리티 및 짝수패리티로 분류됩니다.

말 그대로 홀수패리티는 데이터 전송 전 bit수를 확인하여 패리티비트를 첨가, 1인 bit 개수를 홀수개로 맞추어 줍니다.

예를 들어, 기존 data의 bit = 1 개수가 4개라면, 데이터 전송 전 패리티 비트를 1로 맞추어 총 홀수개(=5)의 bit를 맞추어 최종 데이터를 전달합니다.

이때 데이터 전송 중 1개의 bit가 바뀌어 전송되면 bit 개수가 짝수개로 되어 홀수패리티 규칙에 위반되므로, 컴퓨터는 이 데이터가 오류임을 확인할 수 있습니다.

다만 패리티 비트를 활용할 경우 오류를 수정할 수는 없고, 단지 오류가 발생한 것만 인지할 수 있습니다.

또한 전송 중 두개 이상의 bit 에서 오류가 난다면 이에 대한 확인이 불가능 합니다. 이러한 패리티 비트의 단점을 보완한 오류 검출 방법이 해밍코드입니다.

2-2. 패리티비트 활용 예시

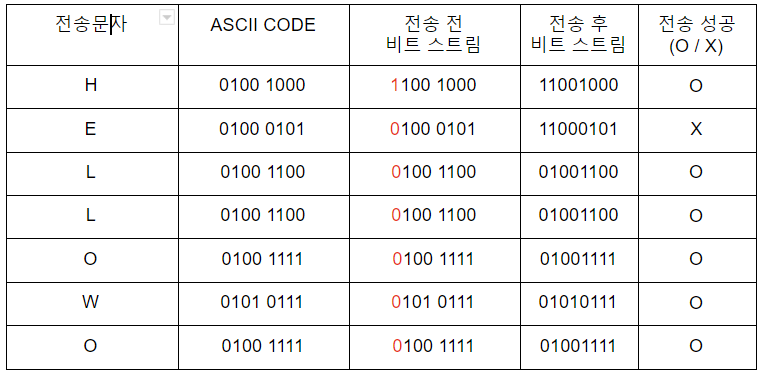

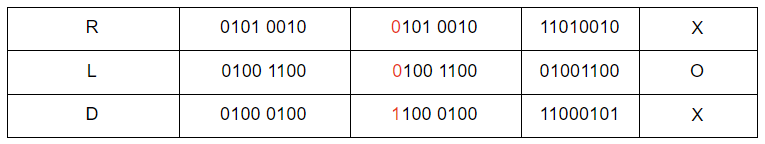

홀수 패리티를 이용하여 HELLO WORLD 문자열을 전송하며, 패리티 비트는 MSB를 활용한다고 가정해보겠습니다.

먼저 전송 전 비트 스트림을 표현한 후, 현재 이용 중인 검출 방법이 홀수 패리티이므로 MSB(가장 왼쪽 패리티 비트)로 전체 bit 개수를 맞추어 줍니다.

전송 문자를 ASCII CODE로 표현 후, 패리티 비트로 bit 수를 맞춘 후 최종 전송합니다.

전송 전 비트 스트림과 전송 후 비트 스트림이 다르다면 전송 간 오류가 있었던 것이고, 같다면 전송에 문제가 없었던 것으로 간주할 수 있습니다.

3. Remind

Not Sugar Syntax, but Sugar logic!