1-1. 병렬처리 개요

최근 출시되는 컴퓨터들은 dure core를 활용하는 등 기존 출시품보다 CPU 성능이 매우 향상되었습니다.

이러한 dure core의 이점을 최대한 높이기 위해 고안된 기술이 병렬처리 및 파이프라인 시스템입니다.

1-2. 병렬처리 개념

멀티프로세싱

CPU, 컴퓨터 처리속도향상을 목적으로 여러 CPU가 1개의 process를 처리하는 방식으로, 쉽게 말해 동시적으로 데이터를 처리하는 기술입니다.

병렬처리는 복잡도 및 활용 레지스터(병렬성을 구현할 때 고려하는 레지스터는 매우 다양하게 존재합니다)에 따라 그 단계가 나뉘게 됩니다.

다만 병렬처리의 근본 원리는 여러 개의 기능 장치를 통해 데이터를 분산처리를 한다는 것이며, 제어장치 관리에 따라 피연산자가 장치별로 처리 및 변환이 이루어지는 것으로 이해할 수 있습니다.

※이러한 여러 개의 기능 장치, 즉 다중기능 unit 체계의 processor register는 실행장치를 동시에 동작하는 8개의 처리장치를 보유하고 있습니다(Adder/Substractor, Integer/Multiply, … 등)

1-3. 병렬처리의 분류(컴퓨터 시스템 구조)

M.J.Flynn의 분류방법

동시에 처리되는 명령어 및 데이터 항목 수에 따라 시스템 구조를 분류

이러한 분류 기준에 따라 활용하는 메모리 장치, 레지스터 등이 달라지기 때문에 곧 컴퓨터 시스템 구조를 분류하는 기준으로 가정할 수 있습니다.

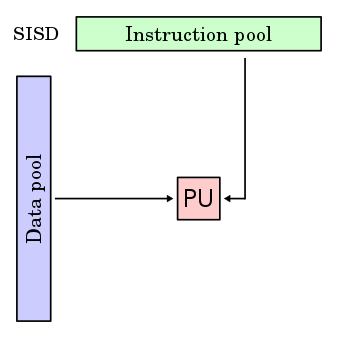

A. SISD, Single Instruction Single Data

→ 하나의 명령어로 하나의 메모리에 저장된 한 데이터를 이용하여 처리하는 구조

제어/처리/메모리 장치 등 기본 병렬처리 체계를 가지는 단일 컴퓨터 구조입니다.

현재 사용중인 구조이며, 명령어는 순차적으로 실행하며 병렬처리는 다중기능장치 및 파이프처리에 의해 구현됩니다.

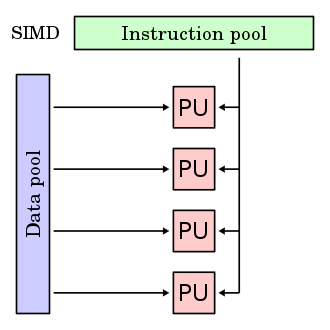

B. SIMD, Single Instruction Multi Data

→ 하나의 명령어로 여러 data를 동시에 처리하는 구조

벡터 프로세스에서 많이 사용하는 구조로, 공통의 명령어 처리 장치 아래 다중 Data를 처리할 수 있는 장치로 구성되어 있습니다.

즉 모든 프로세서들은 동일한 명령어에 대해 서로 다른 데이터 항목에 대하여 실행을 할 수 있습니다.

Clock Pulse 구현 등 로직 수행 알고리즘이 관건이며, 모든 프로세스가 동시에 Data 및 메모리에 접근할 수 있도록 관련 공유 메모리 장치가 필요합니다.

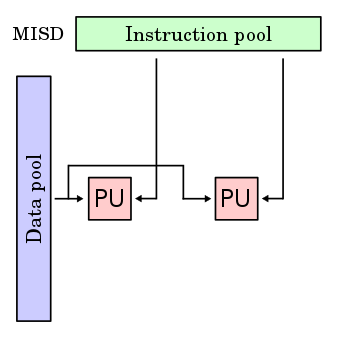

C. MISD, Multi Instruction Single Data

→ 여러 명령어를 처리하는 다수의 장치들이 이에 기반한 동일한 데이터를 처리하는 구조

파이프라인이 개념적으로 MISD 부류에 속할 수는 있으나, 실제 구현은 MISD보다는 SIMD에 더 가깝습니다.

MISD 구조는 현재 이론적 연구가 진행 중이며, 양자 컴퓨터 구조에 사용될 수 있는 체계로 볼 수 있습니다.

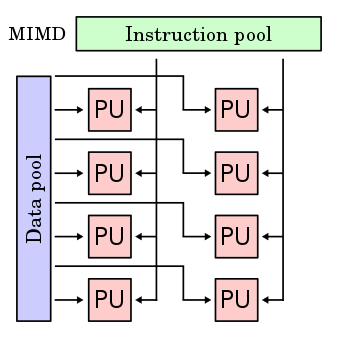

D. MIMD, Multi Instruction Multi Data

→ 여러 명령어로 여러 data를 동시에 처리하는 구조

대부분의 다중 프로세서, 다중 컴퓨터 시스템에서 볼 수 있는 구조입니다.

MISD 구조에서의 모든 프로세서들은 서로 독립적이고 비동기적입니다.

즉 각 프로세서들은 서로 다른 명령어를 기반으로 여러개의 다양한 data를 처리할 수 있습니다.

메모리 사용 방식에 따라 공유 메모리 방식, 분산 메모리 방식 등으로 분류할 수 있습니다.

2-1. 파이프라인

동일한 시간에 더 빠르고 효율적으로 명령어를 처리하기 위해 고안된 체계

파이프라인은 병렬처리가 가능하도록 구현한 체계입니다.

파이프라인의 핵심은 한 프로세스를 여러 개의 프로세스로(서로 다른 기능을 가진 서브 프로세스) 나누어, 각 프로세스가 서로 다른 데이터를 취급하도록 만든 점에 있습니다.

시스템 구현을 위해 고안된 주요 인자는 clock pulse에 따른 동기화(시간함수) 및 연산처리결과를 저장하는 세그먼트가 있습니다.

세그먼트의 경우 수행한 연산결과를 다음 세그먼트로 연속적으로 넘어가도록 하는 역할을 하며, 여러 세그먼트를 통한 동시처리를 가능하게 합니다.

최종적인 결과는 마지막 세그먼트를 통해 확보할 수 있습니다.

2-2. 명령어 파이프라인

파이프라인 설계의 한 종류

명령어 사이클의 fetch-decoding-execute 단계를 중첩하여 동작하는 체계

이전 명령어가 다른 세그먼트에서 실행되는 동안, 메모리에 연속적으로 저장되어있는 다음 명령어를 읽어오는 과정이 진행됩니다.

즉 fetch와 execute가 동시 시점에서 실행될 수 있습니다.

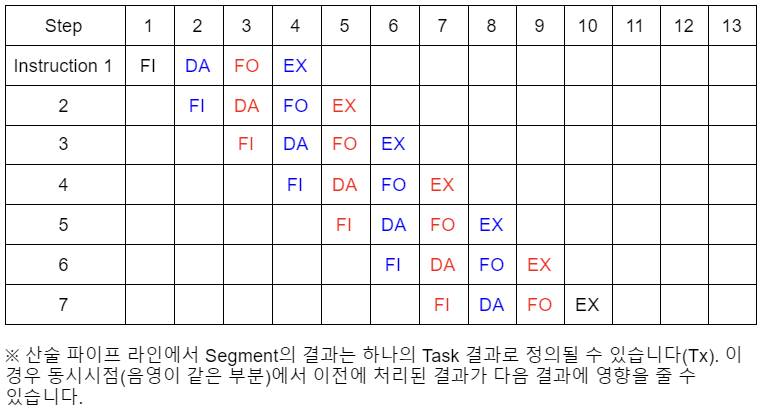

2-3. 명령어 파이프라인의 명령처리 과정(분기가 없는 경우)

Clock Pulse(Step)에 따른 순차/동시적 처리

명령어 처리에 활용하는 Segment는 다음과 같은 4종류라 가정해보겠습니다.

- FI(Fetch Instruction)

- DA(Decode and calculate effective Address)

- FO(Fetch Operand)

- EX(EXecute instruction)

기본적으로 파이프라인은 벡터처리입니다.

즉 SIMD 구조를 채용하여, 하나의 명령어에 대해 다수의 Data를 처리할 수 있는 구조입니다.

여기서 Data가 저장되어있는 공간은 Segment이고, 현 조건에서는 4개의 Segment가 존재합니다.

각 Segment는 Clock Pulse(=Step)마다 FI(명령어를 레지스터에 옮김) → DA(명령어 디코딩) → FO(연산결과 옮김) → 명령어 최종 실행을 순차적으로 실행하되, 이 처리 시점을 명령어 별로 다른 시점에서 실행한 후 해당 결과를 옮기는 방식으로 명령어 처리가 동시적으로 일어나도록 구현합니다.

2-4. 파이프라인의 분기이슈

분기예측을 통한 분기이슈로 인한 성능저하 보완

파이프라인의 목적인 컴퓨터 처리 속도 및 성능 향상을 달성하기 위해 극복해야하는 여러 제약 조건들이 존재합니다. 특히 그 중 분기이슈가 가장 큰 제약조건입니다.

분기점 및 서브루틴 발생 시 분기점 이후 실행된 기존 명령어는 모두 무시되어야 하고, 분기점에 대한 로직만 수행해야 합니다. 이에 따라 현재 진행중인 파이프라인은 모두 비워져야 합니다.

2-5. 분기예측

분기예측은 기존 분기이슈인 명령어 파이프라인의 block(중단) 상태 및 성능저하를 개선하고자, 분기점이 실행될 시점을 추론하여 미리 분기명령을 실행하는 방식입니다.

예측 성공시 그대로 분기명령 실행, 실패시 분기 명령을 철회하고 기존 명령을 그대로 지속합니다. 즉 별도의 중단없이 파이프라인은 명령어 처리를 계속할 수 있게 됩니다.

※Cahce memory의 data 저장원리인 locality 개념과 같습니다. 시스템은 경험적인 추론 알고리즘을 통해 분기가 일어날 가능성이 높은 지점을 예측하고, 분기명령을 미리 실행합니다.

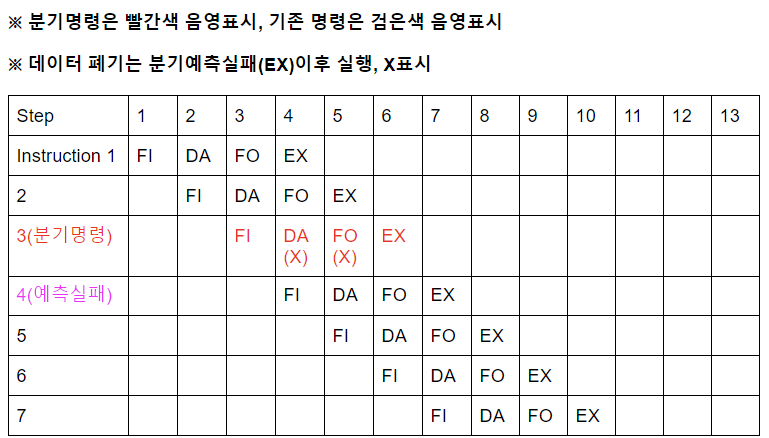

2-6. 명령어 파이프라인의 명령처리 과정(분기가 있는 경우)

분기예측을 통해 처리중단을 방지 가능

먼저 아래와 같이 분기예측을 통한 명령처리 과정을 가정해보겠습니다.

A. 분기예측으로 인해 분기가 일어나는 시점은 FI segment에서 명령어가 처리 될 때입니다.

즉 분기가 일어나도 기존 명령어 처리 시 DA, FO, EX 세그먼트에서의 처리가 무시될 여지는 없습니다.

B. 분기예측 이후 예측의 hit/miss 여부 상관없이 분기명령의 FI, DA, FO, EX는 모두 실행됩니다.

C. 분기예측의 hit/miss 여부를 판단하는 시점은 EX 시점입니다. 해당 시점에서 분기예측 실패를 인지할 경우에 기존 분기 명령을 철회하고, 새로운 명령어를 처리하게 됩니다.

D. 새로운 명령어가 실행되는 시점은, EX후 바로 다음 시점입니다. 여기서 시점이란, 분기명령의 EX세그먼트가 실행된 다음의 Step(Clock Pulse)입니다.

→ 분기예측을 실행한다면 분기점으로 인한 처리중단을 방지할 수 있습니다.

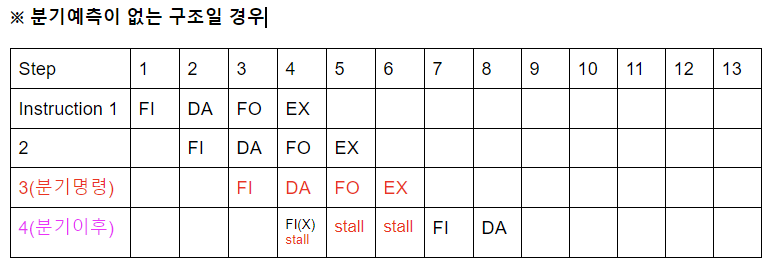

분기예측이 없다면 처리중단으로 인한 컴퓨터 성능저하 초래

→ 분기예측이 없다면 Instruction4에서 Step 4에 실행된 FI Segment는 무시(폐기)되고, 분기 명령이 끝날 때까지 stall(대기)상태입니다. 분기명령의 EX까지 모두 완료된 이후에 FI가 실행됩니다. 이로 인해 3Step만큼의 Stall(중단)이 발생합니다.