CPU를 이야기할 때 자주 나오는 키워드가 CISC와 RISC다. 둘 다 ISA(Instruction Set Architecture, 명령어 집합 구조)를 어떻게 설계할지에 대한 방식이다.

1. CISC / RISC 한 줄 정의

- CISC (Complex Instruction Set Computer)

복잡하고 다양한 명령어를 많이 제공하는 ISA. 한 명령어가 비교적 “큰 일”을 처리할 수 있다. - RISC (Reduced Instruction Set Computer)

단순하고 규칙적인 명령어를 적게 제공하는 ISA. 작은 명령어들을 많이 묶어서 일을 처리하는 방식에 가깝다.

둘 다 “CPU가 이해하는 언어를 어떻게 디자인할까?”에 대한 서로 다른 철학이라고 보면 된다.

2. CISC의 특징

CISC는 “명령어를 복잡하게 만들어서, 한 번에 많은 일을 하도록 하자”에 가까운 접근이다.

-

복잡하고 다양한 명령어

- 수십~수백 개 명령어, 다양한 주소 지정 모드 지원.

- 예: 하나의 명령어로 메모리에서 값 읽고, 연산하고, 다시 메모리에 쓰기까지 처리.

-

가변 길이 명령어

- 명령어마다 길이가 다르다(1바이트, 2바이트, 3바이트…).

- 코드 크기를 줄이기는 좋지만, 디코딩 로직이 복잡해진다.

-

마이크로코드 기반 제어

- 복잡한 명령어를 내부적으로 더 작은 단계들로 쪼개서 실행하는 펌웨어(마이크로코드) 사용.

- ISA를 바꾸지 않고도 내부 구현을 바꾸기 쉬워, 호환성 측면에서 유리하다.

-

장점

- 같은 작업을 적은 수의 명령어로 표현할 수 있어서 코드 밀도가 높다.

- 오래된 명령어와의 하위 호환성을 유지하기 좋다.

-

단점

- 명령어 디코딩과 제어 회로가 복잡해지고,

- 파이프라인·병렬 실행 최적화가 상대적으로 어렵다.

-

대표 예시

- x86, x86-64 계열 CPU (인텔, AMD).

3. RISC의 특징

RISC는 “명령어를 단순하게 만들고, 대신 빠르게 많이 돌리자”에 가까운 접근이다.

-

단순하고 적은 명령어

- 기본 연산들은 거의 레지스터 간 연산으로 제한.

- 메모리 접근은 Load / Store 명령에만 허용하는 구조가 많다.

-

고정 길이 명령어

- 대부분 명령어 길이가 일정(예: 4바이트).

- 디코더를 단순하게 만들 수 있고 파이프라인 설계에 유리하다.

-

하드와이어드 제어

- 단순한 명령어들을 논리 회로로 직접 제어하는 구조 사용.

- 마이크로코드 의존도가 낮다.

-

파이프라이닝 / 병렬 실행에 유리

- 명령어 포맷이 규칙적이라, 파이프라인·슈퍼스칼라·Out-of-order 실행 최적화가 쉽다.

- 전력 효율이 좋아 모바일·임베디드에서 강세다.

-

장점

- 디코더·제어부가 단순해 클럭을 높이거나 파이프라인을 깊게 가져가기 좋다.

- 전력 대비 성능이 좋아 배터리 기반 기기에 적합하다.

-

단점

- 같은 일을 하려면 더 많은 명령어가 필요해 코드 길이가 길어질 수 있다.

- ISA 레벨에서 보면 기능이 단순해서, 같은 역할을 하려면 컴파일러/프로그래머가 더 많은 조합을 만들어야 한다.

-

대표 예시

- ARM, RISC‑V, MIPS, SPARC 등.

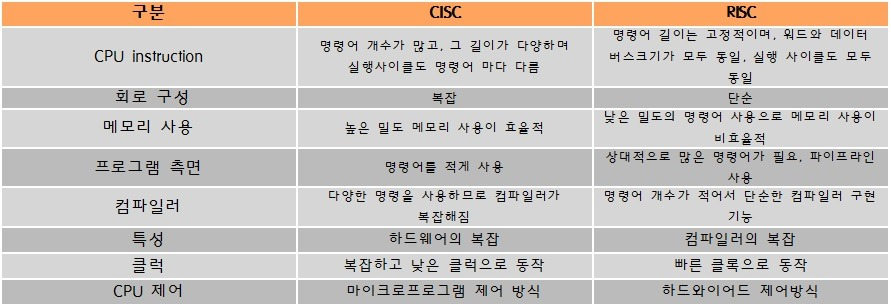

4. CISC vs RISC 한 눈에 비교

| 구분 | CISC | RISC |

|---|---|---|

| 철학 | 복잡한 명령어, 적은 명령어 개수로 많은 일 처리 | 단순한 명령어, 빠르게 많이 실행 |

| 명령어 수 | 많음 (수십~수백 개) | 적음 (핵심 소수 + 확장) |

| 명령어 길이 | 가변 길이 | 고정 길이인 경우가 많음 |

| 메모리 접근 | 연산 명령어에서 직접 메모리 접근 가능 | Load/Store 구조 선호 |

| 제어 방식 | 마이크로코드 기반 제어 많음 | 하드와이어드 제어 비중이 큼 |

| 디코딩/제어 복잡도 | 복잡 | 단순 |

| 파이프라이닝/병렬 실행 | 상대적으로 어려움 | 설계가 유리함 |

| 코드 크기 | 짧을 수 있음 | 길어질 수 있음 |

| 전력/효율 | 상대적으로 높은 전력, 복잡한 회로 | 전력 효율 좋고 모바일/임베디드에 유리 |

| 대표 ISA | x86, x86-64 | ARM, RISC‑V, MIPS 등 |

5. 현대 관점에서 한 가지 더

요즘 CPU는 “순수 CISC vs 순수 RISC”로 딱 잘라 나누기보다는, 서로의 장점을 섞어 쓰는 쪽에 가깝다.

- x86 계열(CISC ISA)은

- 외형상 복잡한 CISC 명령어를 제공하지만,

- 내부적으로는 RISC 스타일의 마이크로 연산(micro‑ops)으로 쪼개서 파이프라인에 태우는 구조가 일반적이다.

- ARM·RISC‑V 같은 RISC 계열 ISA도

- 세대가 지나면서 다양한 확장 명령어(SIMD, 암호화, 벡터 등)를 붙이며

- 단순한 “소수의 명령어만 있는 ISA”와는 거리가 점점 멀어지고 있다.

실제 개발자 입장에서는 “내 코드가 CISC인지 RISC인지”보다,

- 어떤 ISA 위에서 돌아가는지(예: x86 vs ARM),

- 그 ISA가 제공하는 명령어/특성을 컴파일러·런타임·JIT이 어떻게 활용하는지,

이 쪽을 더 신경 쓰게 되는 편이다.