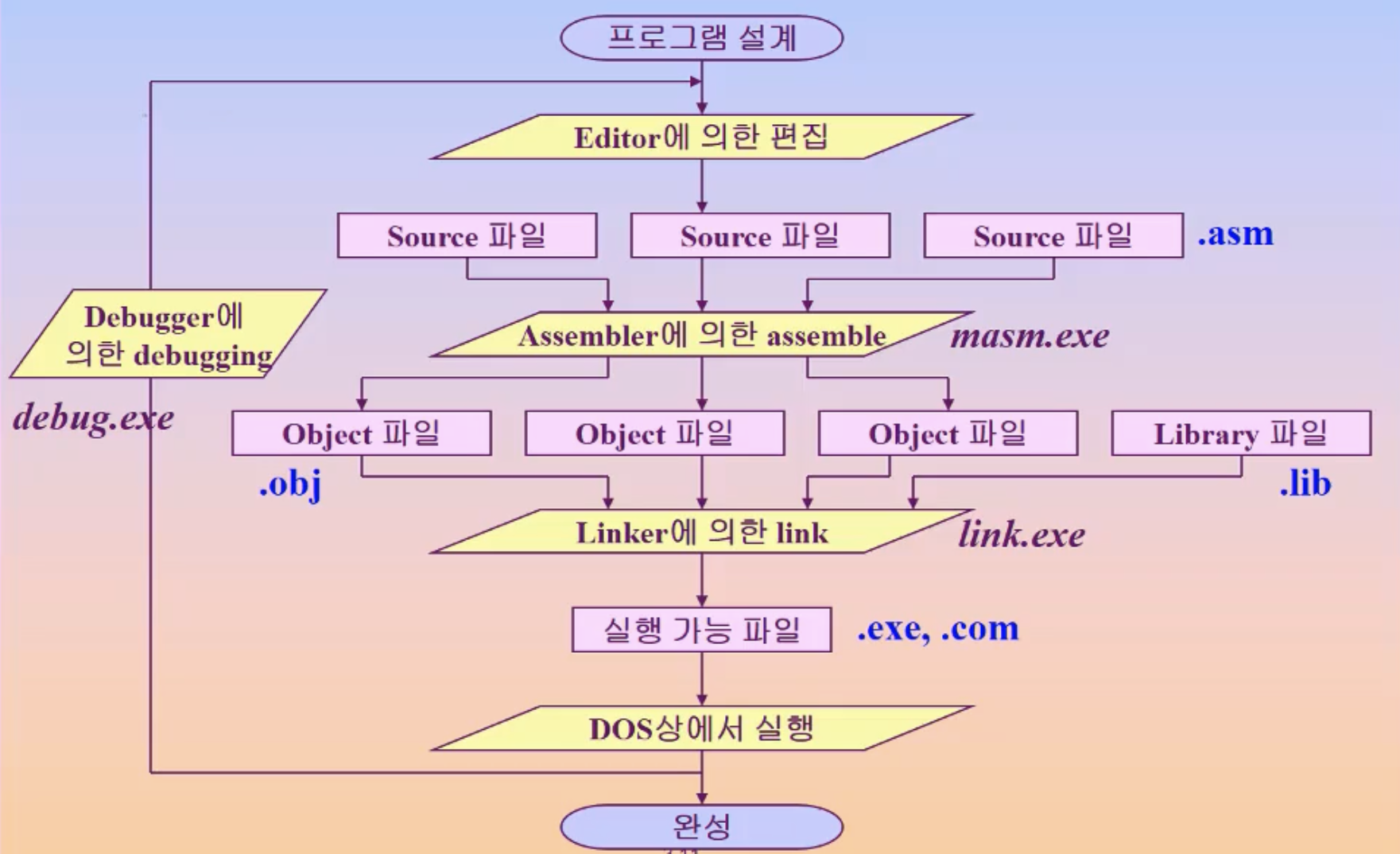

MASM에 의한 Program 개발 과정

CPU의 명령어 실행 과정

- Instruction Fetch Cycle : 실행할 명령어를 기억 장치로부터 읽어오는 과정

- Instruction Decode Cycle : 읽어온 명령어를 해독하는 과정

- Data Fetch Cycle : data가 필요한 경우 data를 읽어오는 과정

- Execution Cycle : 프로세서가 명령어를 실행하는 과정

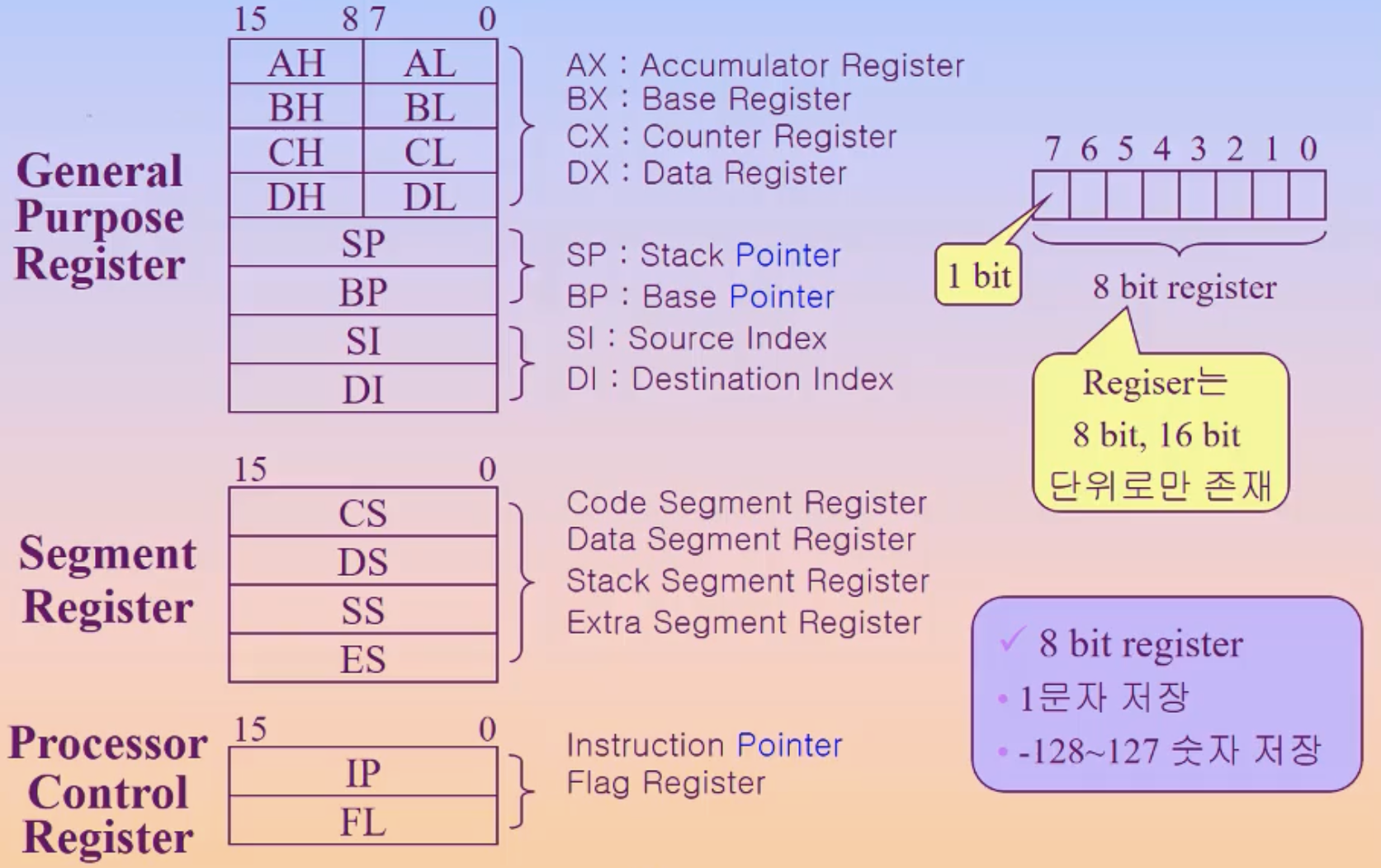

8086 계열 기본 Register

Register

- Data 저장, 연산 등을 하기 위한 임시 기억 장치

- 각 register는 자체의 특수한 용도와 제한점이 있다.

- 장점 : memory보다 access 속도가 빠르다

- 단점 : 개수가 한정되어 있고, 용도가 제한적이다.

종류

General Purpose Register: 8개Segment Register: 4개processor controll register: 2개

General Purpose Register: AX, BX, CX, DX, SP, BP, SI, DI

➡️ 8086은 16bit이므로 범용 register가 16bit이다.

➡️ AX는 16bit이고, AH(상위)와 AL(하위)로 나누어 각각 8bit 8bit로 나눌 수 있다.Segment Register: CS, DS, SS, ES

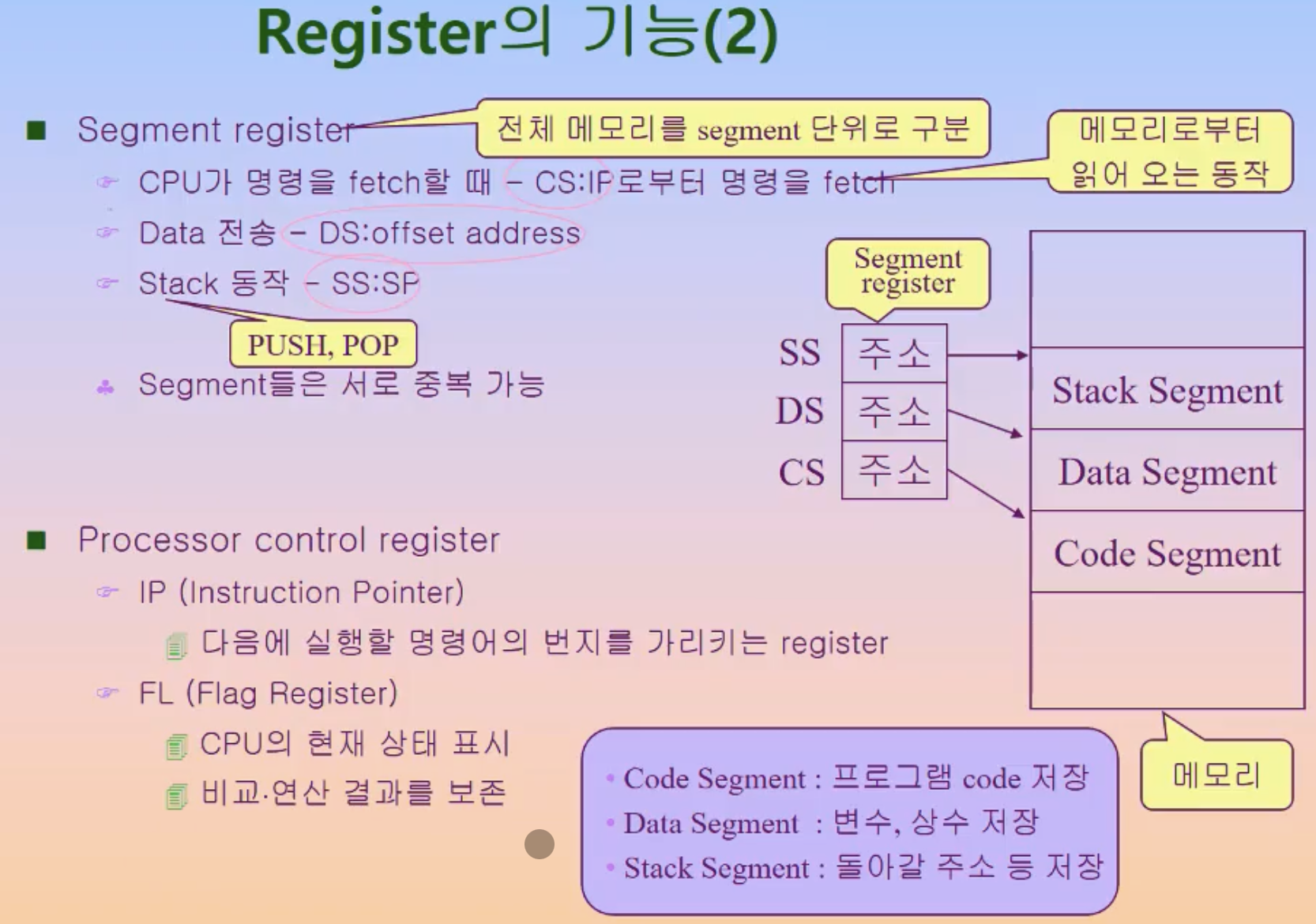

➡️ CS : Code Segment Register

CPU가 명령을 fetch할 때, CS : PI로부터 명령을 fetch

➡️ DS : Data Segment Register

Data 전송, DS : offset address

➡️ SS : Stack Segment Register

Stack 동작, SS : SP

➡️ ES : Extra Segment RegisterProcessor Control Register: IP, FL

➡️ IP : Instructino Pointer

➡️ FL : Flag Register

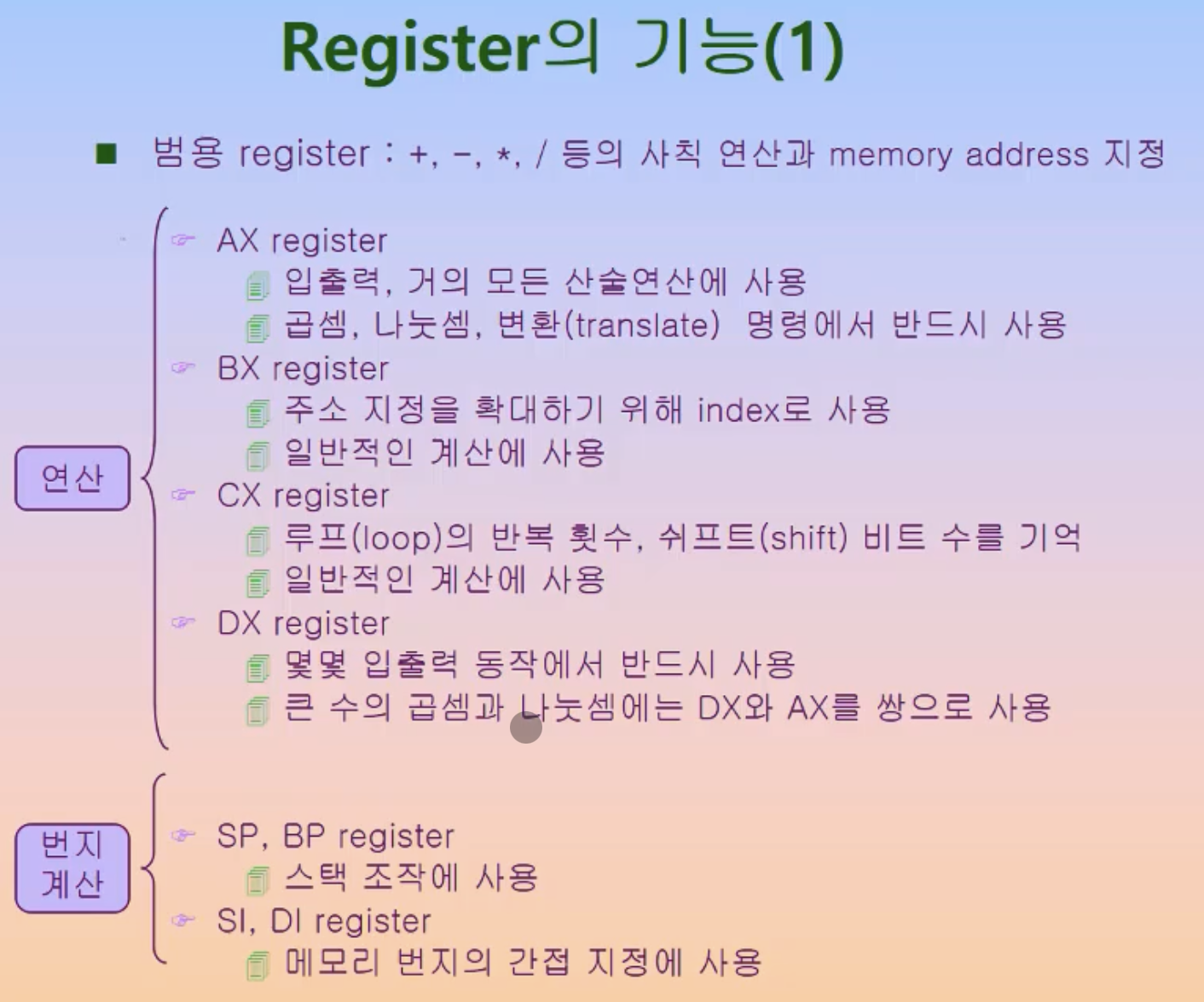

기능