1.1 Overview

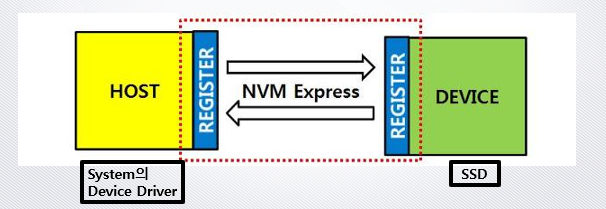

NVMeTM(NVMeTM) 인터페이스를 통해 host SW가 비휘발성 메모리 subsystem과 통신할 수 있다. 이 인터페이스는 일반적으로 PCI Express 인터페이스에 레지스터 레벨 인터페이스로 연결되는 엔터프라이즈 및 클라이언트 ssd에 최적화되어 있다.

참고: 개발하는 동안 이 사양은 Enterprise NVMHCI로 언급되었다. 그러나 이름이 완료되기 전에 NVM Express 기본 사양으로 수정되었다. 이 인터페이스는 클라이언트 시스템과 Enterprise 시스템 모두에서 사용하기 위한 것이다.

NVMe란?

SSD와 같은 비휘발성 메모리 장치를 컴퓨터와 연결하는

"Host Controller Interface / Protocol"

"Host와 Device간에 통신하는 방법에 대해 기술한 스펙"

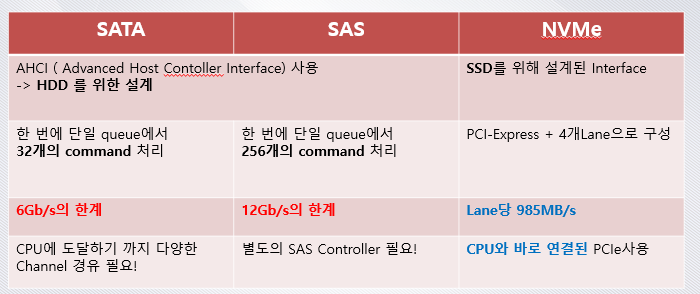

과거 기술들과 비교

1.1.1 NVMe over PCIe and NVMe Fabrics

NVM Express 기본 사양 버전 1.4 및 이전 버전은 PCIeTM(NVMeTM over PCIeTM)을 통해 비휘발성 메모리 subsystem과 통신하기 위한 host SW의 레지스터 레벨 인터페이스를 정의했다. NVMe over Fabrics 사양은 다른 상호 연결(예: 이더넷, InfiniBand™, Fibre Channel)을 통한 작동을 가능하게 하는 프로토콜 인터페이스 및 NVMe 인터페이스에 대한 관련 확장을 정의한다. NVMe over Fabrics 사양은 각 NVMe Transport에 대해 NVMe Transport 바인딩을 갖는다(해당 사양 내에서 또는 참조에 의해).

본 명세서에서 요구사항/기능은 패브릭 구현을 통한 NVMe 또는 특정 NVMe Transport 바인딩에 특정한 것으로 문서화될 수 있다. 또한 기능 및 기능에 대한 지원 요구사항은 PCIe를 통한 NVMe와 패브릭 구현을 통한 NVMe 간에 다를 수 있다.

1.2 Scope

NVM subsystem에서 controller 와 통신을 위한 레지스터 인터페이스를 정의

a) I/O controllers

b) discovery(검색) controllers

c) administrative (관리) controllers

1.4 Theory of Operation

NVMe는 PCI Express기반 Solid State Drive/ fabric연결 device 사용을 위한 설계

• 최적화된 command submission 과 완벽한 paths를 제공함

→ 최대 65,535개의 I/O Queue를 사용하여 병렬 운영 지원

• 추가적인 enterprise 기능

o end-to-end 데이터 보호

o 향상된 오류 보고

o 가상화

Interface 속성

1. command 전달/완료 시 MMIO 레지스터 read가 필요하지 X

2. command 전달 시 최대 1개의 MMIO 레지스터 write 기능이 필요

3. 최대 65,535개의 I/O Queue를 지원하며 각 I/O Queue는 최대 65,535개 command 가능

4. I/O Queue 우선순위 기능과 중재 메커니즘 제공;

5. 4KiB read를 완료하기 위한 모든 정보는 64B command 자체에 포함됨

→ 효율적인 적은 양의 I/O 동작을 보장함

6. 효율적인 command set;

7. MSI(Message Signaled Interrupts)/MSI-X, interrupt 다수 지원

8. 여러 개의 namespace 지원

9. I/O 가상화 아키텍처 지원 ex) SR-IOV

10. 강력한 오류 보고 및 management 기능

11. multi-path I/O와 namespace 공유

참고) MMIO(Memory Mapped I/O)

참고) MSI(Message Signaled Interrupt)

Interrupt란?

프로세서가 순차적으로 작업을 처리 중인 상황에서 일시 중단하고 우선적으로 먼저 처리해줘야 할 긴급한 작업

MSI(Message Signaled Interrupt)란?

인터럽트 라인의 기존 대역 외 신호를 대체하여 특수 대역 내 메시지를 사용해 인터럽트 신호를 보내는 방법

참고) Multi-Path I/O and Namespace Sharing

Multi-Path란?

Multi-Path I/O는 단일 Host와 namespace사이 간 2개 이상의 독립된 path를 말한다

Namespace Sharing이란?

2개 이상의 host가 서로 다른 NVM Controller를 사용하여 하나의 공유된 namespace에 접근하는 것

참고) NVMe Subsystem Model

NVM Subsystem이란?

하나 이상의 controller, 하나 이상의 namespace, 하나 이상의 PCI Express port, 비휘발성 메모리 저장매체 및 컨트롤러와 비휘발성 메모리 저장 매체(SSD) 간의 인터페이스

Controller란?

NVM Express를 구현하는 PCI Express 기능

참고) Namespace 생성

Namespace Management command와 Namespace attachment command를 사용해 namespace를 생성/삭제 시킨 후 컨트롤러에 attachment/detach 시킬 수 있음

모든 컨트롤러가 namespace management를 지원하지 않으므로 컨트롤러가 아래의 작업을 수행해야함!

- Namespace Management command와 Namespace Attachment command 지원

- OACS (Optional Admin Command Support) 의 3번째 비트를 1 로 설정

- Namespace Attribute Changed 비동기 이벤트를 지원 해야 함

Namespace를 생성하기 위해, host SW는 다음과 같은 작업을 수행함 :

- Host SW가 Identify command 이용

- 컨트롤러가 사용하는 일반적인 Namespace 데이터 구조를 파악한다.

(Identify 엔트리에서 NSID를 FFFFFFFFh로 설정 후,

CNS(controlller/namespace structrue) 필드를 0h 로 설정)- host SW가 4KB 데이터 구조를 Spec의 Figure 124를 참조하면서 생성한다.

- hostSW specified fields를 Figure 121을 참조하면서 원하는 값으로 설정한다.

- hostSW가 Namespace Management command를 Data Structure와 함께 SQ로 발생시킨다.

- command가 성공적으로 끝나면, 새로운 namespace의 NID가 CQ의 Dword 0에 return 된다.

- 이 단계에서는 아직 새로운 namespace가 컨트롤러에 부착 되어있지 않다.

- hostSW가 새 namespace의 모든 특성을 알기 위해서

새로운 namespace의 Data Structure를 Identify하는 것을 요청한다.

NVMe 컨트롤러 단일 PCI Function과 연결되어 있다.

전체 controller에 적용되는 기능 및 설정은 controller 기능(CAP) 레지스터 및 식별 데이터 구조에 표시된다. namespace는 논리 블록으로 format될 수 있는 비휘발성 메모리의 양이다.

NVMe 컨트롤러 namespace ID를 사용하여 참조되는 여러 namespace를 지원할 수 있다. namespace는 생성/삭제 가능하며, namespace 데이터 구조 식별은 특정 namespace에 특정한 기능과 설정을 나타낸다. 모든 namespace에 공통되는 기능 및 설정은 namespace ID FFFFFFh에 대한 식별 namespace 데이터 구조에 의해 보고된다.

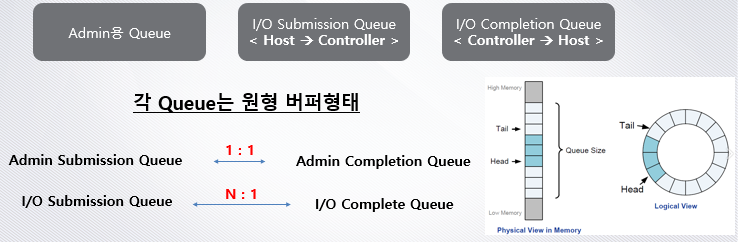

NVMe interface는 Submission Queue + Completion Queue의 쌍으로 구성된 메커니즘을 기반으로 한다.

command는 host SW에 의해 Submission Queue에 배치되며, Completion은 controller에 의해 Completion Queue에 배치된다. 여러 개의 Submission Queue는 동일한 CQ를 사용할 수 있다.

Submission Queue, Completion Queue는 Memory에 할당된다.

Admin Submission과 관련된 Completion Queue는 controller 관리 및 제어 목적으로 존재한다. (ex : I/O Submission 및 Completion Queue 생성 및 삭제, 명령 중단 등)

Admin Command 일부만 Admin Submission Queue에 제출할 수 있다. I/O Command Set은 I/O queue pair과 함께 사용되며 이 규격은 NVM Command Set이라는 하나의 I/O Command Set을 정의한다.

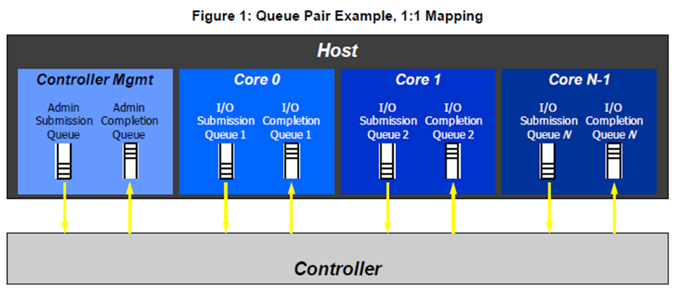

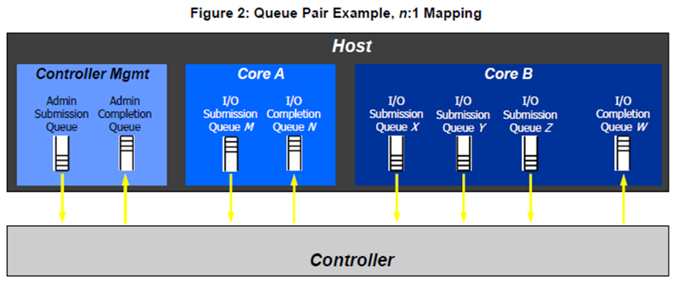

host가 모든 I/O Queue pairs에 사용되는 I/O Command Set을 하나 선택한다. Host SW는 controller가 지원하는 최대까지 queue를 생성한다. 일반적으로 생성되는 command queue수는 시스템 구성과 예상된 작업량 기준으로 한다.

예를 들어, 4개의 core 프로세서 기반 시스템에서는 locking을 방지하고 적절한 프로세서 core의 cache에 데이터 구조가 생성되도록 core당 queue pair가 있을 수도 있다.

NVMe Controller - Host 소통방식

NVMe controller에 명령을 내리기 위해서 3개의 Queue를 코딩한 다음 그 주소 값을 넘겨준다.

둘 다 모두 항상 Admin Submission Queue와 Admin Completion Queue와의 1:1 mapping이 존재한다.

SQ(Submission Queue): ( Host -> Controller )

Host SW가 Controller를 실행하기 위한 명령을 제출하는데 사용하는 고정 slot 크기의 원형 버퍼

host SW는 실행할 명령이 1~n개 있을 때 SQ Tail doorbell 레지스터를 업데이트한다. 새로운 doorbelll 레지스터가 “쓰기”를 할 때, 이전의 SQ Tail 값을 덮어쓴다. 컨트롤러 SQ항목을 순서대로 가져와서 실행한다. 각 SQ는 64byte 크기의 command이다.

메모리의 물리적 메모리 위치는 물리적 영역 페이지(Physical Region Page, PRP) 또는 Scatter Gather Lists(SGL)를 사용하여 지정된다. 각 명령은 2개의 PRP 또는 1 개의 SGL 세그먼트가 포함될 수 있다.

데이터 버퍼를 설명하는데 2개 이상의 PRP가 필요한 경우, PRP Entry List을 설명하는 PRP LIST의 pointer가 제공된다. 데이터 버퍼를 설명하는데 1개 이상의 SGL이 필요한 경우, SGL세그먼트는 다음 SGL 세그먼트에 대한 포인터를 제공한다.

- 적당한 코어를 선택하고 해당 코어의 I/O Submission Queue에 command를 넣는다.

- 호스트는 NVMe 컨트롤러의 Submission Queue Tail Doorbell 레지스터를 사용해서 NVMe컨트롤러에 새로운 command의 존재를 알린다.

- NVMe 컨트롤러가 큐(시스템 메모리)의 command를 가져온다.

- NVMe컨트롤러가 가져온 command를 처리한다 (SSD - 시스템메모리 상의 입출력이 작동한다)

CQ(Complete Queue): ( Controller -> Host )

완료된 command 상태를 게시하는 데 사용되는 고정 slot 크기의 원형 버퍼

완료된 command는 SQ Identifier와 command Identifier의 조합이며, 이 기능은 command가 여러 SQ에서 시작된 경우에도 하나의 CQ를 통해 하나의 Worker Thread가 모든 command를 완료 처리하는데 사용될 수 있다. CQ Head Pointer는 마지막 사용 가능한 CQ slot을 나타내는 CQ Entry를 처리한 후 host SW에 의해 업데이트 된다

CQ Entry에는 P(Phase Tag) bit가 정의되어 레지스터와 상의하지 않고 Entry이 새로 게시되었는지 여부를 나타낸다. 이를 통해 Host SW는 새 Entry가 이전 또는 현재 완료되었는지 여부를 확인할 수 있다.

구체적으로, CQ를 통해 매 라운드마다 컨트롤러는 Phase Tag bit를 반전시킨다.

- NVMe컨트롤러는 명령어 처리가 끝나면 I/O Completion Queue에 처리결과를 넣는다.

- NVMe컨트롤러는 적당한 MSI_X 인터럽트를 발생시킨다.

- 호스트의 인터럽트 서비스 루틴은 처리결과를 I/O Completion Queue에서 꺼내서 확인한다.

- 호스트는 인터럽트 확인을 마쳤다는 의미로 Completion Queue Head Doorbell 레지스터를 사용한다.

1.4.1 Multi-Path I/O and Namespace Sharing

이 섹션에서는 Multi-path I/O 및 namespace공유에 대한 개요를 제공한다. Multi-Path I/O는 단일 HOST와 namespace사이의 2개 이상의 완전히 독립적인 경로를 의미하고 namespace 공유는 2개 이상의 host가 서로 다른 NVMe 컨트롤러를 사용하여 공통 공유 namespace에 접근하는 기능을 의미한다.

Multi-Path I/O 및 namespace 공유를 사용하려면 NVM서브시스템에 2개 이상의 컨트롤러가 있어야한다. Multi-Path I/O 및 namespace 공유를 지원하는 NVM서브시스템은 비대칭 컨트롤러 동작도 지원할 수 있다. 둘 이상의 Host가 공유 namespace에 동시에 접근하려면 Host끼리 서로 어떤 형태로든 조정해야 한다. 이러한 호스트를 조정하는데 사용되는 절차는 이 규격의 범위를 벗어난다.

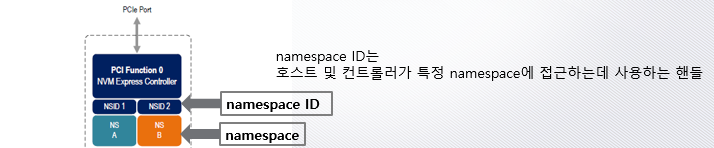

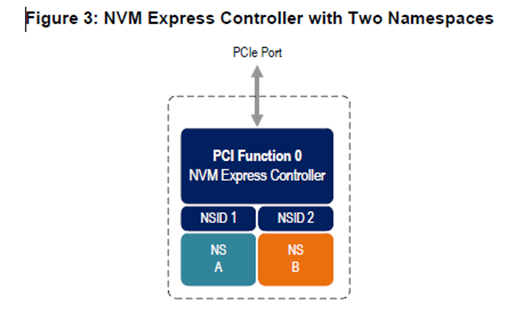

그림 3은 단일 NVMe 컨트롤러와 단일 PCIe포트를 포함하는 NVM subsystem이다. 단일기능 PCIe장치이므로 NVMe컨트롤러는 PCI Function0과 연결되어야 한다. 하나의 컨트롤러는 여러 개의 namespace를 지원할 수 있다. 그림 3에서 컨트롤러는 2개의 namespace “NS A, NS B”를 지원한다. 각 컨트롤러 namespace와 연결된 namespace ID(“NS A, NS B”)는 특정 namespace를 참조하는데 사용된다. namespace ID는 namespace자체와 구별되며 Host 및 컨트롤러가 특정 namespace를 지정하는데 사용하는 핸들이다. 컨트롤러의 namespace ID를 선택하는 것은 이 규격의 범위를 벗어난다. 예를 들어 namespace ID 1은 namespace A와 연결되고 namespace ID 2는 namespace B와 연결된다. 두 namespace들은 컨트롤러 전용이며, 이 구성은 multi-path I/O 및 namespace 공유를 지원하지 않는다.

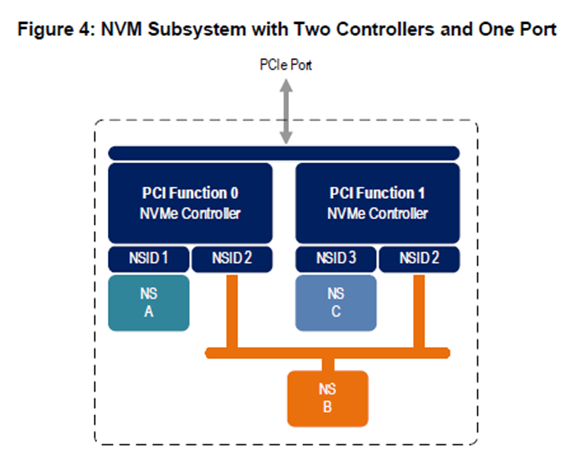

그림 4는 2개의 컨트롤러를 포함하는 단일 PCIe포트 중 Multi-Function NVM subsystem을 보여준다. 하나의 컨트롤러는 PCI Function 0과 연결되어 있고 다른 하나의 컨트롤러는 PCI Function 1과 연결되어 있다. 각 컨트롤러는 단일 private namespace와 공유된 namespace B에 대한 접근을 지원한다.

namespace ID는 특정 공유 namespace에 대한 접근할 수 있는 모든 컨트롤러에서 동일해야 한다. 이 예시에서는 두 컨트롤러 모두 namespace ID 2를 사용해 공유 namespace B에 접근한다.

각 컨트롤러에 대한 고유한 Controller Identify 데이터구조와 각 namespace에 대한 고유한 Namespace Identify 데이터구조가 있다. 공유 namespace에 접근할 수 있는 컨트롤러는 Namespace Identify 데이터 구조를 반환한다. namespace자체와 관련된 전역적으로 고유한 식별자가 있으며 동일한 공유 namespace에 대한 다수의 경로가 존재할 때 이를 결정하는 데 사용될 수 있다.

공유 namespace와 연결된 컨트롤러 namespace에서 동시에 작동할 수 있다. 개별 controller가 수행하는 작업은 명령이 제출된 controller의 write원자성 수준에서 공유 namespace에 원자이다.

write atomic level은 namespace를 공유하는 controller간 동일할 필요는 없다. 공유 namespace에 접근하는 서로 다른 controller의 command 간에 요구 사항을 수행하려면, host SW/관련 애플리케이션이 필요하다.

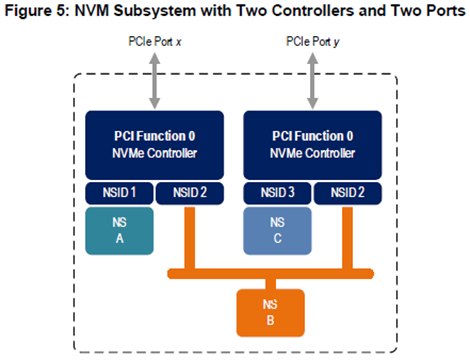

그림 5는 2개의 PCI Express 포트가 있는 NVM 서브시스템을 보여준다. 각 포트에는 컨트롤러가 연결되어 있으며, 두 컨트롤러 모두 해당 포트의 PCI Function 0에 mapping되어 있다.

이 예제의 각 PCI Express 포트는 완전히 독립적이며 자체 PCI Express Fundamental Reset 및 clock input이 있다.

포트의 재설정은 해당 포트와 연결된 컨트롤러에만 영향을 미치며, 다른 컨트롤러와 공유 namespace에는 영향을 미치지 않는다.

그림 5에 표시된 두 개의 포트는 동일한 Root Complex 또는 서로 다른 Root Complex와 연결될 수 있으며 multi-path I/O 및 I/O sharing 아키텍처를 모두 구현하는 데 사용될 수 있다.

시스템 수준의 아키텍처 측면과 PCI Express 패브릭에서 여러 포트를 사용하는 것은 해당 명세서의 범위를 벗어난다.

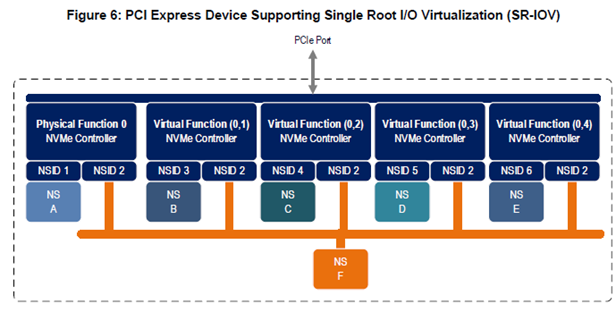

그림 6에서는 SR-IOV(Single Root I/O Virtualization)를 지원하며 하나의 물리적 기능과 4개의 가상 기능이 있는 NVM subsystem을 보여준다. NVM Express 컨트롤러는 각 컨트롤러에 개인 namespace가 있고 모든 컨트롤러가 공유하는 namespace(“NSF”)에 접근할 수 있는 각 기능과 연결되어 있다.

1.4.2 Asymmetric Controller Behavior

비대칭 controller 동작은 namespace 접근특성(성능)이 다음에 따라 달라질 수 있는 NVM 서브시스템에서 발생한다.

- NVM 서브시스템의 내부구성

- namespace에 접근하는데 사용되는 controller

비대칭 controller 동작을 제공하는 NVM 서브시스템은 섹션 8.20에 설명된 대로 비대칭 namespace 접근 보고를 지원할 수 있다.

1.5 Conversion

하드웨어의 “reserved”: 모든 비트와 레지스터에 대해 '0'을 반환

Host SW “reserved”: 모든 비트와 레지스터를 0h의 값으로 작성해야 한다.

레지스터 섹션(즉, 섹션 2 및 섹션 3) 내에는 다음 용어와 약어가 사용된다.

일부 레지스터 필드의 경우 해당 필드가 RW, RWC 또는 RO 중 어느 것인지에 대한 구현이다. 일반적으로 RW/RO 또는 RWC/RO로 표시되어 기능이 지원되지 않는 경우 필드만 읽음을 나타낸다.

문서에서 레지스터 필드가 참조될 때 사용되는 규칙은 "Register Symbol.Field Symbol"이다. 예를 들어, PCI command 레지스터 Parity 오류 응답 활성화 bit는 “CMD.PEE”라는 이름으로 참조된다.

레지스터 필드가 bit의 배열인 경우 필드를 "Register Symbol.Field Symbol (array에서 element로 오프셋)"이라고 한다.

0의 기준 값은 숫자 0h가 1h의 값을 나타내고, 1h가 2h를 나타내고, 2h가 3h를 나타내는 등의 번호 부여 방식이다. 이 번호 체계에서는 0h의 값을 나타내는 방법이 없으며, 본 명세서에서의 값들은 특별한 규정이 없는 한 1-기반(즉, 숫자 1h는 1h의 값을 나타내고, 2h는 2h를 나타내는 등)이다.

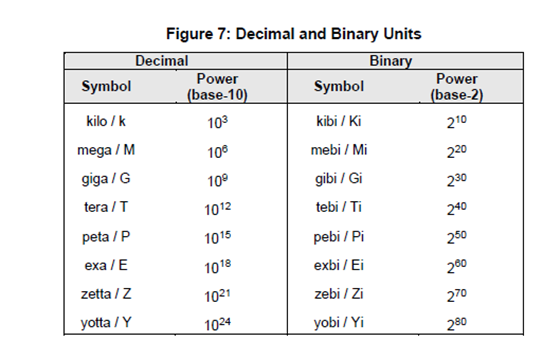

크기 값은 이진 단위 또는 십진 단위로 표시된다. 이 값들을 나타내기 위해 사용된 기호는 그림 7과 같다.

^ 연산자는 해당 숫자, 기호 또는 식을 올릴 거듭제곱을 나타내는 데 사용된다.

일부 파라미터는 ASCII 문자열로 정의된다. ASCII 문자열은 코드 값 20h ~ 7Eh만 포함해야 한다. 문자열 "Copyright"의 경우 문자 "C"는 첫 번째 바이트, 문자 "o"는 두 번째 byte이다. 문자열은 정당한 상태로 유지되며 필요한 경우 오른쪽에 공백(ASCII 문자 20h)을 추가해야 한다. 16진수 ASCII 문자열은 코드 값의 하위 집합인 "0" ~ "9", "A" ~ "F" 대문자, "a" ~ "f" 소문자를 사용하는 ASCII 문자열이다.

16진수(즉, 베이스 16) 숫자는 소문자 "h" 접미사(예를 들어, 0FFFh, 80h)로 기록된다. 8자리보다 큰 16진수는 8자리(예를 들어, 1E_DEADBEEFh)의 각 그룹을 나누는 "(언더바)" 문자로 표시된다.

이진수(즉, 베이스 2) 숫자는 소문자 "b" 접미사(예를 들어, 1001b, 10b)로 작성되며,

4자리보다 큰 이진수는 4자리의 각 그룹(예: 1000_0101_0010b)을 나누는 밑줄 문자로 작성된다.

다른 모든 숫자들은 10진법이다. 본 명세서에서 10진법은 소문자 b 또는 소문자 h(예를 들어, 175)가 바로 뒤따르지 않는 서양-아랍 숫자 0~9로만 이루어진 숫자열로 표시된다. 이 규격은 십진법 숫자를 나타내기 위해 다음과 같은 규칙을 사용한다.

A. 10진법 구분자(즉, 정수 부분과 분수 부분을 구분하는 것)는 마침표이다.

B. 수천 개의 구분자(즉, 숫자의 일부에서 소수 셋째 자리의 그룹을 구분하는 것)는 쉼표이다.

C. 수천 개의 구분자는 숫자의 정수 부분에만 사용되고, 숫자의 분수 부분에는 사용되지 않는다.

D. 1년 동안의 십진수 표현에는 쉼표가 포함되지 않는다. (예: 2,019 대신 2019).

1.6 Definitions

1.6.1 Admin Queue

Admin Queue는 SQ와 식별자가 0인 CQ이다. admin command를 제출하고 완료하기 위해 Admin SQ와 Admin CQ는 쌍으로 이루어져 있다.

1.6.2 administartive controller

Host가 NVM 서브시스템을 관리할 수 있게 하는 controller이다.

Admin 컨트롤러 I/O Queue를 가지지 않으며, Logical blocks와 관련된 metadata에 대한 접근 권한을 제공한다. namespace를 지원하지 않는다. (활성 NSID가 전혀 없음)

1.6.3 arbitration burst

Round robin/weighted round robin을 사용하는 SQ로부터 한 번에 처리 가능한 commands의 최대 수를 말한다.

1.6.4 arbitration mechanism

SQ에서 controller에 의해 수행되기 위한 command를 결정하기 위해 사용된다.

1.6.5 Cache

NVM subsystem을 사용하는 data storage area

1.6.6 Candidate Command

Candidate Command는 컨트롤러로 전송된 제출된 command이며 컨트롤러는 처리 준비가 완료된 것으로 간주된다.

1.6.7 Command Completion

Command는 컨트롤러가 command 처리를 완료하고 CQ Entry에 상태 정보를 업데이트하고 CQ Entry를 관련 CQ에 게시하면 완료된다.

1.6.8 Command Submission

NVMe over PCIe 구현의 경우, Submission Queue Tail Doorbell Write가 완료되면 command가 전송된다. 이는 Submission Queue Tail Pointer 값을 command가 배치된 Submission Queue 슬롯을 지나 이동한다.

1.6.9 Controller

컨트롤러는 호스트와 NVM 서브시스템 사이의 인터페이스이다.

컨트롤러에는 세 가지 유형이 있습니다:

a) I/O 컨트롤러;

b) 검색 컨트롤러; 및

c) 관리 컨트롤러.

1.6.10 directive

호스트 및 NVM 서브시스템 또는 컨트롤러 정보 교환 방법. 정보는 Directive Send 및 Directive Receive 명령을 사용하여 전송될 수 있습니다. I/O 명령의 서브세트는 연관된 I/O 명령에 특정한 더 많은 정보를 전달하기 위해 Directive Type 필드 및 Directive Specific 필드를 포함할 수 있습니다. 섹션 9를 참조하십시오.

1.6.11 discovery controller

호스트가 Discovery Log Page를 검색할 수 있도록 하는 기능을 노출하는 컨트롤러이다. Discovery 컨트롤러는 I/O Queue를 구현하지 않거나 비휘발성 메모리 저장 매체에 대한 액세스를 제공하지 않는다. 자세한 내용은 NVMe over Fabrics 사양을 참조하십시오

1.6.12 emulated controller

SW에 정의된 NVM Express 컨트롤러. Emulated된 컨트롤러는 기본 물리적 NVMe 컨트롤러(예를 들어, 물리적 PCIe 기능)를 가질 수도 있고 가지지 않을 수도 있다.

1.6.13 Endurance Group

성능과 수명의 증가를 위해 NVM Set를 하나로 묶은 것

1.6.14 Extended LBA

extended LBA는 LBA 데이터와 연속적으로 LBA와 관련된 메타데이터가 전송될 때 생성되는 더 큰 LBA이다. 그림 453을 참조하십시오.

1.6.15 firmware slot

펌웨어 슬롯은 펌웨어 이미지를 저장하는 데 사용되는 NVM 서브시스템의 위치이다. NVM 서브시스템은 1개에서 7개의 펌웨어 이미지를 저장한다.

1.6.16 host

하나 이상의 컨트롤러를 통해 NVM 하위 시스템에 인터페이스하고 Submission Queue에 command를 제출하고 Complete Queue에서 command completion을 검색하는 Entity이다.

1.6.17 host-accessible memory

호스트가 액세스할 수 있는 메모리(예: host memory, CMB(Controller Memory Buffer), PMR(Persistent Memory Region))

1.6.18 host memory

호스트와 컨트롤러 모두에 의해 읽고 쓸 수 있고 컨트롤러에 의해 노출되지 않는 메모리(즉, controller memory buffer 또는 persistent memory region). Host memory는 호스트 내부 또는 외부(예를 들어, 호스트도 컨트롤러도 아닌 장치에 의해 노출되는 메모리 영역)에 구현될 수 있다.

1.6.19 I/O command

I/O command는 I/O Submission Queue에 제출되는 command이다.

1.6.20 I/O Completion Queue

I/O Complete Queue는 command completion을 나타내는 데 사용되는 Complete Queue이며 하나 이상의 I/O Submission Queue와 연관되어 있다. I/O Complete Queue 식별자는 1 ~ 65535이다.

1.6.21 I/O Controller

I/O 큐를 구현하고 비휘발성 메모리 저장 매체에 액세스하기 위해 사용되는 컨트롤러

1.6.22 I/O Submission Queue

I/O Submission Queue는 컨트롤러에서 실행하기 위한 I/O command(예: NVM command set에 대한 읽기, 쓰기)을 제출하는 데 사용되는 Submission Queue이다. I/O Submission Queue 식별자는 1에서 65,535이다.

1.6.23 LBA range

시작 LBA 및 논리 블록 수에 의해 지정된 연속된 논리 블록의 모음이다.

1.6.24 Logical Block

Read/Write command의 주소 지정 가능한 가장 작은 데이터 단위이다.

1.6.25 Logical Block Address(LBA)

일반적으로 LBA라고 하는 논리 블록의 주소이다.

1.6.26 Metadata

메타데이터는 특정 데이터와 관련된 상황 정보이다. 호스트는 컨트롤러에 의해 저장 공간이 제공되는 경우, NVM 서브시스템에 의해 저장될 메타데이터를 포함할 수 있다. 메타데이터는 보호 정보(Protection Information)를 포함할 수 있다(섹션 8.3 참조).

1.6.27 Namespace

Logical Block(Read/Write command의 주소 지정 가능한 가장 작은 데이터 단위)들로 포맷될 수 있는 비휘발성 메모리의 양이다. 포맷될 때, 크기 n의 namespace는 0에서 (n-1)까지의 논리 블록 주소를 갖는 논리 블록들의 집합이다.

- 파티션 나누듯 SSD 내의 저장 공간을 논리적으로 분할하여 서로 다른 별도의 저장 장치로 보이게 하는 것

- 다만 파티션과 조금 다른 점이라면 Namespace로 나눈 곳은 아까 말씀드렸듯 하나의 또 다른 SSD로 인식되어 다시 파티션으로 나눌 수 있다는 점

- 보통 보안, 복구, 쓰기 성능, 내구성 향상을 위한 프로비저닝 등에 사용하고 있다고 한다.

1.6.28 Namespace ID (NSID)

NSID를 포함하는 SQE의 Namespace 또는 필드 이름에 대한 액세스를 제공하기 위해 컨트롤러가 사용하는 식별자이다(그림 106 참조). 유효한 NSID, 유효하지 않은 NSID, 유효하지 않은 NSID, 활성 NSID, 비활성 NSID, 할당된 NSID 및 할당되지 않은 NSID의 정의는 섹션 6.1을 참조하십시오.

1.6.29 NVM

NVM은 비휘발성 메모리의 약자이다.

1.6.30 NVM Set

내구성 그룹의 NVM 일부. 섹션 4.9를 참조하십시오.

1.6.31 NVM Subsystem

NVM subsystem은 하나 이상의 컨트롤러, 0 이상의 namespace, 및 하나 이상의 포트를 포함한다. NVM subsystem은 비휘발성 메모리 저장 매체 및 NVM subsystem 내의 컨트롤러(들)와 비휘발성 메모리 저장 매체 사이의 인터페이스를 포함할 수 있다.

1.6.32 Primary Controller

가상화 관리(Virtualization Management) command을 지원하는 NVM Express 컨트롤러. NVM subsystem에는 여러 개의 기본 컨트롤러가 포함될 수 있다. NVM 서브시스템의 보조 컨트롤러는 동적 리소스 관리를 위해 기본 컨트롤러에 의존한다(섹션 8.5 참조).

기본 컨트롤러의 예로는 NVM Express 인터페이스와 가상화 향상 기능을 지원하는 PCI Express SR-IOV 물리적 기능이 있다(섹션 8.5.4 참조).

1.6.33 Private Namespace

한 번에 하나의 컨트롤러에만 연결할 수 있는 namespace이다. 호스트는 namespace 데이터 구조 식별의 namespace multi path I/O 및 NMIC(네임스페이스 공유 기능) 필드 값으로 네임스페이스가 개인 네임스페이스인지 또는 공유 네임스페이스인지를 결정할 수 있다.

1.6.34 Runtime D3 (Power Removed)

Runtime D3(RTD3)에서 메인 전원은 컨트롤러에서 제거된다. 보조 전원은 제공될 수도 있고 제공되지 않을 수도 있다. PCI Express의 경우 RTD3는 D3 Cold Power 상태이다(섹션 8.4.4 참조).

1.6.35 Sanitize Operation

Cache 또는 비휘발성 미디어에서 이전 사용자 데이터를 복구할 수 없도록 NVM subsystem의 모든 사용자 데이터가 변경되는 프로세스.

1.6.36 Secondary Controller

일부 컨트롤러 리소스의 관리를 위해 NVM subsystem의 기본 컨트롤러에 의존하는 NVM Express 컨트롤러(섹션 8.5 참조).

보조 컨트롤러의 예로는 NVM Express 인터페이스를 지원하고 기본 컨트롤러로부터 리소스를 수신하는 PCI Express SR-IOV Virtual Function이 있다(섹션 8.5.4 참조).

1.6.37 Shared Namespace

NVM 서브시스템에서 둘 이상의 컨트롤러에 동시에 연결될 수 있는 namespace이다. 호스트는 namespace 데이터 구조 식별의 namespace multi-path I/O 및 NMIC(Namespace Sharing Capabilities) 필드 값에 의해 네임스페이스가 개인 네임스페이스인지 또는 공유 네임스페이스인지 여부를 결정할 수 있다.

1.6.38 User Data

호스트가 저장하고 나중에 지원하는 경우 메타데이터를 포함하여 검색할 수 있는 데이터로 구성된 네임스페이스에 저장된 데이터이다.

1.7 Keywords

여러 수준의 요구 사항을 구분하기 위해 여러 키워드가 사용된다.

1.7.1 Mandatory

본 명세서에서 정의한 대로 구현할 항목을 나타내는 키워드이다.

1.7.2 May

암시된 선호도가 없는 선택의 유연성을 나타내는 키워드이다.

1.7.3 Optional

본 명세서에 의해 요구되지 않는 특징을 기술하는 키워드. 단, 본 명세서에 의해 정의된 임의의 선택적 특징이 구현되는 경우, 해당 특징은 본 명세서에 의해 정의된 방식으로 구현되어야 한다.

1.7.4 R

"R"은 그림 또는 표가 "reserved"라는 전체 단어에 대한 충분한 공간을 제공하지 못할 때 "reserved"의 약자로 사용된다.

1.7.5 Reserved

향후 표준화를 위해 설정 측에 있는 bit, byte, word, field 및 opcode 값을 나타내는 키워드이다. 이들의 사용 및 해석은 본 명세서 또는 다른 명세서의 향후 확장자에 의해 지정될 수 있다. reserved bit, byte, word, field 또는 register는 0h로 지워지거나 본 명세서의 향후 확장자에 따라 지워진다. command 또는 레지스터 쓰기의 수신자는reserved bit, byte, word 또는 field를 확인할 필요가 없다. command에서 정의된 필드의 reserved 코드 값 수신은 오류로 보고되어야 한다. reserved 코드 값을 컨트롤러 레지스터 필드에 쓰면 정의되지 않은 결과가 발생한다.

1.7.6 Shall

필수 요건을 나타내는 키워드이다. 설계자는 사양을 준수하는 다른 제품과의 상호 운용성을 보장하기 위해 그러한 모든 필수 요건을 구현해야 한다.

1.7.7 Should

강력하게 선호하는 대안으로 선택의 유연성을 나타내는 키워드 "추천한다"는 문구에 해당한다.

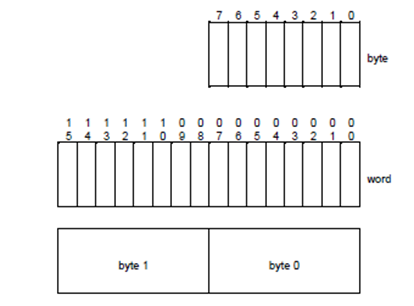

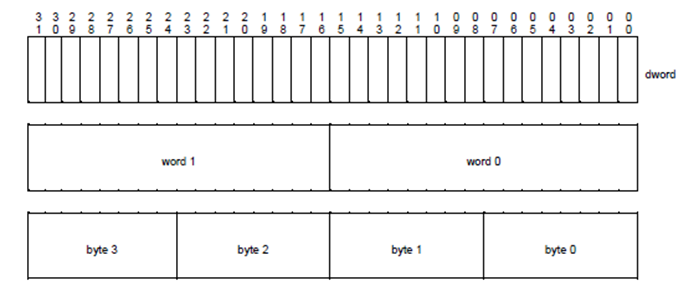

1.8 Byte, Word, and Dword Relationship

그림은 byte, word 및 dword 간의 관계를 보여준다. qword(4중 단어)는 단어의 4배 크기의 데이터 단위이며, 공간 제약으로 인해 표시되지 않는다. 이 명세서에서는 특별한 규정이 없는 한 작은 endian 형식의 데이터를 지정한다.