Controller register는 MLBAR/MUBAR 레지스터(PCI BAR0 및 BAR1)에 있으며, 이 register는 in-order access와 variable access 폭을 지원하는 메모리 공간에 매핑된다. 많은 컴퓨터 아키텍처에서 메모리 공간을 캐시 불가능으로 지정하면 이러한 동작이 발생한다. Host는 잠금 access를 발행하지 않아야 하며, Host는 resister에 지정된 너비를 사용하거나 정렬된 32비트 access를 사용하여 register에 access해야 한다. 이러한 Host 요구 사항 중 하나를 위반하면 정의되지 않은 동작이 발생한다.

두 개 이상의 register 중 해당 대상에 대한 access는 지원되지 않는다.

register 내의 모든 reserved register 및 모든 reserved bits는 읽기 전용이며 읽기 시 0h를 반환한다. SW는 0h를 반환하는 것에 의존해서는 안 된다.

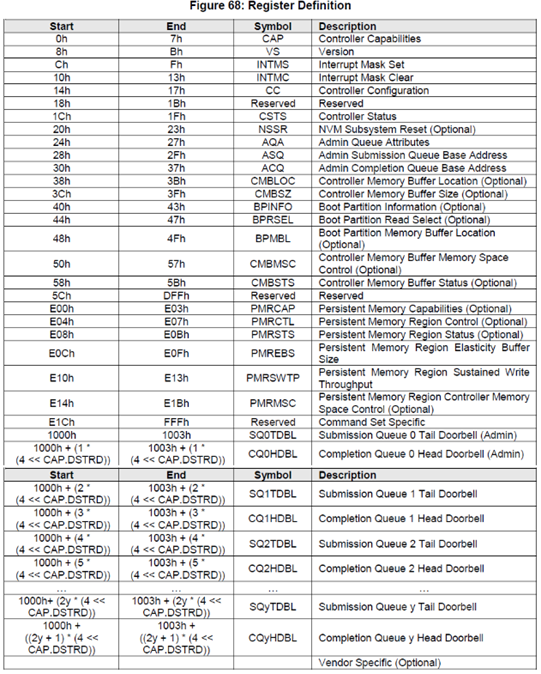

3.1 Register Definition

그림 68은 컨트롤러에 대한 register map을 설명한다.

Vendor Specific Address 범위는 컨트롤러가 지원하는 마지막 Doorbell 이후에 시작하여 BAR0/1 지원 범위의 끝까지 계속된다. Vendor Specific Address 범위의 시작은 동일한 위치에서 시작하며 할당된 Doorbell의 수에 의존하지 않는다.

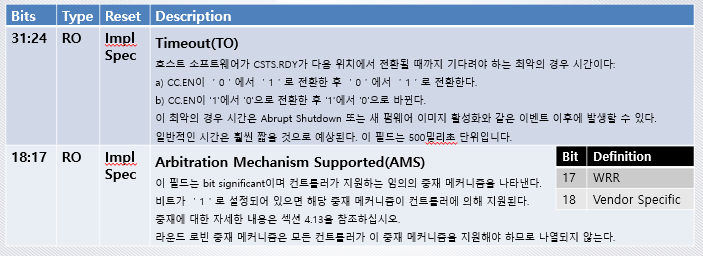

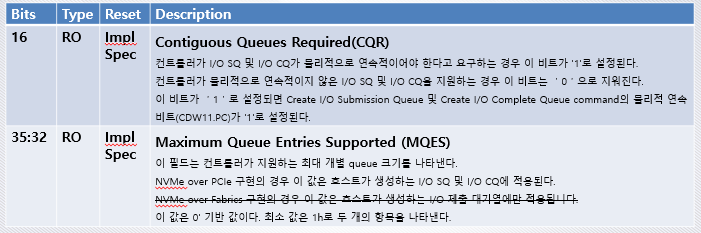

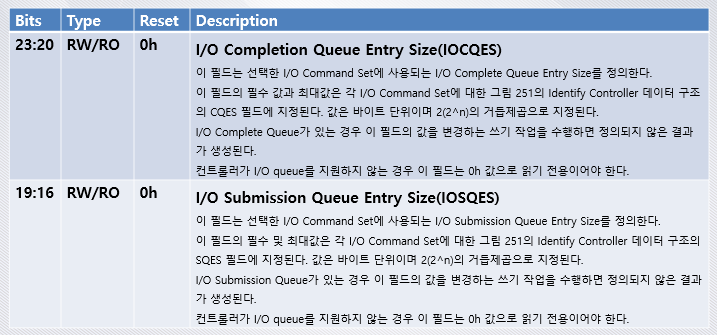

3.1.1 offset 0h: CAP -Controller Capabilites

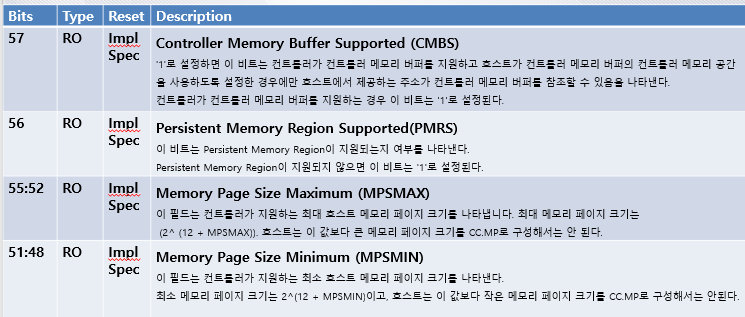

이 레지스터는 컨트롤러가 소프트웨어를 호스팅하는 기본 기능을 나타낸다.

3.1.2 Offset 8h : VS - Version

이 레지스터는 컨트롤러 구현이 지원하는 NVM Express 기본 사양의 주 버전, 부 버전 및 3차 버전을 나타낸다. 이 사양의 유효한 버전은 1.0, 1.1, 1.2, 1.2.1, 1.3 및 1.4이다.

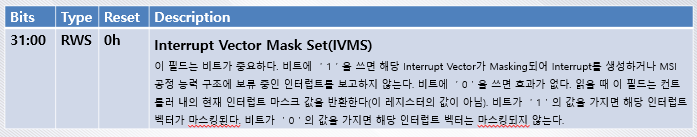

3.1.3 Offset Ch: INTMS - Interrupt Mask Set

이 레지스터는 핀 기반 인터럽트, 단일 메시지 MSI 또는 다중 메시지 MSI를 사용할 때 인터럽트를 masking하는 데 사용된다. MSI-X를 사용할 때는 MSI-X의 일부로 정의된 인터럽트 마스크 테이블을 사용하여 인터럽트를 masking해야 한다. Host SW는 MSI-X용으로 구성된 경우 이 레지스터에 액세스할 수 없다. MSI-X용으로 구성된 경우 액세스가 정의되지 않는다. 인터럽트 동작 요구 사항은 섹션 7.5를 참조하십시오.

3.1.4 Offset 10h: INTMC – Interrupt Mask Clear

이 레지스터는 핀 기반 인터럽트, 단일 메시지 MSI 또는 다중 메시지 MSI를 사용할 때 인터럽트의 마스크를 해제하는 데 사용된다. MSI-X를 사용할 때는 MSI-X의 일부로 정의된 인터럽트 마스크 테이블을 사용하여 인터럽트의 마스크를 해제해야 합니다. 호스트 소프트웨어는 MSI-X용으로 구성된 경우 이 레지스터에 액세스할 수 없다. MSI-X용으로 구성된 경우 액세스가 정의되지 않는다. 인터럽트 동작 요구 사항은 섹션 7.5를 참조하십시오

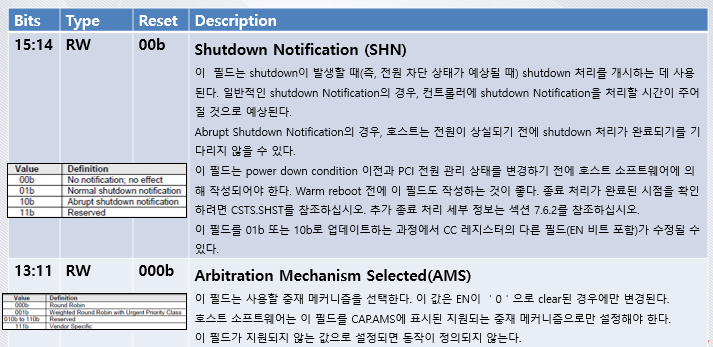

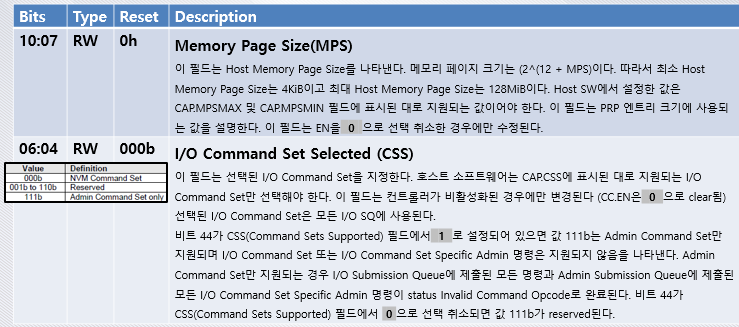

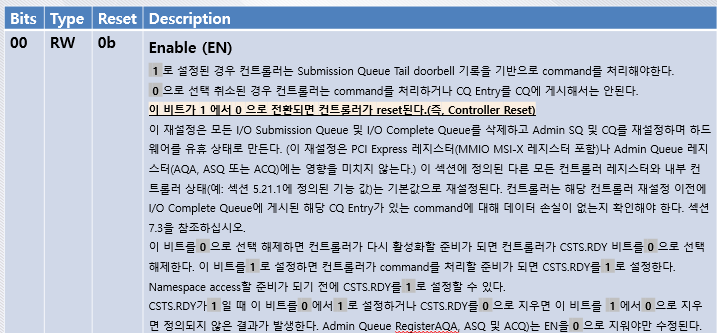

3.1.5 CC - Controller Configuration

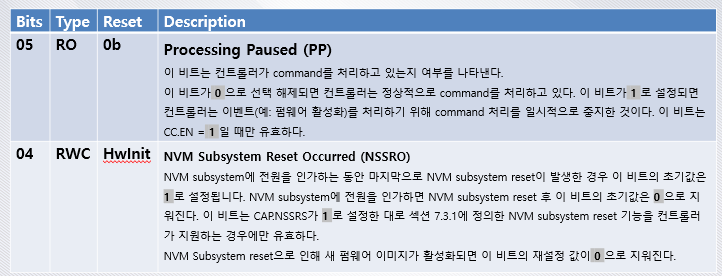

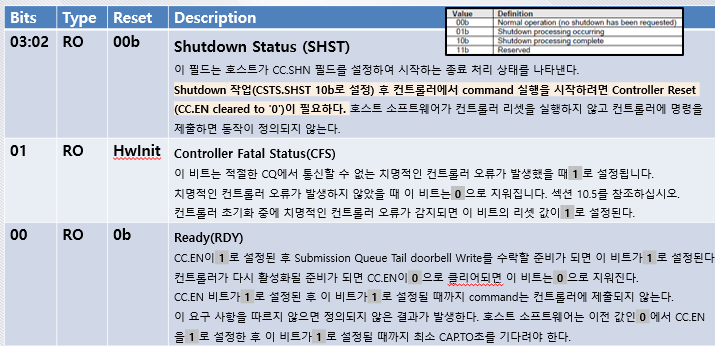

3.1.6 Offset 1Ch: CSTS - Controller Status

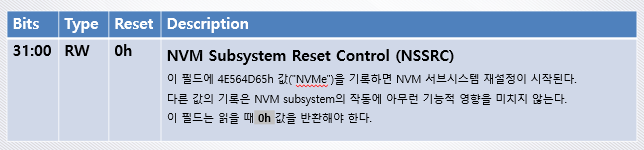

3.1.7 Offset 20h: NSSR - NVM Subsystem Reset

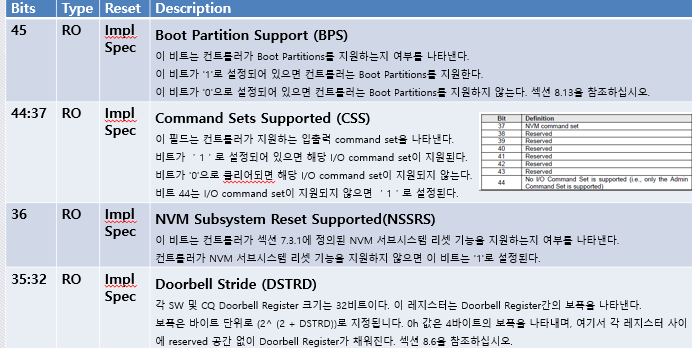

이 옵션 레지스터는 host SW에 NVM subsystem reset을 시작하는 기능을 제공한다. 이 레지스터의 지원은 NVM 서브시스템 리셋 지원(CAP.NSSRS) 필드의 상태로 표시된다. 레지스터가 지원되지 않으면 레지스터가 차지하는 주소 범위가 reserved된다. 섹션 7.3.1을 참조하십시오.

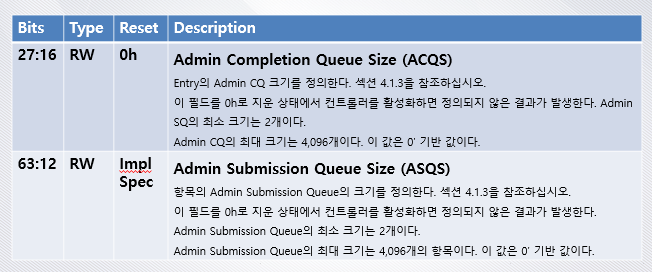

3.1.8 Offset 24h: AQA - Admin Queue Attributes

이 레지스터는 Admin Submission Queue와 Admin Complete Queue에 대한 속성을 정의한다. Admin Submission Queue와 Admin Complete Queue에 대한 Queue Identifier는 0h이다. Admin Submission Queue의 우선 순위는 선택한 중재 메커니즘에 의해 결정된다. 섹션 4.13을 참조하십시오. Admin Submission Queue와 Admin Complete Queue는 물리적으로 연속된 메모리에 있어야 한다.

참고: UEFI는 부팅 작업 중에 사용하는 것이 좋습니다. 낮은 메모리 환경(예: 레거시 BIOS 환경의 옵션 ROM)에서는 필요한 제출 및 완료 대기열을 할당하기에 충분한 메모리가 없을 수 있습니다. 이러한 유형의 조건에서 컨트롤러의 낮은 메모리 작업은 벤더에 따라 다르다.

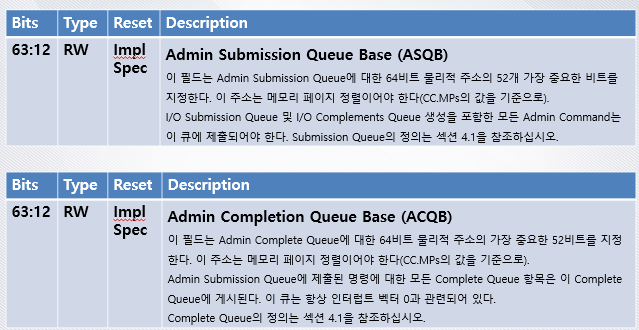

3.1.9 Offset 24h: ASQ – Admin Submission Queue Base Address

이 레지스터는 Admin Submission Queue의 기본 메모리 주소를 정의한다.

3.1.10 Offset 30h: ACQ – Admin Completion Queue Base Address

이 레지스터는 Admin Completion Queue의 기본 메모리 주소를 정의한다.

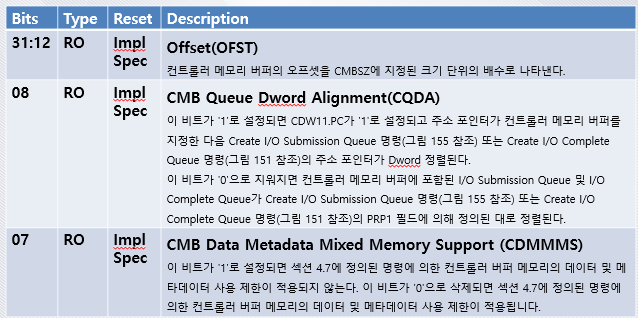

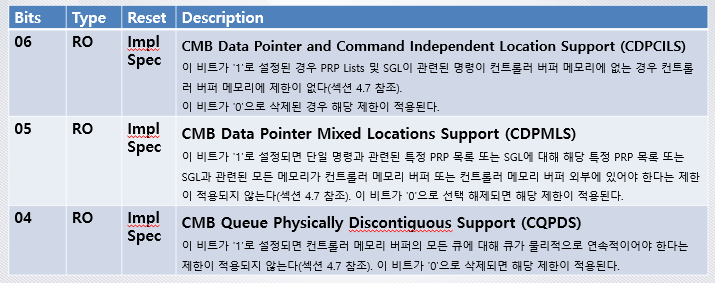

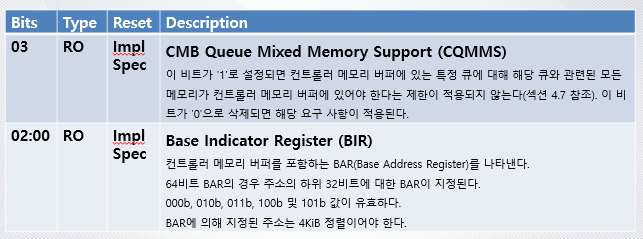

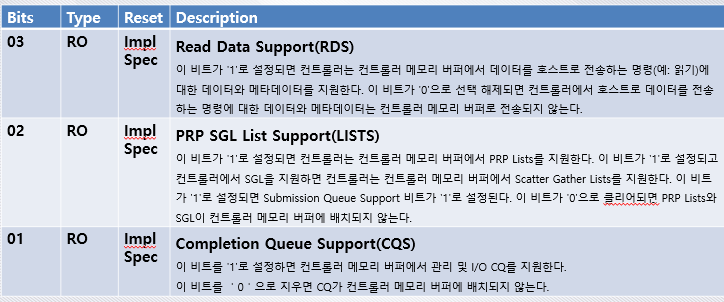

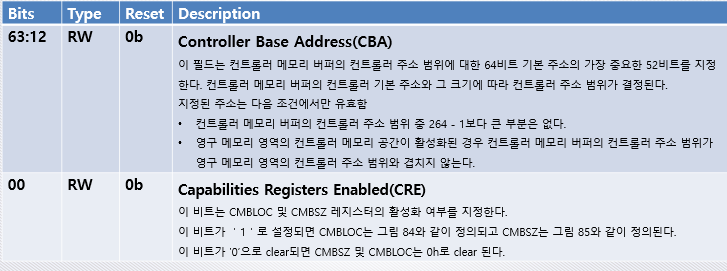

3.1.11 Offset 38h: CMBLOC – Controller Memory Buffer Location

이 옵션 레지스터는 컨트롤러 메모리 버퍼의 위치를 정의한다(섹션 4.7 참조). 컨트롤러가 컨트롤러 메모리 버퍼(CAP.CMBS)를 지원하지 않는 경우 이 레지스터는 reserved된다. 컨트롤러가 컨트롤러 메모리 버퍼를 지원하고 CMBSC.CRE가 '0'으로 클리어되면 이 레지스터는 0h로 클리어 된다.

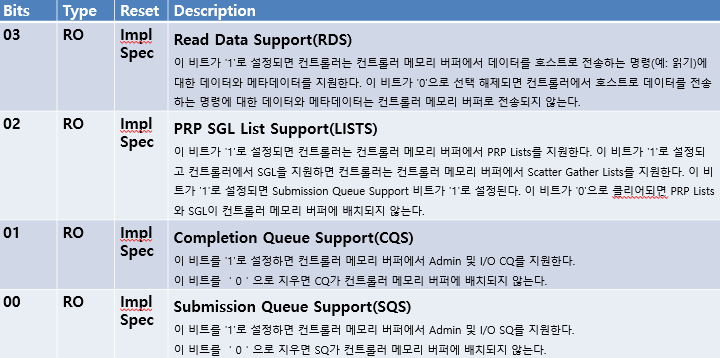

3.1.12 Offset 3Ch: CMBSZ – Controller Memory Buffer Size

이 옵션 레지스터는 컨트롤러 메모리 버퍼의 크기를 정의한다(섹션 4.7 참조). 컨트롤러가 컨트롤러 메모리 버퍼 기능을 지원하지 않거나 컨트롤러가 컨트롤러 메모리 버퍼(CAP.CMBS) 및 CMBSC.CRE를 지원하는 경우 '0'으로 선택 해제되면 이 레지스터는 0h로 선택 해제된다.

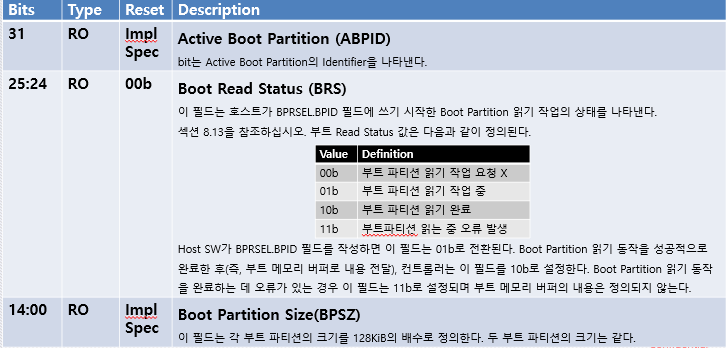

3.1.13 Offset 40h: BPINFO – Boot Partition Information

이 옵션 레지스터는 부트 파티션의 특성을 정의한다(섹션 8.13 참조).

컨트롤러가 부트 파티션 기능을 지원하지 않는 경우 이 레지스터는 0h로 삭제된다.

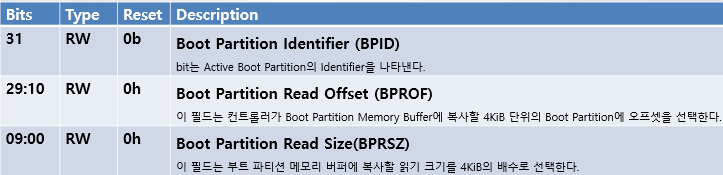

3.1.14 Offset 44h: BPRSEL – Boot Partition Read Select

이 옵션 레지스터는 부팅 파티션(섹션 8.13 참조)의 데이터를 컨트롤러에서 호스트로 전송하는 데 사용된다. 컨트롤러가 부팅 파티션 기능을 지원하지 않는 경우 이 레지스터는 0h로 지워진다.

호스트가 부트 파티션의 끝을 넘어서 읽기를 시도하는 경우(즉, 부트 파티션 읽기 오프셋 + 부트 파티션 읽기 크기, 바이트 단위), 컨트롤러는 BPINFO.BRS 필드에 데이터를 전송하지 않고 오류를 보고하지 않는다.

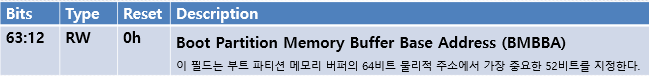

3.1.15 Offset 48h: BRMBL – Boot Partition Memory Buffer Location(Optional)

이 옵션 레지스터는 부트 파티션을 읽을 때 데이터의 대상으로 사용되는 메모리 버퍼를 지정한다(섹션 8.13 참조). 컨트롤러가 부트 파티션 기능을 지원하지 않는 경우 이 레지스터는 0h로 지워진다.

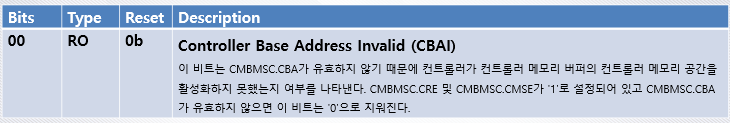

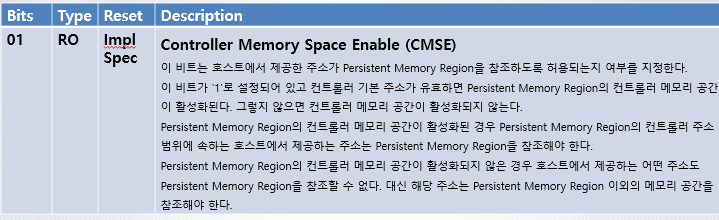

3.1.16 Offset 50h: CMBMSC – Controller Memory Buffer Memory Space Control

이 옵션 레지스터는 컨트롤러가 호스트에서 제공하는 주소로 컨트롤러 메모리 버퍼를 참조하는 방법을 지정한다. 컨트롤러가 컨트롤러 메모리 버퍼(CAP.CMBS)를 지원하는 경우 이 레지스터는 필수이며, 그렇지 않으면 이 레지스터가 reserved되어 있다.

이 레지스터는 컨트롤러 리셋 및 기능 레벨 리셋 모두에 의해 리셋되지 않고 다른 모든 컨트롤러 레벨 리셋에 의해 리셋된다.

3.1.17 Offset E00h: PMRCAP – Persistent Memory Buffer Status

이 옵션 레지스터는 컨트롤러 메모리 버퍼의 상태를 나타낸다. 컨트롤러가 컨트롤러 메모리 버퍼(CAP.CMBS)를 지원하는 경우 이 레지스터는 필수이다. 그렇지 않으면 이 레지스터는 reserved되어 있다.

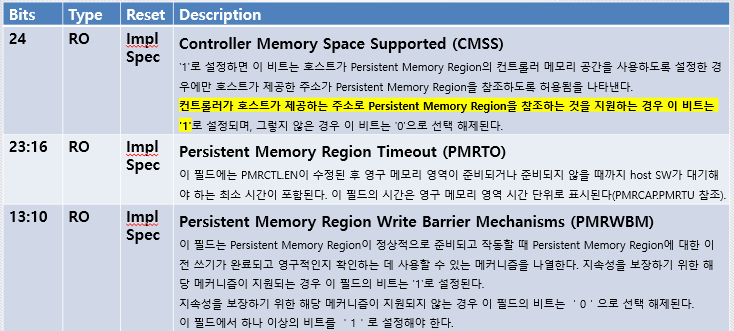

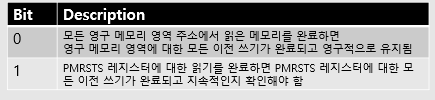

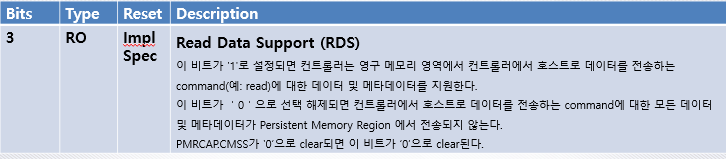

3.1.18 Offset E00h: PMRCAP 0 Persistent Region Capabilities

이 레지스터는 Persistent Memory Region(영구 메모리 영역)의 기능을 나타낸다. 컨트롤러가 Persistent Memory Region(영구 메모리 영역) 기능을 지원하지 않으면 이 레지스터는 0h로 지워진다.

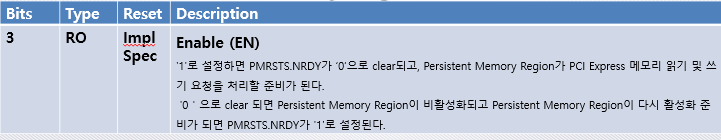

3.1.19 Offset E04h: PMRCTL – Persistent Memory Region Control

이 옵션 레지스터는 Persistent Memory Region(영구 메모리 영역)의 작동을 제어한다. 컨트롤러가 Persistent Memory Region(영구 메모리 영역) 기능을 지원하지 않으면 이 레지스터는 0h로 지워진다.

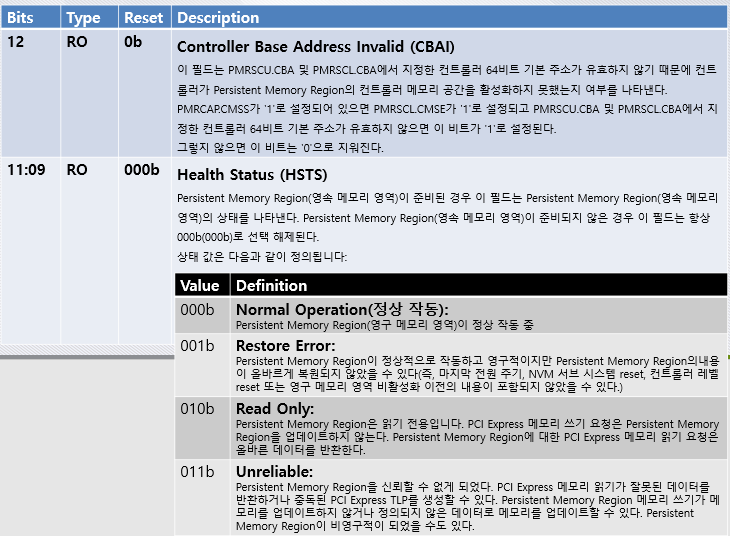

3.1.20 Offset E08h: PMRSTS – Persistent Memory Region Status

이 옵션 레지스터는 Persistent Memory Region(영구 메모리 영역)의 상태를 제공한다. 컨트롤러가 Persistent Memory Region(영구 메모리 영역) 기능을 지원하지 않으면 이 레지스터는 0h로 지워진다.

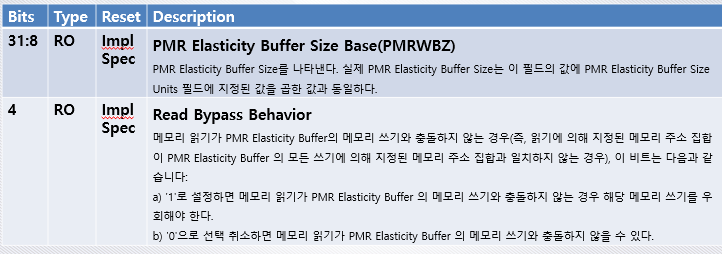

3.1.21 Offset E0Ch: PMREBS – Persistent Memory Region Elasticity Buffer Size

이 옵션 레지스터는 호스트에 PMR elasticity buffer의 크기를 식별한다. 이 레지스터의 값이 0h이면 호스트에 PMR elasticity buffer의 존재 또는 크기에 관한 정보가 없음을 나타낸다.

3.1.22 Offset E10h: PMRSWTP – Persistent Memory Region Sustained Write Throughput

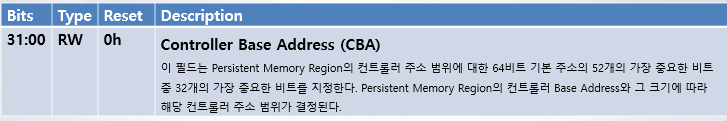

3.1.23 Offset E14h: PMRMSCL – Persistent Memory Region Memory Space Control Lower

3.1.24 Offset E18h: PMRMSCU – Persistent Memory Region Memory Space Control Upper

이 옵션 레지스터와 PMRSCL 레지스터는 컨트롤러가 호스트에서 제공한 주소로 Persistent Memory Region을 참조하는 방법을 지정한다. 컨트롤러가 Persistent Memory Region의 컨트롤러 메모리 공간(PMRCAP.CMSS)을 지원하는 경우 이 레지스터는 필수이며, 그렇지 않으면 이 레지스터가 reserved되어 있다. 호스트는 정렬된 32비트 액세스로 이 레지스터에 액세스해야 한다.

이 레지스터는 controller reset에 의해 reset되지 않는다.

3.1.25 Offset (1000h + ((2y) * (4 << CAP.DSTRD))): SQyTDBL – Submission Queue y Tail Doorbell

이 레지스터는 Submission Queue y에 대한 Tail Entry Pointer를 업데이트하는 Doorbell Register를 정의한다. y의 값은 Queue Identifier와 동일하다. 이는 처리를 위해 새로운 command가 제출되었음을 컨트롤러에 나타낸다.

호스트는 Doorbell Register를 읽어서는 안 된다. Doorbell Register를 읽었을 경우 반환되는 값은 vendor이다. 존재하지 않는 SQ Tail Doorbell에 쓰는 것은 정의되지 않은 결과를 가져온다.

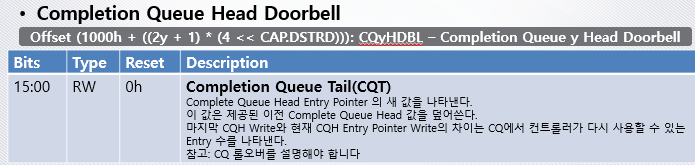

3.1.26 Offset (1000h + ((2y + 1) * (4 << CAP.DSTRD))): CQyHDBL – Completion Queue y Head Doorbell

이 레지스터는 Complete Queue y에 대한 Head Entry Pointer를 업데이트하는 Doorbell Register를 정의한다. y의 값은 Queue Identifier와 동일하다. 이는 호스트 소프트웨어에서 처리한 Complete Queue Entry를 나타낸다.

호스트는 Doorbell Register를 읽어서는 안 된다. Doorbell Register를 읽었을 경우 반환되는 값은 vendor별로 다르다. 존재하지 않는 CQ Head Doorbell에 쓰는 것은 정의되지 않은 결과를 가져온다.

Host SW는 특정 또는 SQ에 사용 가능한 Entry이 있는지 여부에 관계없이 CQ 내에서 CQ Entry를 계속 처리해야 한다.

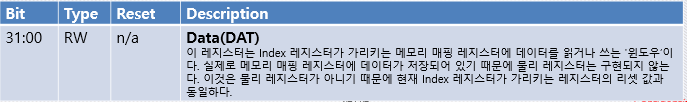

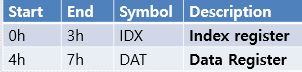

3.2 Index/Data Pair registers (Optional)

Index/DataPair 레지스터는 host SW I/O space based 레지스터를 사용하여 NVM Express 메모리 매핑 레지스터에 액세스할 수 있는 메커니즘을 제공한다. 지원되는 경우 이러한 레지스터는 BAR2에 있다. PC 기반 플랫폼에서 'real-mode'(8086 모드)로 동작하도록 작성된 호스트 소프트웨어(BIOS, Option ROM, OS)는 주소 공간이 메모리 매핑되고 1 MiB 이상으로 매핑된 경우 PCI Express 함수의 주소 공간에 있는 레지스터에 액세스할 수 없다.

인덱스/데이터 쌍 메커니즘을 사용하면 호스트 소프트웨어가 직접 메모리 매핑 액세스 대신 간접 I/O 주소 지정을 사용하여 모든 메모리 매핑 NVM Express 레지스터에 액세스할 수 있습니다.

참고: UEFI 드라이버는 1 MiB 제한에 직면하지 않으므로 EFI를 사용할 때 Index/Data Pair 메커니즘에 대한 요구 사항이 없다. 따라서 이 기능은 컨트롤러가 지원하는 옵션이며 UEFI가 널리 보급됨에 따라 폐지될 수 있다.

3.2.1 Restrictions

Host SW는 Index/Data Pair 기반 액세스 방식과 Direct Memory Mapped 액세스 방식을 번갈아 사용해서는 안 된다. 컨트롤러 레지스터에 직접 메모리 매핑 액세스를 사용한 후에는 Index/Data Pair 메커니즘을 사용해서는 안 된다.

3.2.2 Register Definition

다음 레지스터는 Index/Data Pair 구현에 필요한 레지스터에 대해 설명한다.

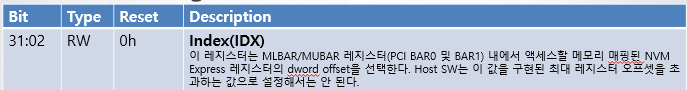

3.2.3 Offset 0h:IDX – Index Register

3.2.4 Offset 4h:DAT – Data Register