시간 및 기억소자들

- sequential logic의 경우 과거의 출력값에도 영향을 받기 때문에 memory device가 필요하며 현재의 input 이외의 과거 상태 및 현재 상태 값들을 고려하여 출력이 결정되므로 time을 나타내는 device가 필요하다.

- computer에서 시간을 나타내는 device는 Oscillator와 counter가 대표적이며 기억소자는 단순히

ORgate에 feedback을 추가한 경우에서부터 RAM을 거쳐 HDD, SDD까지 다양하다. - 여기서는 gate기반의 구현물부터 출발할 것이다.

Oscillator

-

일정 시간에 맞춰 반복되는 주기적인 펄스를 발생시켜 computer등에서 time 정보를 제공하는 역할

-

CPU에서 동작 클럭 등이 해당 device가 어떤 빠르기로 동작하는지를 나타내며 동작 클럭을 제공하는 것이 oscillator이다.

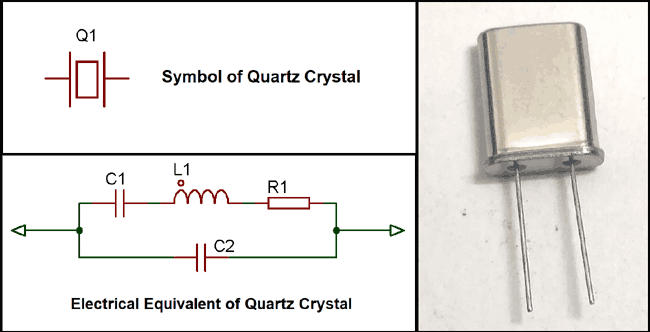

* 주로 piezoelectric effect를 이용하는 crystal로 만들어진다. 보다 저렴한 ceramic으로 만들어지는 경우도 있다.- crystal(주로 석영quartz가 사용된다)에 전기를 가할 경우 일정 시간 이후 crystal이 다시 전기를 만들어내는데 이 시간 간격이 매우 정확하다.

- 이를 바탕으로 clock signal을 발생시키는 oscillator가 만들어진다.

clock

- computer나 circuit의 동작 pace를 가르키며 단위는 보통 Hz로 표기되고 초당 몇 번의 pulse signal이 반복되었는지로 빠르기를 나타낸다.

- computer나 circuit을 구성하고 있는 여러 device들은 propagation delay 등의 특성이 다들 다르기 때문에 clock에 맞춰서 정상적인 동작이 이루어지도록 동기화되는 경우가 대부분이다. 비동기 방식은 없는 건 아니지만 매우 제어가 어렵다.

- 일반적으로 device들의 시간과 관련된 특성들은 동일 소자라도 온도나 제조 공정에서의 차이 등으로 인한 variation이 다양해 통계적인 측정치로 표시되며 일정 range에서 정상동작이 보장되는 특징을 가진다.

더 살펴보기

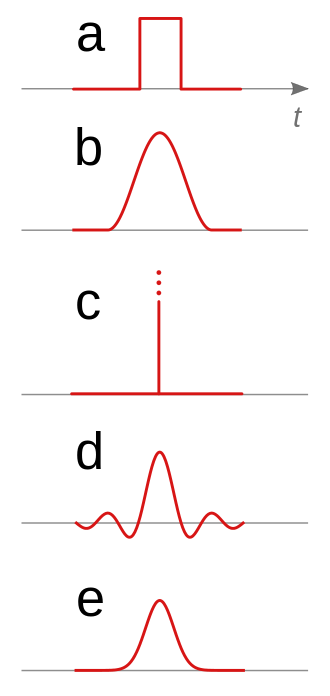

- pulse signal은 신호처리나 디지털 회로 등에서 자주 보게 되는 signal 중 하나이다.

- 여러 종류가 있으나 일반적으로 rectangular pulse를 주로 가르키며 구형파라고도 불린다.

- 다음은 pulse의 예시이다.

latch

걸쇠라는 뜻으로 자물쇠의 의미를 가진다.

gate를 조합하여 1bit의 정보를 기억하는(걸어두는) 역할을 하는 회로를 뜻한다.

- 주로

S-R letch에 대한 이해를 통해 실제 1bit의 정보를 기억하는데 많이 사용되는flip-flop을 이해하는 과정으로 배우게 된다. 이 flip-flop은 CPU가 명령어와 데이터를 기억하는데 사용하는register로 확장하게 된다. - 1bit의 정보를 기억하는 flip-flop와의 대표적인 차이점은 다음과 같다.

- clock signal에 대해 high (or low) 레벨에서 기억이 이루어지는지 아니면 rising(or falling) edge에서 기억이 이루어지는지라고 할 수 있다.

letch는 주로 high 레벨에서 기억이 이루어지며 flip-flop는 주로 rising edge에서 기억이 이루어지는 버전이 많이 사용된다.

OR latch

-

feedback 연결과

ORgate를 이용하여 1bit의 정보를 기억한다는 점에서 가장 간단한 latch이다.하지만 기억만 가능(정확히는 set)할 뿐 다시 reset할 방법이 없다.

-

교과서에서만 주로 다루는 latch이다.

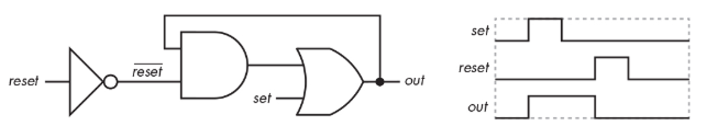

AND-OR Latch

-

ORlatch의 feedback connection을OR에 직접 연결하지 않고OR앞에 연결된AND에 연결하는 동시에 해당 AND에 을 (reset입력을inverter에 연결)을 입력시켜 reset 기능을 추가한 latch

-

ORlatch에서 reset이 되지 않는 단점을 보완한 것으로 정보의 기억 및 기억된 정보의 출력, 기억될 정보의 수정이 가능한 가장 간단한 memory이다. -

symmetric structure가 아니기 때문에 gate 간의 propagation delay에 취약하다.

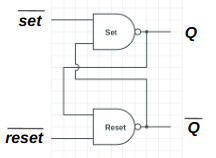

S-R latch

AND-ORlatch를NAND와NOR로 구현하여 symmetric structure를 가지도록 구현한 것이며 이름의S와R은 set과 reset을 줄인 말이다.

- 위 그림은

NAND로 구현되어 있으나NOR로 만들 수 있다. - 흔히 latch라고 하면

S-Rlatch를 가르킨다.

초기값 관련한 문제가 디지털 회로에서 자주 제기되며 과

이 동시에 activation되는 경우는 사용하지 않는다.

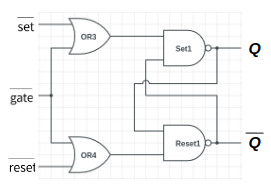

Gated S-R latch

- clock signal을 입력받아 특정 시점의 정보를 기억하도록

S-R latch를 확장한 것이며 개념적인S-R latch가 아닌 실제 회로 등에서 얘기하는Latch는 (특히 synchronous circuit) 이 Gated S-R latch를 가르키는 경우가 많다.

- S-R latch의 과 의 입력단 각각의 앞에

OR을 붙이고 각OR에서 과 의 입력을 받고 동시에 각OR은 clock이 입력될 동일 입력을 받는 구조이다. - 위 구조에서 과 의 입력을 분리하여 받고 있으나 이 둘은 동시에 1이 될 수 없는 입력이다.

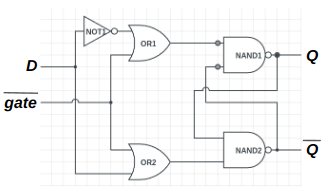

D latch

- Gated S-R latch에서 입력이 동시에 1이 될 수 없는 입력을 한 쪽에는 그대로 한 쪽에는 inverter를 거쳐 입력하는 구조로 만드는 게 보다 낫다.

- 이 경우 입력을 D라고 하면 이 latch는 해당 D의 1bit 정보를 에 따라 지정된 시간만큼 기억하는 memory로 동작하게 된다.

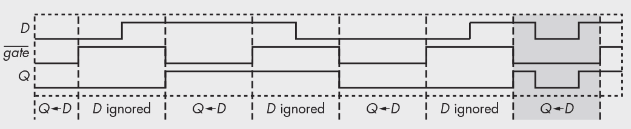

- 가 active인 경우 ()에 D의 signal이 그대로 출력 Q에 전달된다. 즉, 가 active인 상태에서 D의 상태가 변한다면 해당 변화가 그대로 출력 Q에 전달된다.

Memory는 일정 기간 동안 입력을 받기보다 한 순간의 값을 기억하는 게 유리한 경우가 많다.

- 일정 기간 동안 입력값이 변할 경우 어느 값이 기억될지가 알기 어려운 경우가 많다.

- 가 active인 기간 동안 D의 값이 0과 1 사이를 왔다갔다하는 경우를 생각해볼 것

- 이 때문에 Latch보다는 flip-flop이 보다 많이 이용된다.

Flip-Flops

특정 시점의 1bit 정보를 기억하는 memory device

latch는 high level에서 기억이 이루어지지만 flip-flop에서는 edge(=transition between logic level)로 결정된다.

latch가 특정 level인 경우 입력을 받아들이므로 해당 level 기간동안 입력이 변경될 수 있다.edge는 훨씬 짧은 시간동안 입력을 받아들이므로 해당 시간에 입력이 변경될 확률이 latch에 비해 매우 낮다.(flip-flop은 Edge triggered latch라고도 불린다.)

flip-flop들을 묶어서 여러 bit를 기억하게 확장한 형태의 register 또는 clock의 rising edge(or positive edge)의 수를 세는 counter로 확장이 된다.

흔히 4가지의 Flip-Flop이 다루어지지만 여기선 가장 널리 사용되는 D flip-flop만을 살펴본다.

- SR flip-flop

- D flip-flop

- JK flip- flop(Delay flop-flop): 가장 간단(S-R latch 3개를 묶어 구현)

- T flip flop

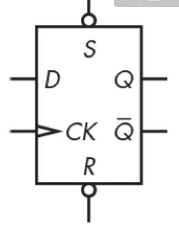

D flip-flop

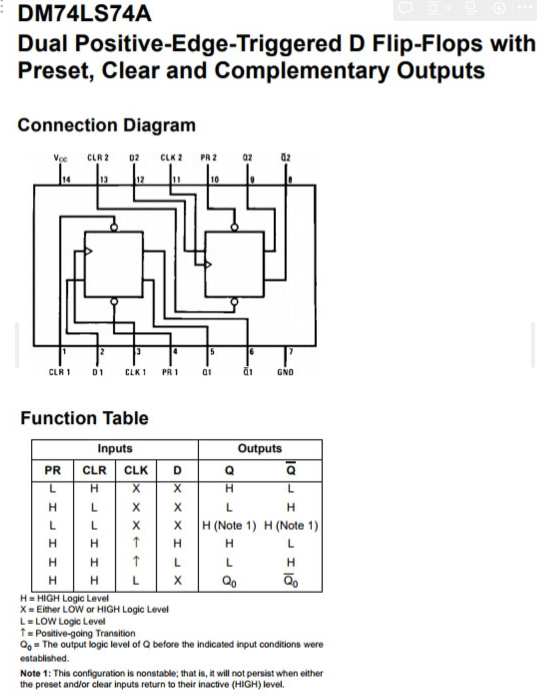

schematic diagram (7474 or DM74LS74)

- : input

- : output

- : set, bubble이 있으므로 active low인

- : reset, bubble이 있으므로 active low인

- ck: Clock Pulse, 삼각형 표시가 rising edge triggered 임을 표시

데이터 시트를 이용한 flip-flop의 동작 파악

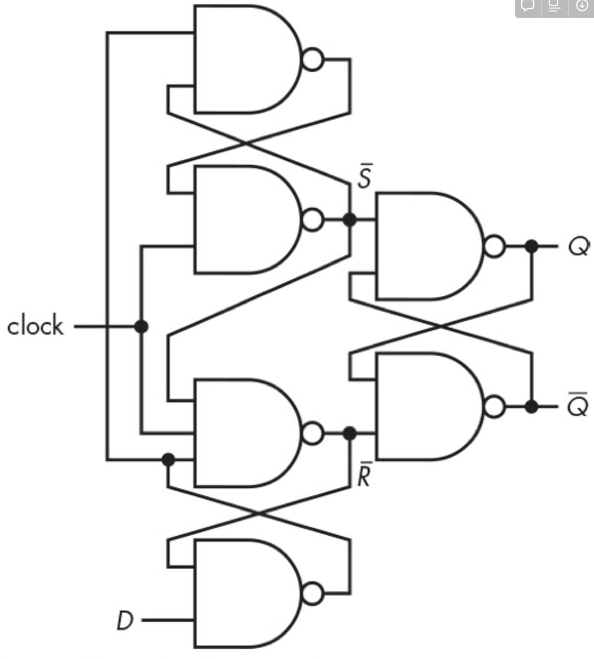

Gate D flip-flop의 구조

Gate로 D Flip-Flop의 구조를 보면 다음과 같다. (S-R latch 3개를 이용함)

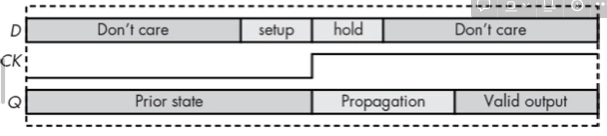

Setup and Hold times

- flip-flop처럼 edge에서 입력이 이루어지는 경우, ideal한 경우 순간의 값이 저장되나 practice인 경우 입력을 위해 앞뒤로 시간이 필요하다. 이를

Setup Time과Hold Time이라고 부르며 각각의 의미는 다음과 같다.

Setup Time

- 정상적으로 입력이 이루어지기 위해 입력 signal을 받아들이는 clock edge가 발생하기 전에 inpit signal이 유지되어야 하는 시간

- 으로 표기됨

Hold Time

- 정상적으로 입력이 이루어지기 위해 입력 signal을 받아들이는 clock edge가 발생한 후에 input signal이 유지되어야 하는 시간

- 로 표기된다.

이들과 Propagation Delay를 반영한 Timing Diagram은 다음과 같다.

- Latch보다는 입력을 받아들이는 시간이 짧지만 위의 timing diagram에서 보이듯이 입력이 출력으로 반영되기 위한 일정 시간들이 필요함

counter

register와 함께 flip-flop의 대표적인 응용사례이다.

가장 간단한 정의는 다음과 같다.

- 일정한 순서로

state가 반복하여 변화하는 일종의Register이다. Oscillator의 clock pulse를 입력받아 Difital System(computer 포함)에서 Time에 대한 정보를 주는 소자이다.

흔히 Counter의 풀력은 Counter의 state가 된다. oscillator의 pulse train의 주기에 정수배한 주기신호들을 만들어낼 수 있으며 Asynchoronous counter와 Synchoronus counter로 나뉘는데 Synchoronus counter가 사용하기 쉽기 때문에 많이 사용된다.

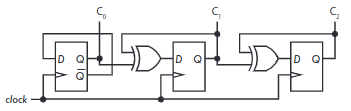

Asynchronous (Ripple) Counter

- signal이 clock pulse 부분에 들어가면서 signal이 0에서 1로 변할 때마다 그 count를 세어서 에 출력했다.

- signal은 보통 oscillator로부터 오게 되고 들은 각각 앞의 입력에 비해 2배 더 긴 주기의 신호를 생성해낸다.

D flip-flop의 input 에 가 연결되어 있기 때문에 1로 올라가고 나선 다시 0으로 떨어지게 되며 이를 에 들어오는 signal에 맞춰 반복한다.

ripple counter라는 별칭을 가지고 있는데 구성하고 있는 D flip-flop의 출력이 왼쪽에서 오른쪽으로 전달되는 것이 마치 물결이 퍼져나가는 것과 비슷하다는 점에서 유래되었다. 이 별칭에서도 알 수 있듯이 flip-flop에서의 출력이 동시에 이루어지는 게 아닌 출력이 앞에서 뒤로 이어지는 경우이다. 따라서 propagation delay에 취약할 수밖에 없다. 실제로 clock signal이 빠르게 변할 경우 정상적인 동작이 이루어지지 못한다.

Synchoronous Counter

Synchoronous란 clock을 공유한다는 뜻으로 HW나 SW나 동기식이 훨씬 제어가 쉽다. 단 일정부분 느려지는 trade-off가 있다.

다음은 Synchoronous counter로서 를 공유하여 모든 flip-flip들이 정확히 같은 시간에 값이 변화하게 된다.

- 출력이 valid하기까지 요구되는 setup 및 hold time, propagation delay 영향은 있으나 각 flip-flop들이 동일한 clock에 맞춰 동작한다.

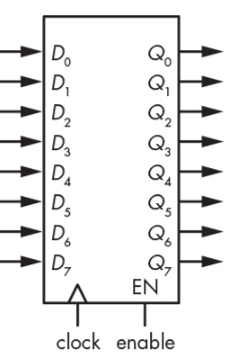

register

1bit를 기억할 슈 있는 flip-flop들을 여러 개를 묶어서 여러 bit를 기억하도록 만들어진 device로 CPU 내부에 위치하며 ALU 등이 직접 접근하여 사용되는 memory가 바로 Register이다.

가장 빠르고 비싼 memory라고 할 수 있다.

- Register를 여러 개 사용하면 보다 많은 bit를 저장할 수 있다.

- e.g. 8개의

D flip-flop들을 묶어서 사용하면 8bit register가 가능하다. - 하지만 보다 많은 여러 bit를 기억하기 위해서 각각의 값들이 어느 register에 저장되는지를 나타내는 address가 필요하며 이를 위해

decoder와selector가 연결된memorydevice가 등장한다.

schematic representation

clock: rising edge에 입력D의 값이Q에서 출력enable: 해당 입력이 active여야 register가 동작한다. 여기선 1이어야 한다.

reference

1. wikipedia pulse

2.mk docs