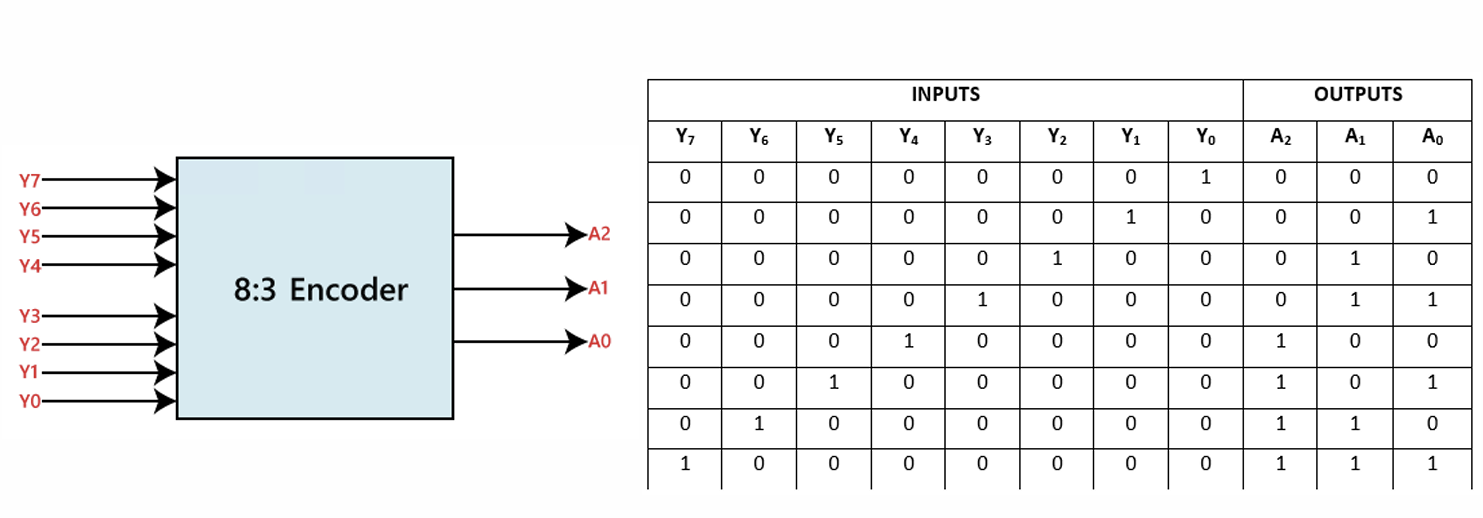

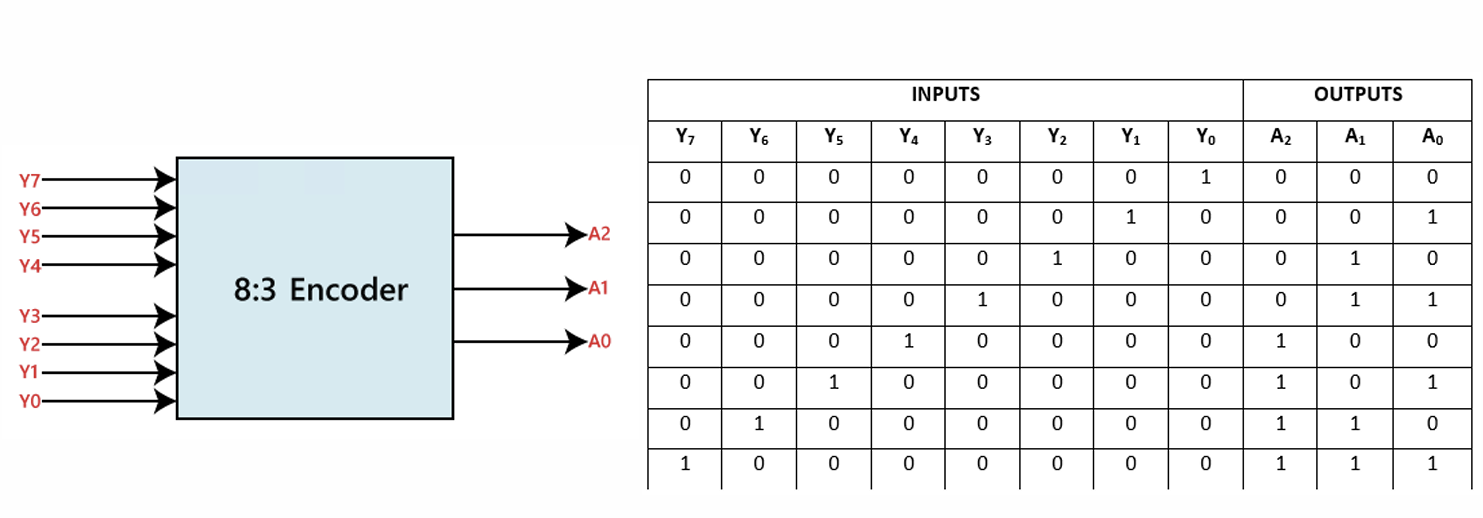

Encoder explanation

- Encoder with input 8 output3

- 8개의 입력선 중 한 개의 input 만 1 나머지 0

- 1이 있는 위치를 output 으로 출력

8to3 Encoder verliog source code

`timescale 1ns / 1ps

module encoder_8to3(

input [ 7: 0] in,

output reg [ 2: 0] out

);

always @ (*)

begin

case(in)

8'h01 :out =3'd0;

8'h02 :out =3'd1;

8'h04 :out =3'd2;

8'h08 :out =3'd3;

8'h10 :out =3'd4;

8'h20 :out =3'd5;

8'h40 :out =3'd6;

8'h80 :out =3'd7;

default: out = 3'bxxx;

endcase

end

endmodule

8to3 Encoder verliog testbench code

`timescale 1ns / 1ps

module encoder_8to3_tb;

reg [7:0] in;

wire [2:0] out;

// DUT (Device Under Test) 인스턴스

encoder_8to3 uut (

.in(in),

.out(out)

);

initial begin

$display("8-to-3 Encoder Test");

$display("----------------------------");

$display("Input | Output");

$display("----------------------------");

// 1-hot 입력을 하나씩 테스트

in = 8'h01; #10; $display("%08b | %03b", in, out);

in = 8'h02; #10; $display("%08b | %03b", in, out);

in = 8'h04; #10; $display("%08b | %03b", in, out);

in = 8'h08; #10; $display("%08b | %03b", in, out);

in = 8'h10; #10; $display("%08b | %03b", in, out);

in = 8'h20; #10; $display("%08b | %03b", in, out);

in = 8'h40; #10; $display("%08b | %03b", in, out);

in = 8'h80; #10; $display("%08b | %03b", in, out);

// default 케이스 (여러 개 입력 or 0)

in = 8'h00; #10; $display("%08b | %03b (default)", in, out);

in = 8'h03; #10; $display("%08b | %03b (invalid)", in, out);

$finish;

end

endmodule

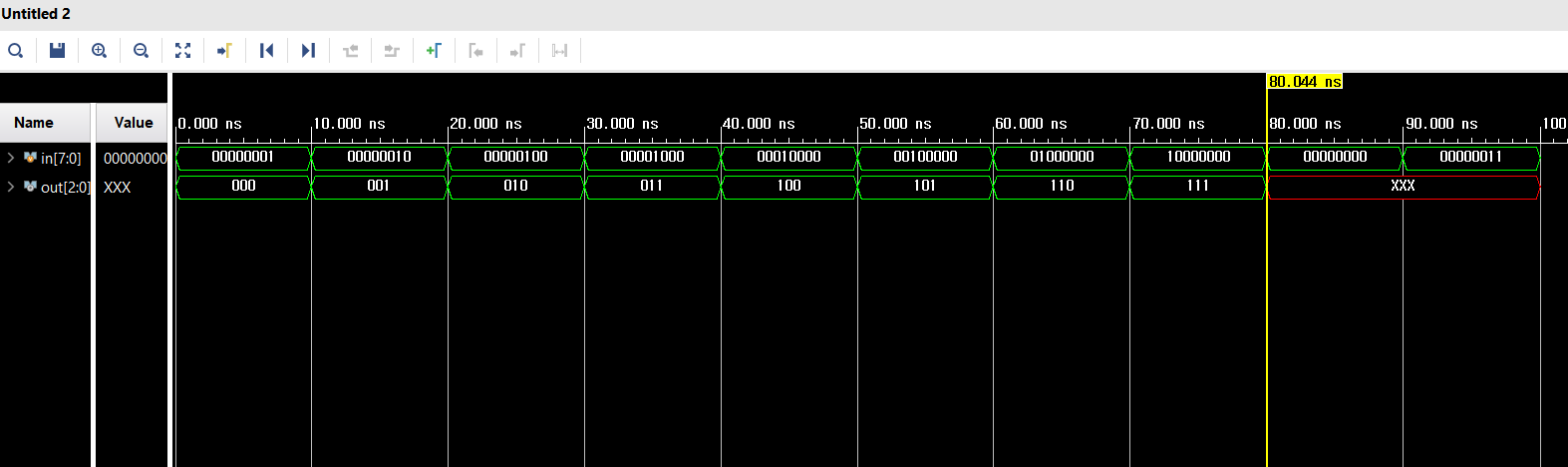

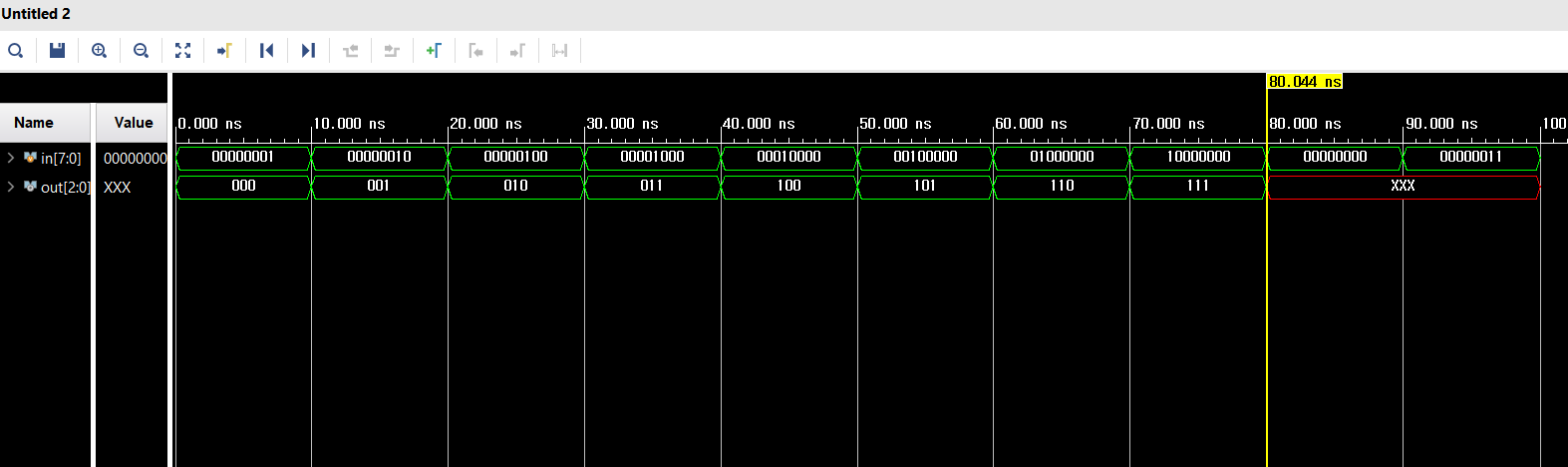

Simulation result

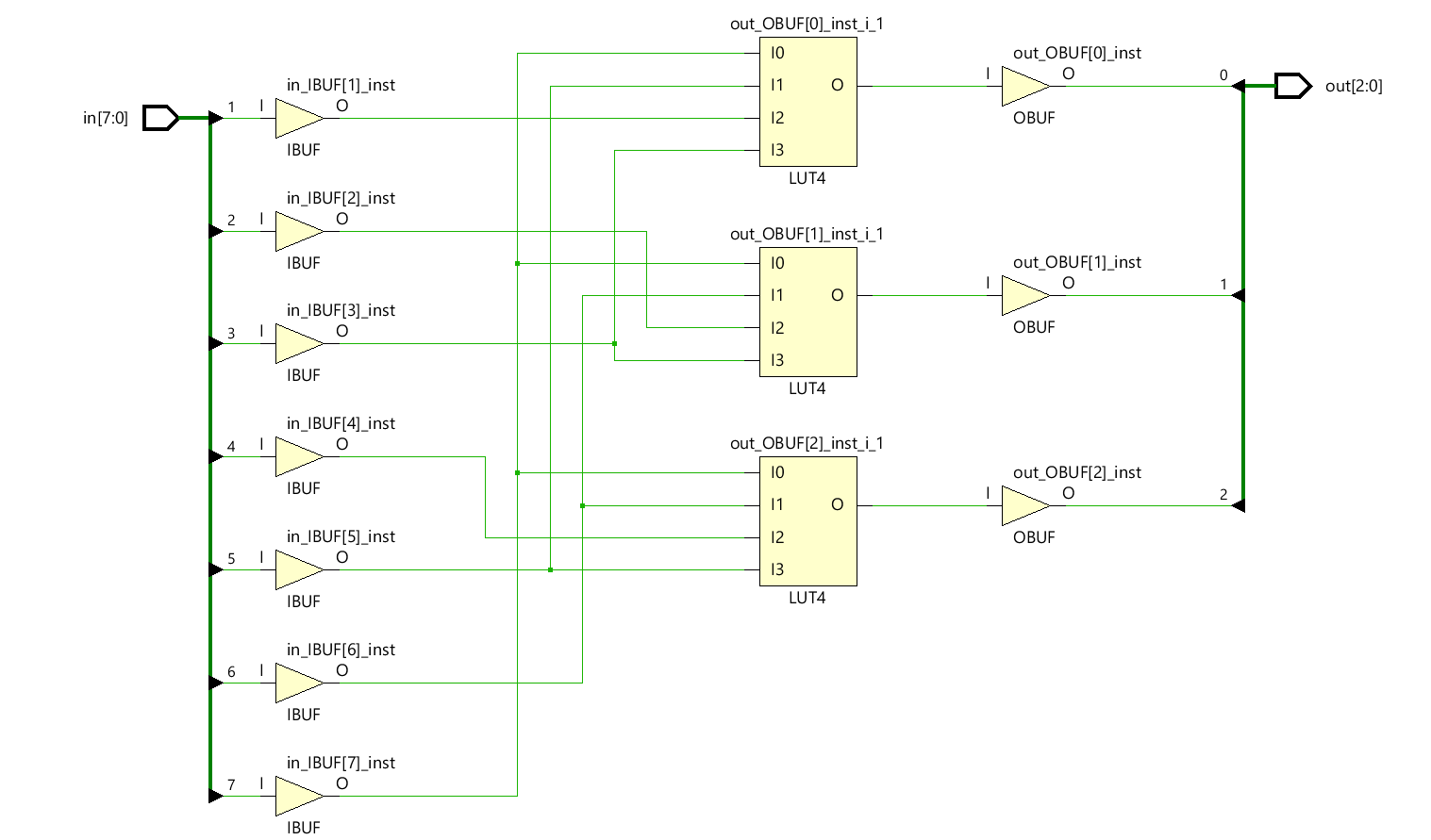

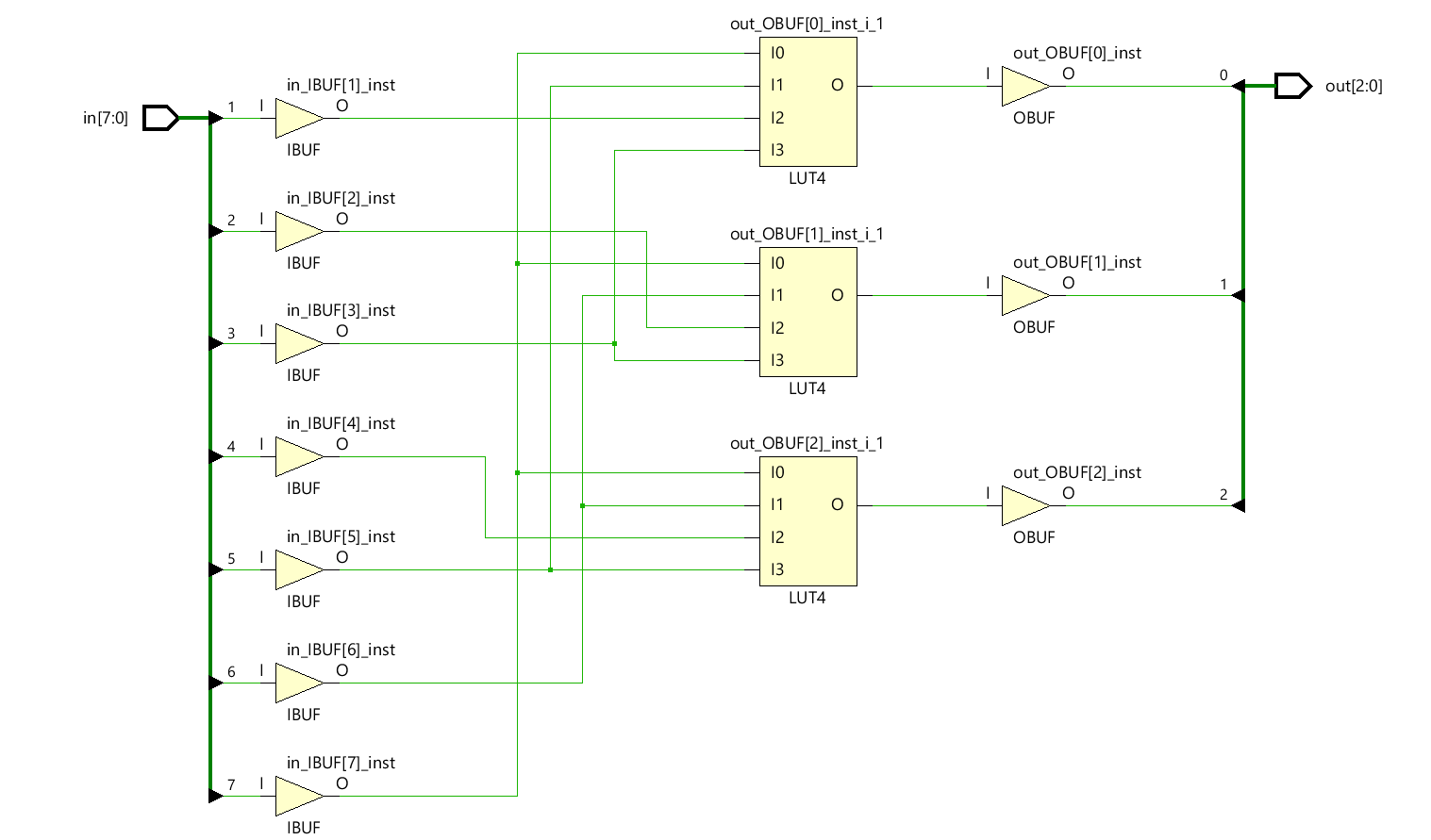

Schematic

출처

- System integrated Circuit design lab