13.1 Parity check

Parity bit

- n개의 비트에 더해져 전체 비트의 1의 갯수를 짝수/홀수가 되도록 한다.

Parity check

- 지금까지 주어진 입력에 대해 1의 갯수가 짝수였는지 홀수였는지를 알려준다.

- 1 Clock edge 마다 1개의 입력이 주어지고, 그에 상응하는 1개의 출력이 주어진다.

Odd parity check 의 구현

- 지금까지 들어온 1의 갯수가 홀수이면 1을 출력한다.

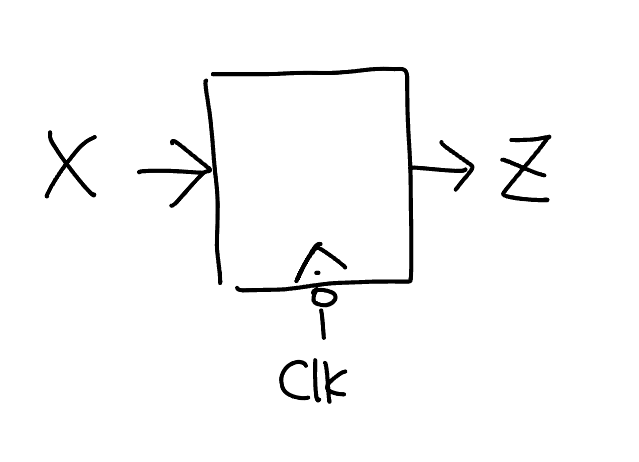

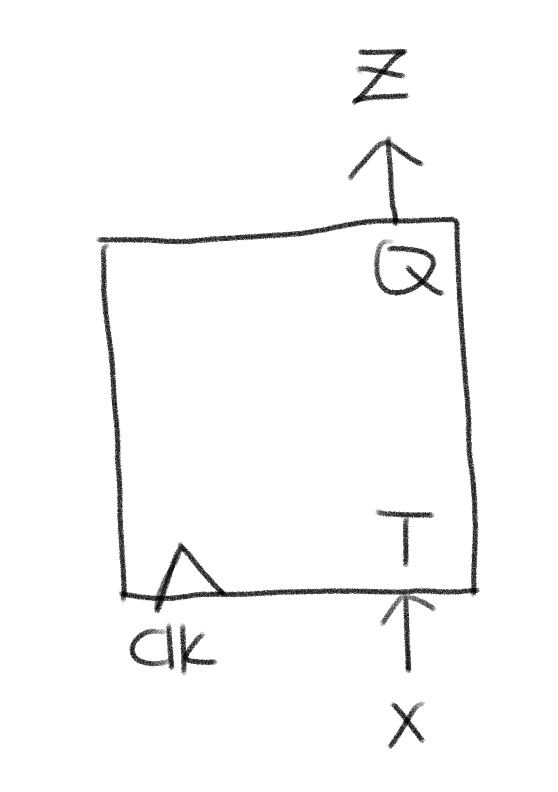

대략적인 형태

- X는 직렬 입력, Z는 입력에 상응하는 출력이다.

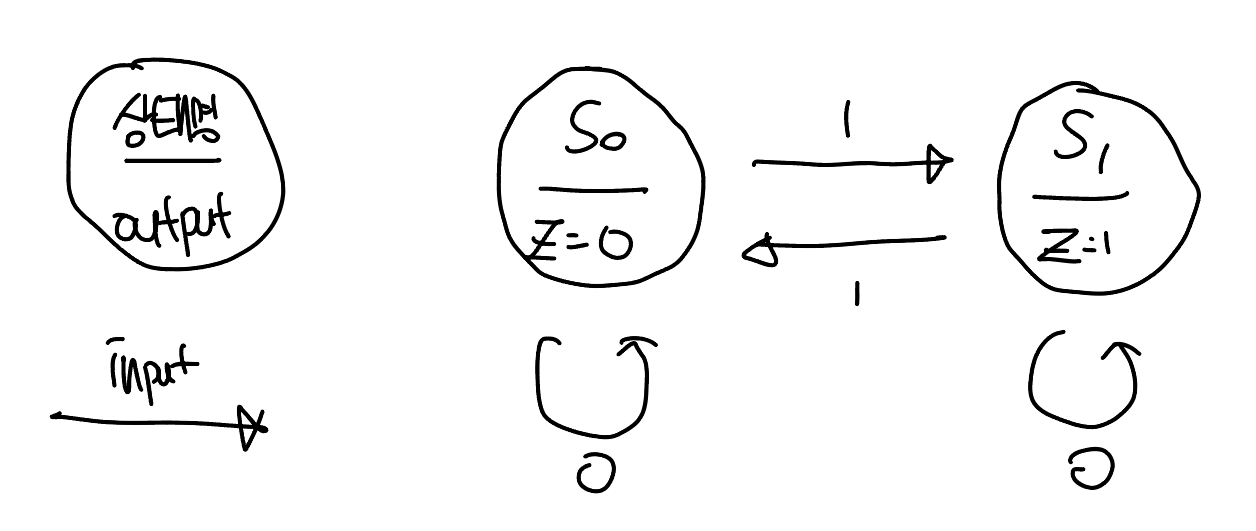

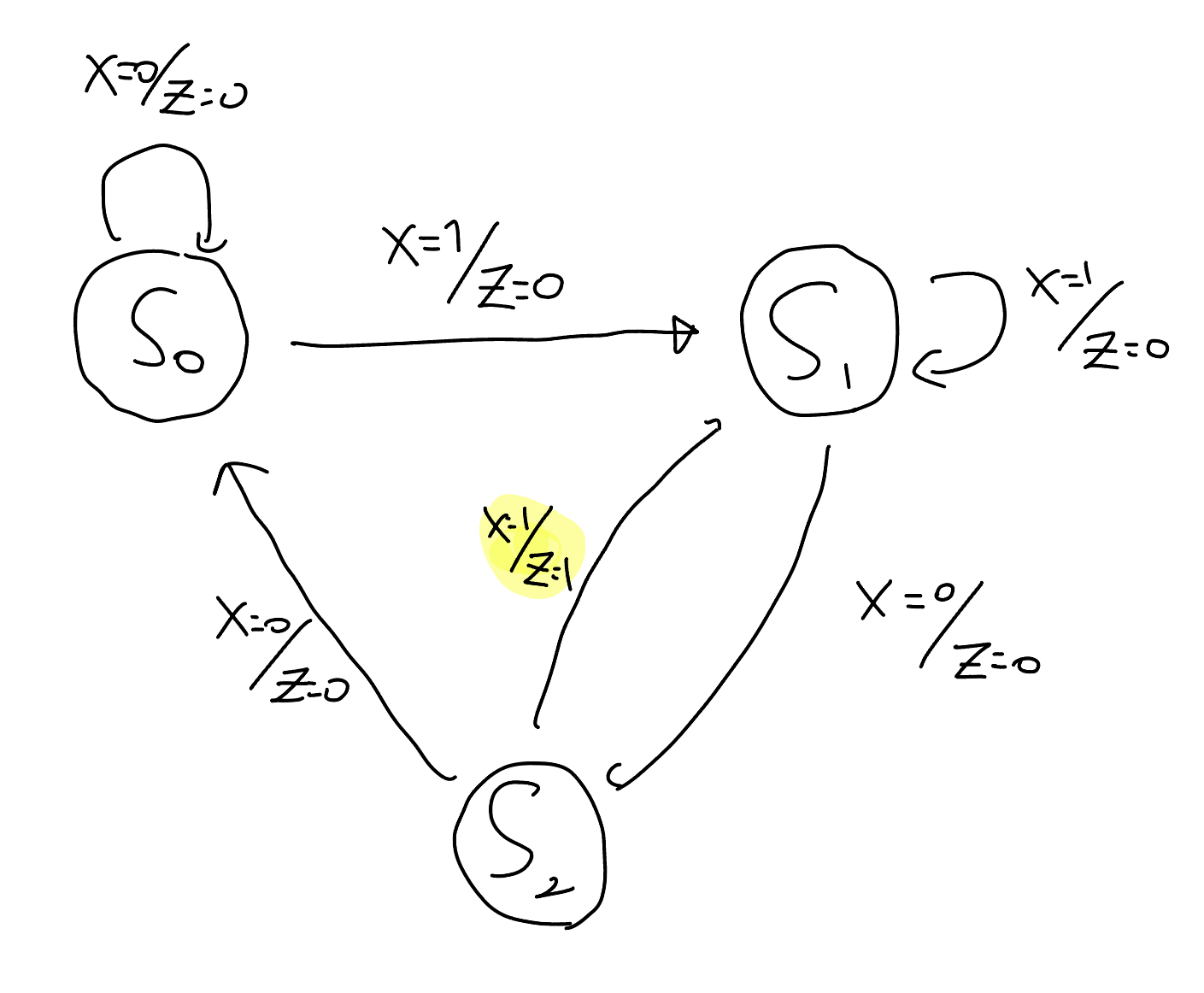

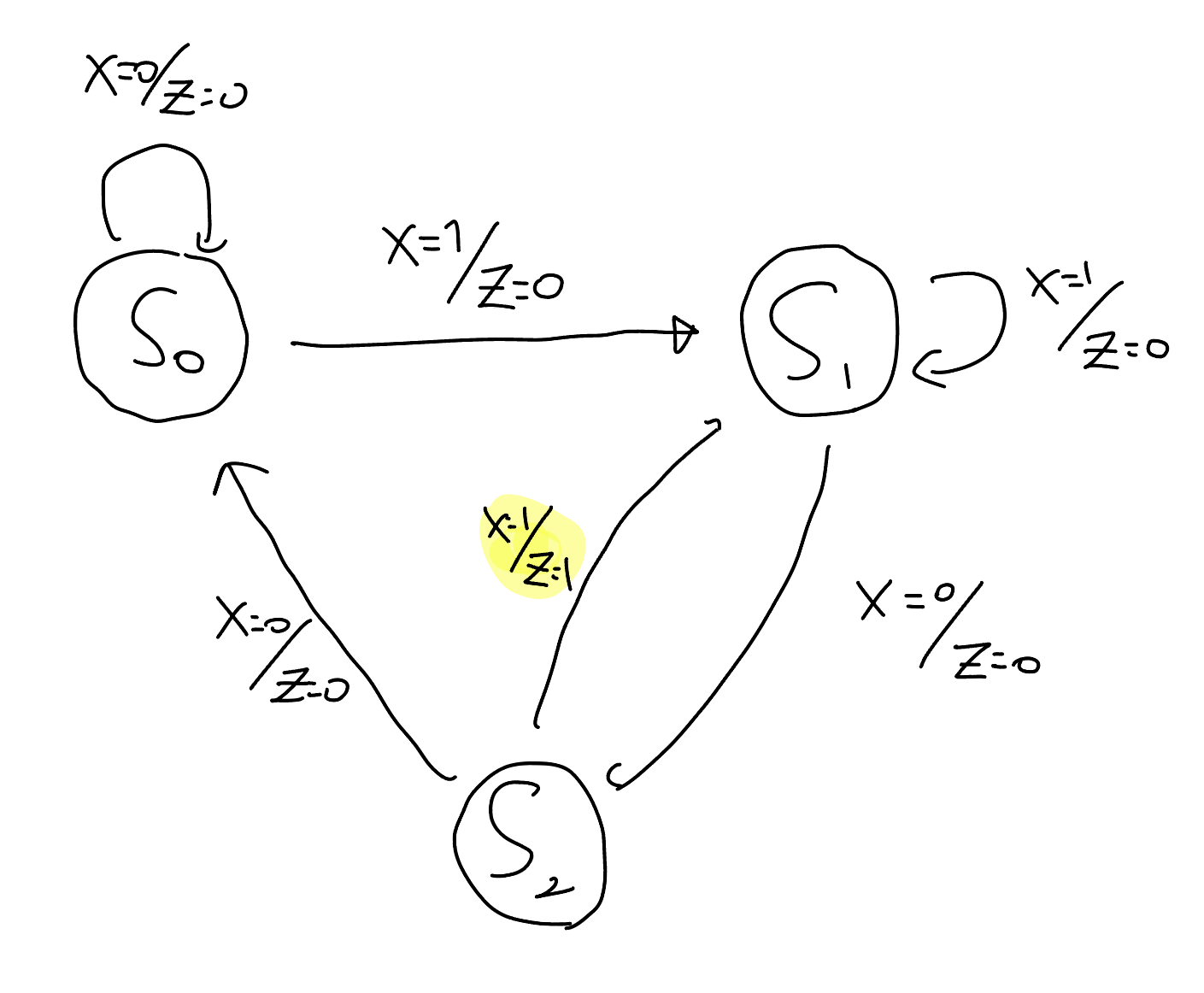

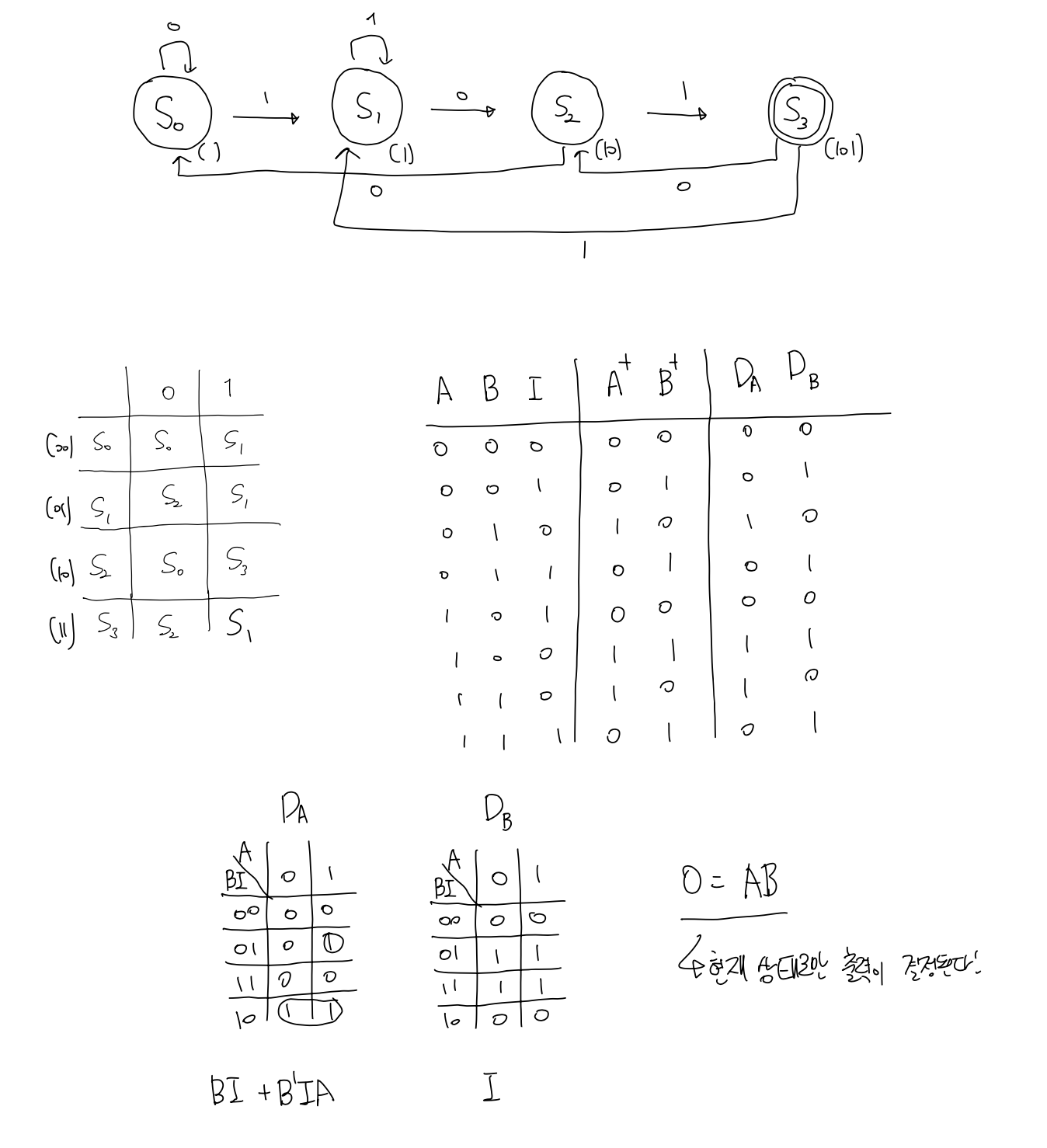

- 이를 State machine으로 표현시 아래와 같다.

- 각각의 State는 상태명과 상태에 따른 출력값이 적혀있다.

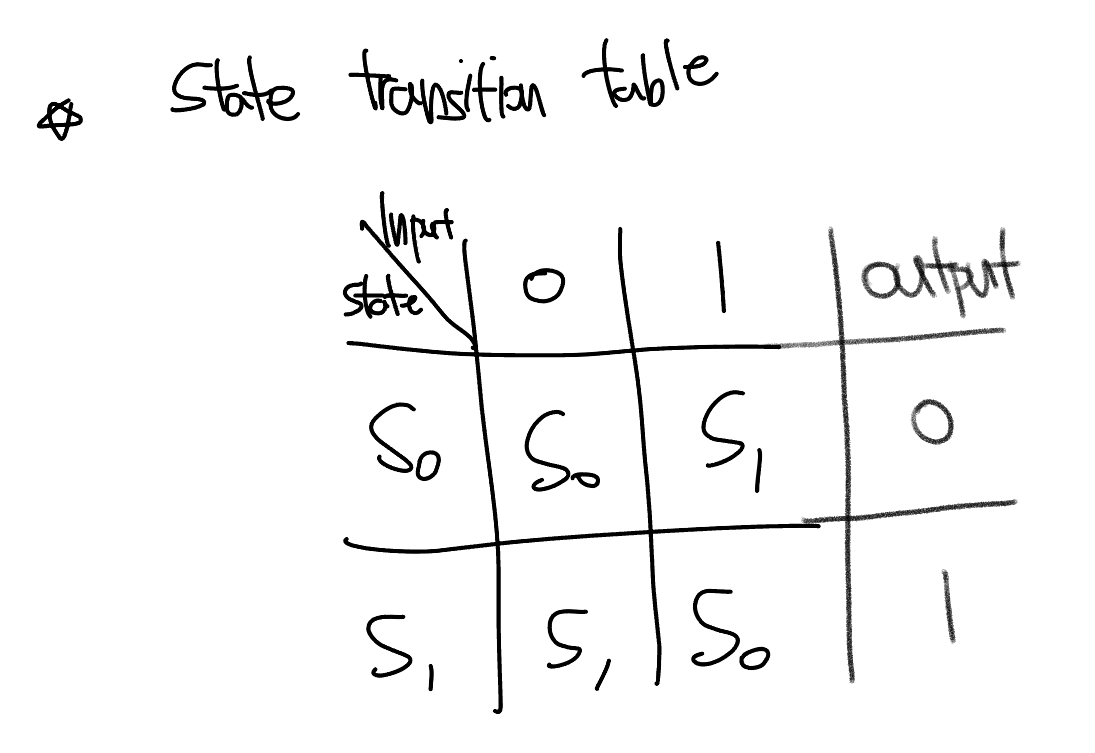

- 이를 트랜지션 테이블로 변환하면

- Row index는 State, Column index는 Input이 들어간다.

직접 구현

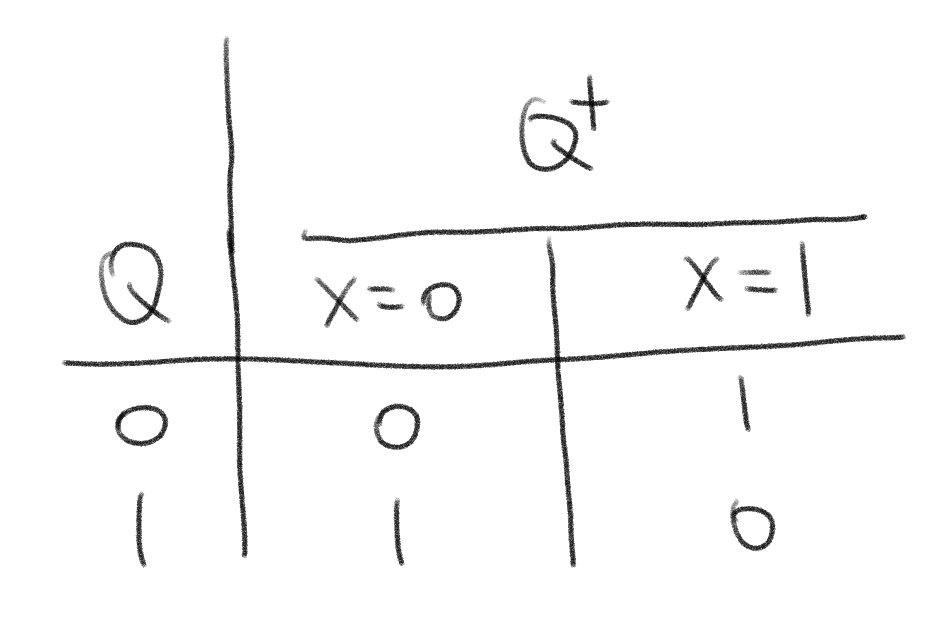

- 1개의 T - 플립플롭을 이용해 구현하는것

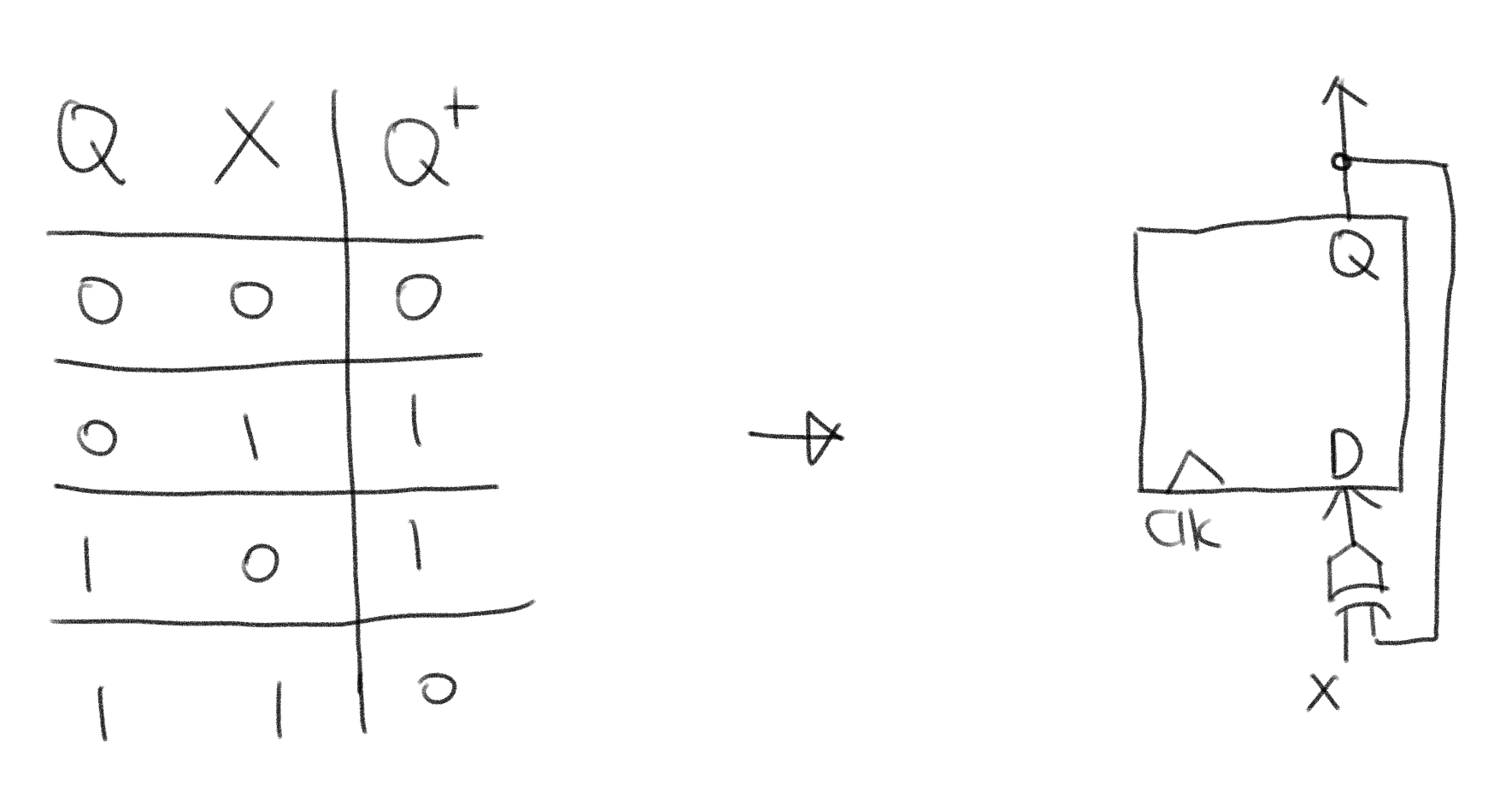

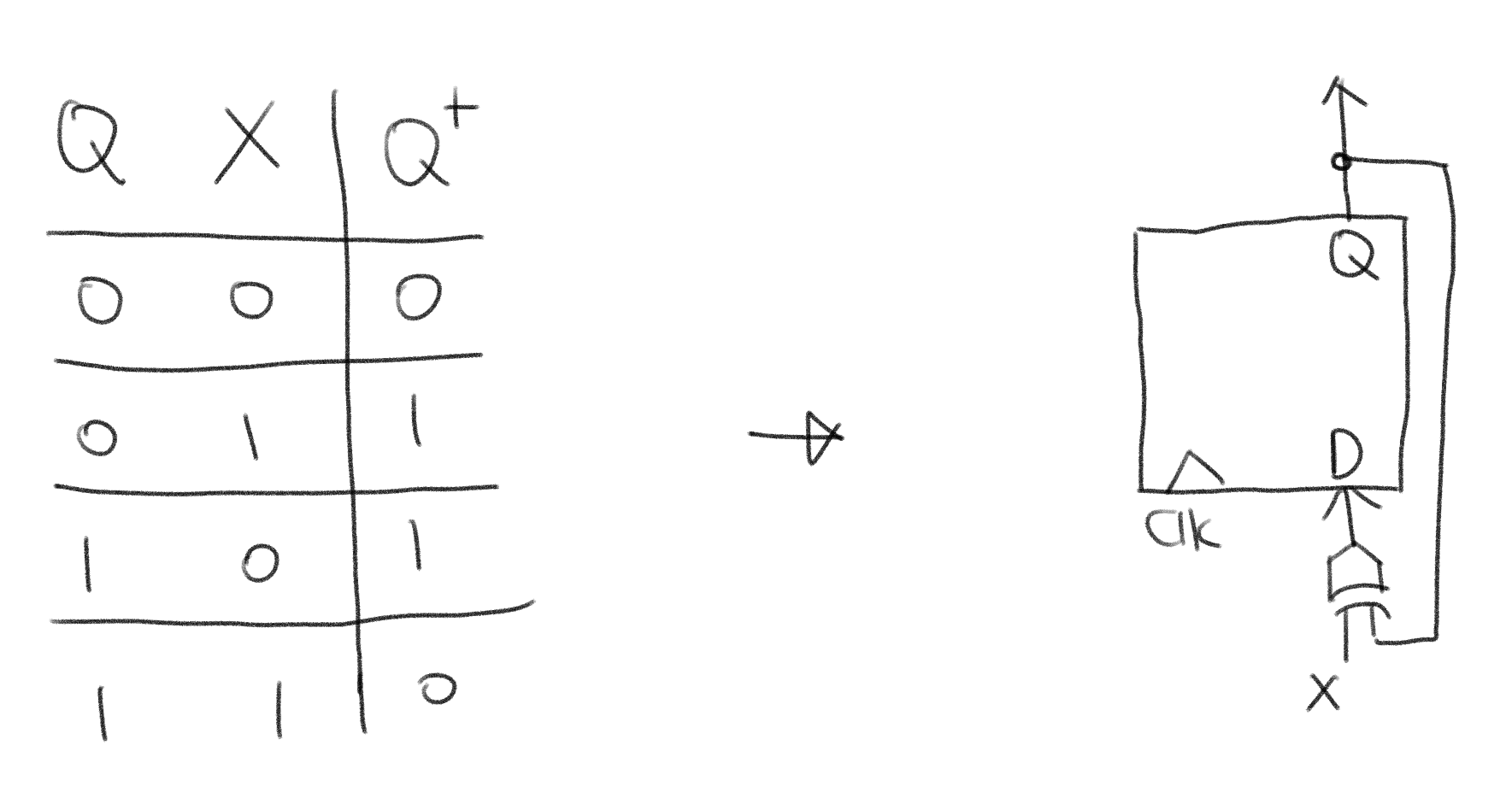

State table

실제 형태

- 입력과 현재 상태를 통해 Table을 만들어 카르노 맵으로 구현하는 과정을 통해 D 플립플롭도 사용 가능하다.

Clocked sequential circuit

Moore machine

- 출력이 플립플롭의 현재 상태로만 구성된다.

- 출력이 간단하다.

- State 만 다 그려도 출력을 구성할수 있다.

Mealy machine

- 출력이 플립플롭의 상태와 입력으로 구성된다.

- 상태의 갯수가 Moore machine 에 비해 적다.

위 두개가 할수있는 능력은 서로 같다.

Sequential detector

- "101" 이 순서대로 입력되면 1을 출력하는 회로

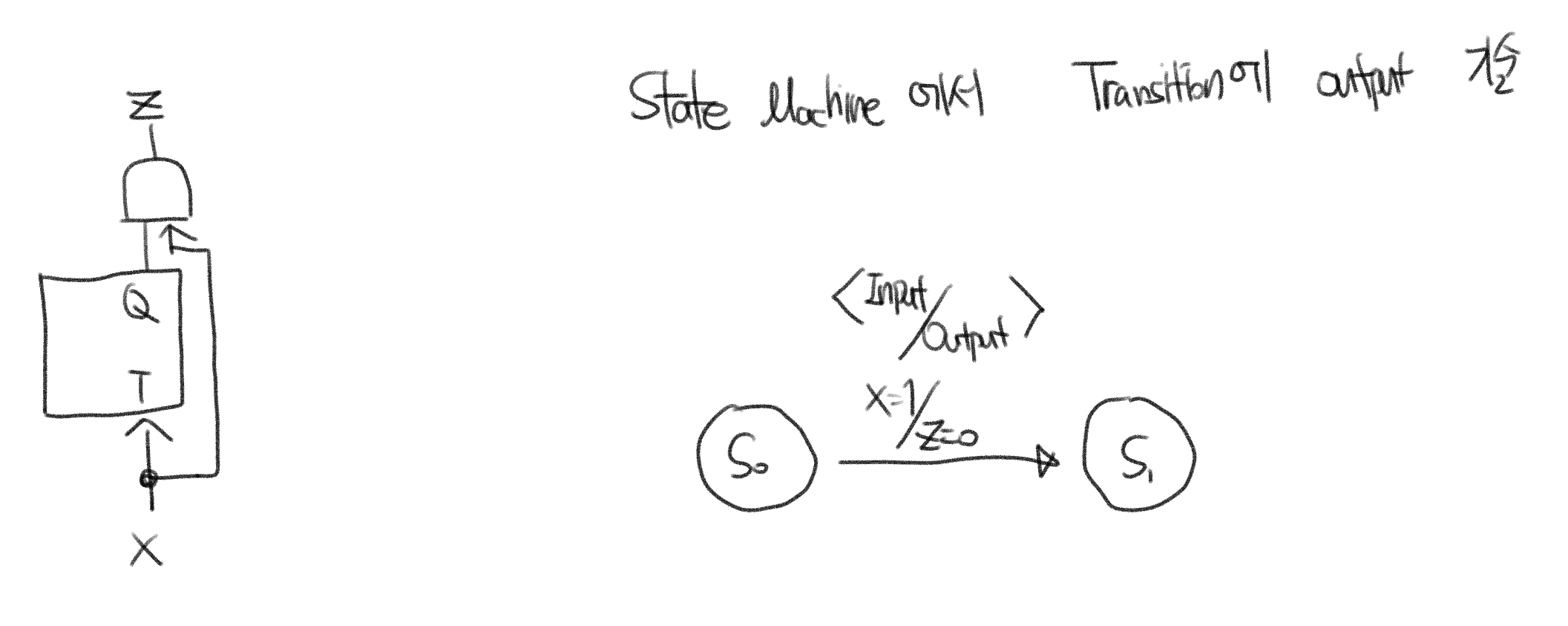

Mearly machine 을 이용한 구현법

- State machine을 구성한다.

- Transition diagram 을 구성한다.

- 하나의 플립플롭은 0과 1의 두 상태를 저장할수 있다.

- N개의 플립플롭은 개의 상태를 저장할수 있다.

- 즉 3개의 상태가 존재해 2개의 플립플롭을 사용한다.

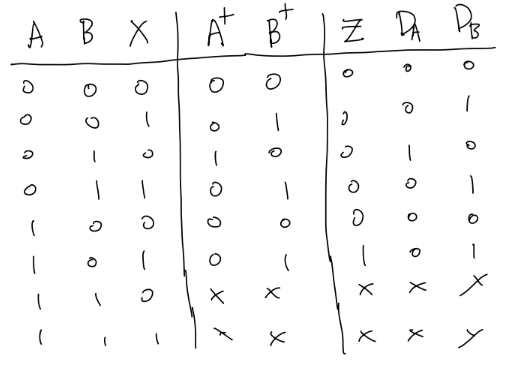

- 2개의 D 플립플롭을 사용한다고 가정하고 카르노맵을 구성하기 위해 준비한다.

- 입력은 1개 받고 사용할수 있는 플립플롭의 상태는 2개이다.

- 입력에 Z, 플립 플롭의 상태를 A, B 라고 둔다.

- 여기에서 플립 플롭의 상태와 Transition machine의 상태를 1:1 대응한다.

- 이를 통해 표를 작성한다

- 맨 왼쪽은 현재상태와 입력

- 중간은 현재상태 + 입력에 대한 다음 상태

- 맨 오른쪽은 그렇게 되기 위해 플립플롭에 직접 입력되는 값과 출력이다.

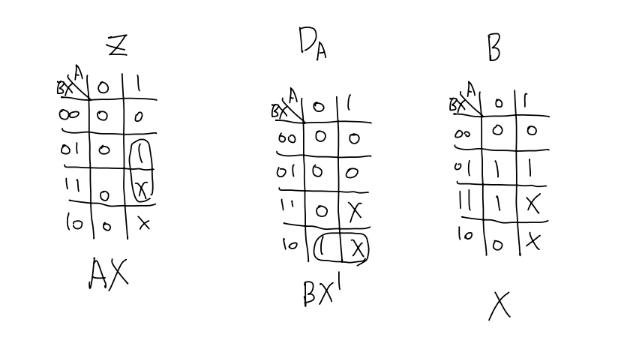

맨 오른쪽을 카르노맵을 통해 구한다.

Moore machine 을 이용한 구현

Mealy machine에서의 state 축약

- 0 혹은 1의 입력이 들어오든 출력이 0이라는 뜻