Von Neumann Machine

Stored-Program computer - Program과 Data가 동일한 형식으로 저장된다.

Processing unit이 오직 메모리하고만 소통할 수 있다.

Harvard Architecture

Processing unit이 Data Memory와 Instruction Memory 둘 다 소통이 된다.

Computer System에서 메모리에 잦은 접근은 성능을 저하시킨다.

또한 processor가 상대적으로 속도가 느린 Memory나 Storage에 접근하는 횟수를 최소화할 때 성능을 최대화 할 수 있다.

1. Mode Bit

Mode Bit은 PSW라 불리는 레지스터에 저장된다.

Mode Bit이 왜 필요한가 ?

사용자와 OS는 시스템 자원을 공유하기 때문에 사용자가 메모리 내의 OS영역에 침투해 시스템이 망가질 수 있다.

-> OS의 안전과 적절한 동작을 위한 보호장치

Mode bit 0 -> The System is in kernel mode

제어권이 OS에게 있고 OS code가 수행 (privileged mode)

Mode bit 1 -> The System is in user mode

제어권이 사용자에게 있고 user code가 수행

2. Timer

The main task of a timer is to interrupt the CPU after a specfic period of time (-> It is determined by hardware design)

Timer의 주요 업무는 시간의 특정 기간 후에 CPU를 멈추게하는 것

Timer를 사용하는 이유는 Time sharing 때문이다.

-> 사용자의 response time을 줄이기 위해 !

현재 CPU를 멈추고 다른 program을 동작시켜야함

Timer에 의해 시간이 제동된다.

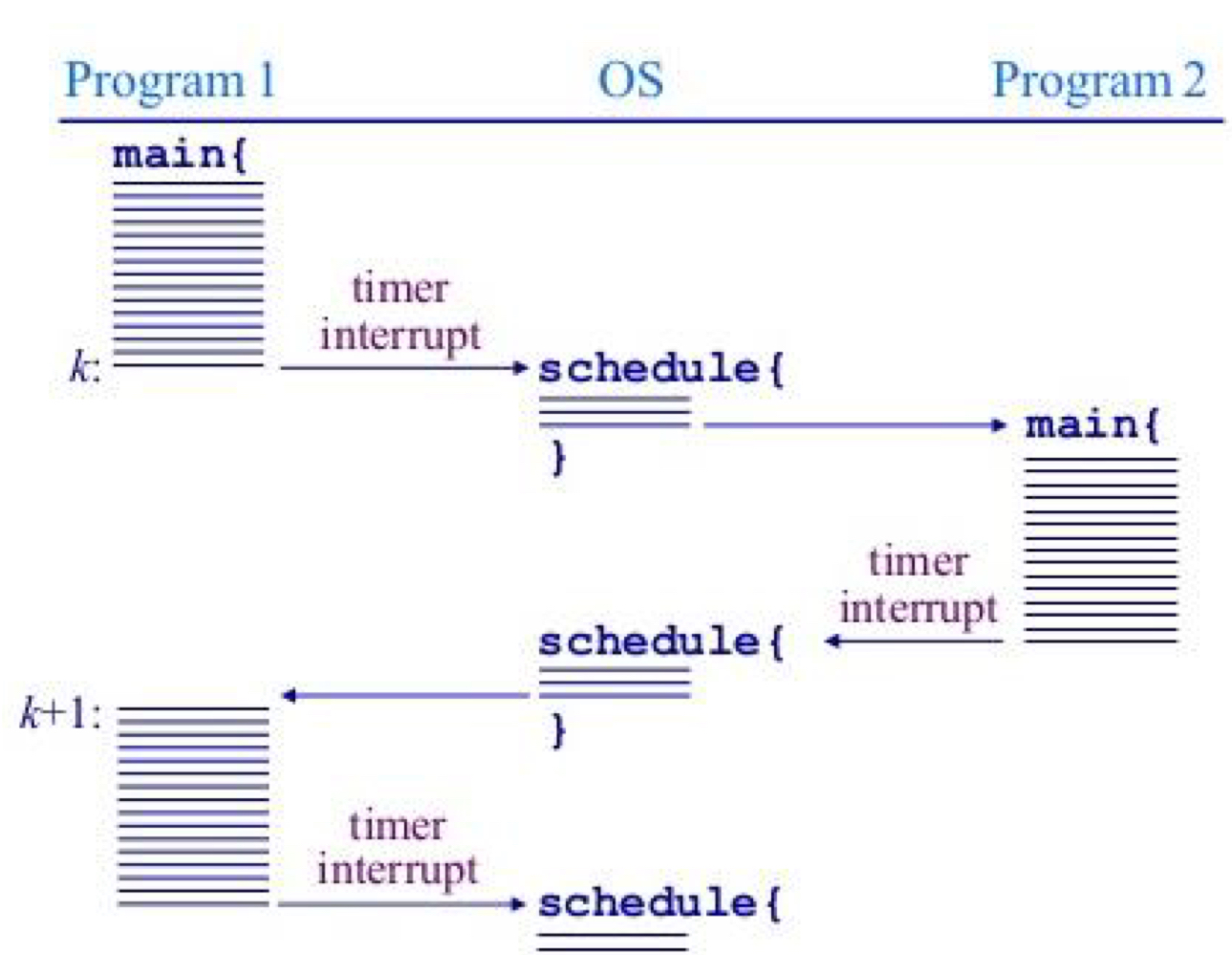

Program1 Program2는 Mode Bit이 1일 때 실행

OS는 Mode Bit이 0일 때 실행

timer interrupt는 Timer에 의해 stop

3. I/O Device

I/O Device는 키보드, 마우스 등 모든 입출력 장치를 말한다.

OS는 I/O Device가 무엇을 해야하는지 알려주며 Device driver는 I/O device를 관리하는 운영체제이다.

4. Exception (Interrupt)

- Transfer to OS

- Exception processing by exception handler

- return to I_current, I_next, abort

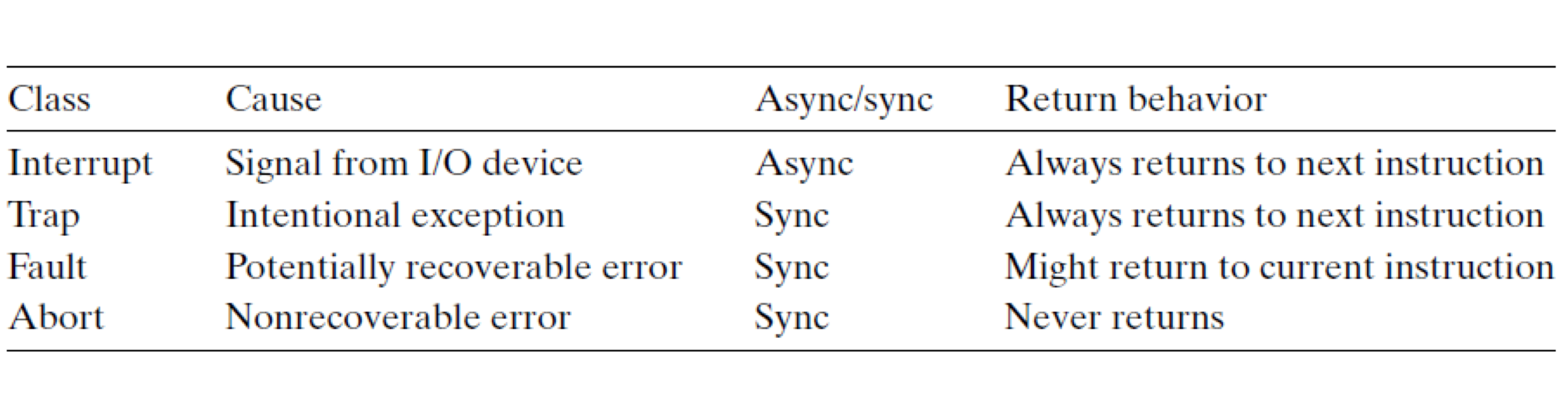

4-1 Asynchronous Exceptions

- Caused by events external to the processor (e.g., I/O devices)

외부 하드웨어가 발생시킨 문제- Unpredictable

program 입장에서는 예측할 수가 없다.- Handler returns to "next" instruction

입력이 다 되면 Next 명령어를 리턴해준다.

Examples:

Timer interrupt - Timer도 하드웨어

4-2 Synchronous Exceptions

- Caused by events that occur as a result of executing an instruction, and triggered by the CPU it self

CPU 자체가 exception 발생한 것으로 program 실행중에 발생한다.

즉, 실행하고 있는 명령어의 결과에 의해서 발생되는 이벤트

-

Traps

사용자에 의해 의도적으로 발생된 이벤트

EX) System calls, breakpoint traps 등 (예를 들면 scanf)

Next 명령어를 리턴해준다. -

Faults

사용자가 의도하진 않았지만 회복이 가능한 이벤트

EX) page faults (recoverable), protection faults (unrecoverable), floating point exceptions(divide by 0), invalid memory access

이 문제는 핸들러에 의해서 회복이 가능하다고 판단되면 다시 현재의 명령어로 돌아간다. -

Aborts

사용자가 의도하지도 않고 회복도 안 되는 이벤트

EX) illegal instruction parity error, machine check

복구할 수 없기 때문에 프로세스를 종료시킴으로 처리한다.

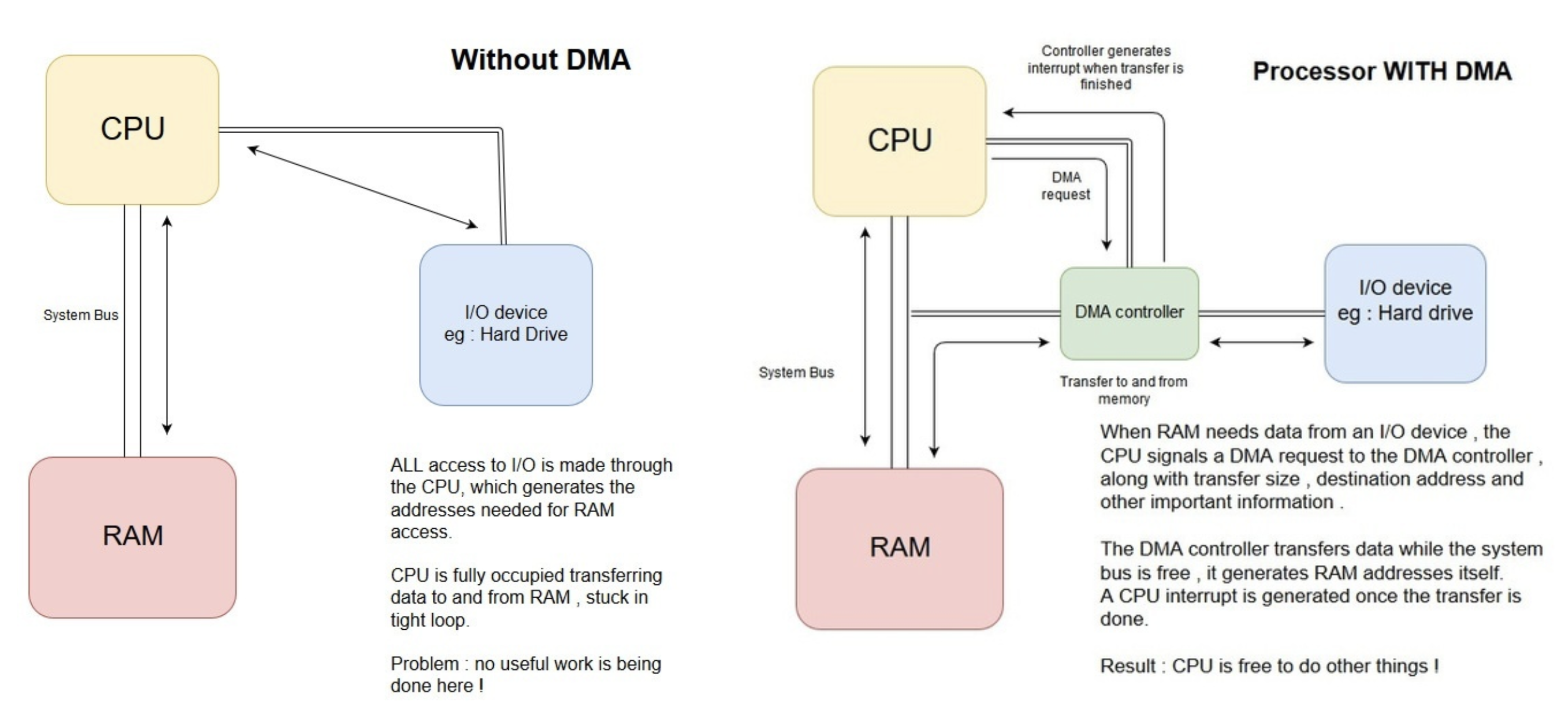

5. DMA (Direct Memory Access)

It allows the device to transfer data directly to/from memory without CPU involvement

하드웨어 장치(하디디스크, 그래픽 카드 등)들이 메모리에 직접 접근하여 읽거나 쓸 수 있도록 하는 기능

CPU의 개입없이 I/O 장치와 기억장치 사이의 데이터를 전송하는 접근 방식이다.

CPU가 해야할 주변 장치와의 데이터 전송을 DMA 장치가 해준다.

그 만큼 CPU의 효율을 늘릴 수 있다.

고속의 I/O 장치의 경우 Interrupt가 빈번하게 발생하는데 DMA를 사용하면 횟수를 줄일 수 있다.

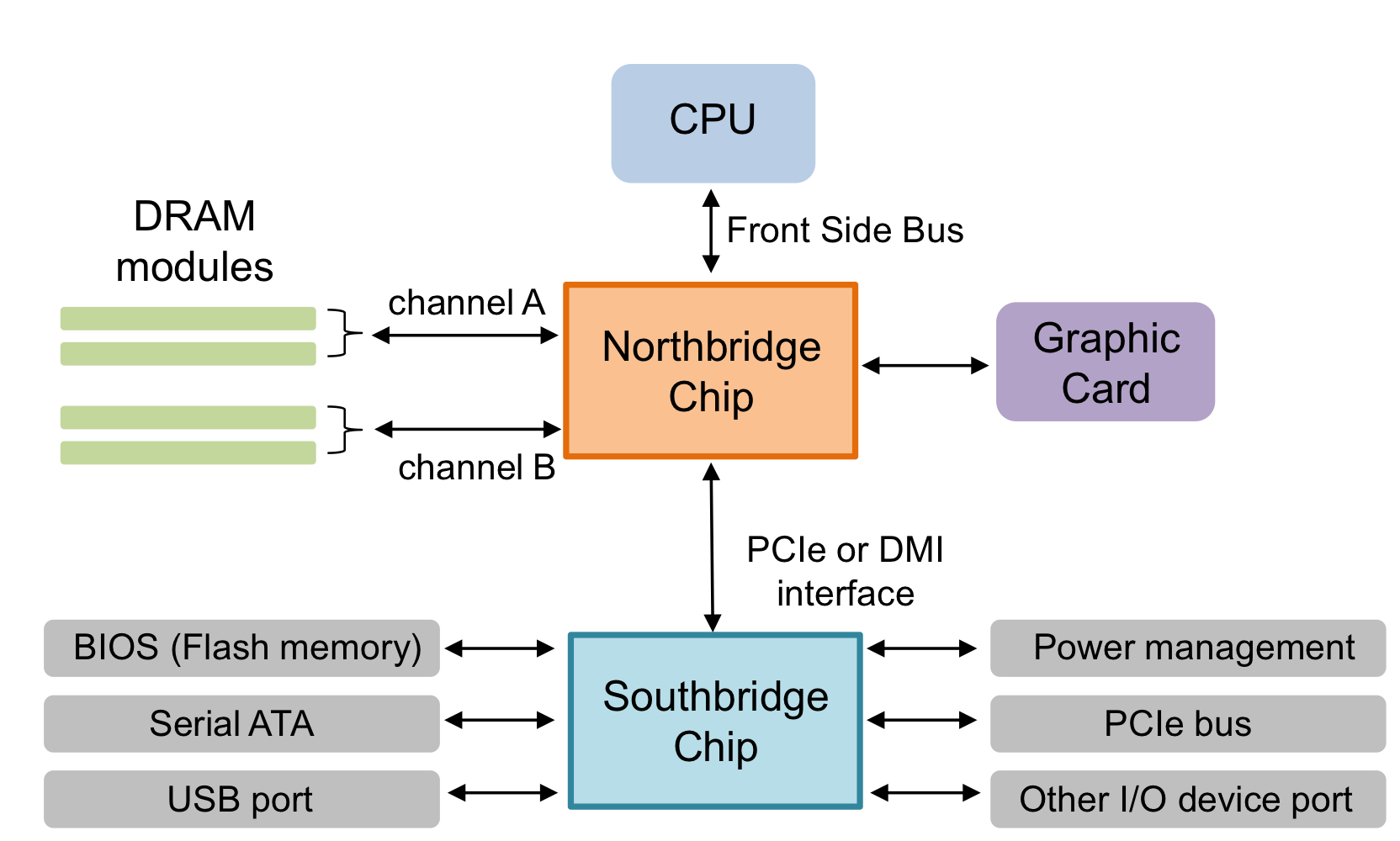

6. BUS

Northbridge(Memory Controller Hub or Graphic Memory Controller Hub) is one of the two chips in the core logic chipset on a PC motherboard

Southbridge (I/O Controller Hub) is the chip that controls all of the computers I/O functions

Northbridge Chip - 빠르다.

Southbridge Chip - 느리다.