1. 페이징 Paging

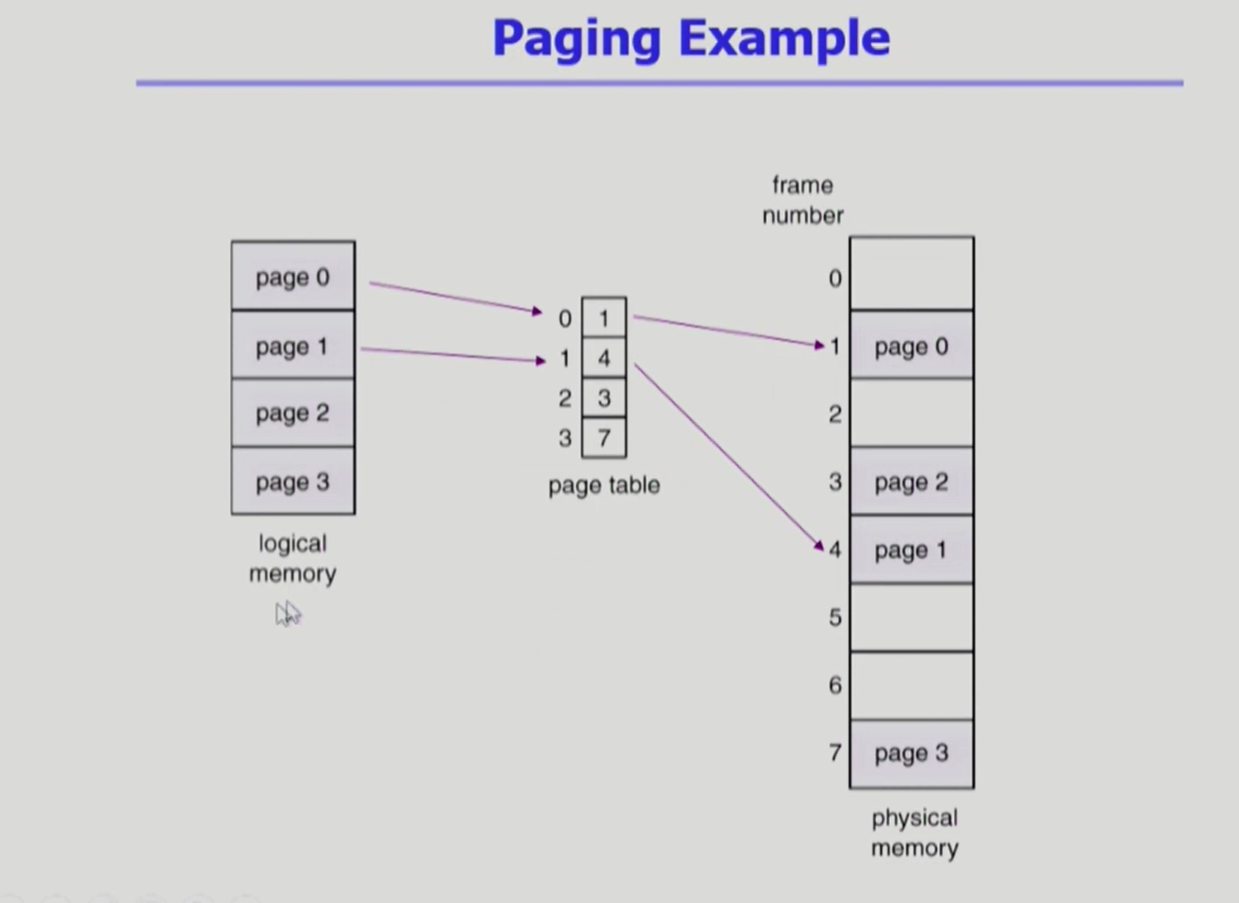

- 페이징이란 프로그램을 페이지라는 작은 단위로 나누고, 물리 메모리를 페이지와 동일한 크기로 나누는 메모리 관리 기법을 말한다. 그러니까 프로세스의 메모리를 분산 및 할당 Noncontiguous allocation과 물리 메모리를 고정 분할 Fixed partition 방식을 채택.

- 페이지의 크기는 4kb. 물리 메모리와 논리 메모리(프로그램)를 4kb로 고정 분할함. 메모리 주소를 가지는 한 단위를 frame이라 하며 해당 크기는 페이지와 같은 4kb.

- Page Table을 사용하여 논리 주소와 물리 주소를 번역.

- 메모리의 모든 공간이 동일한 크기(4kb)를 가지기 때문에 내부 조각이 발생하지 않음. 외부 조각은 4kb 보다 작은 한 조각만 존재함. 그러므로 hole로부터 자유로움.

- 현대적인 메모리 관리 기법 중 하나임.

2. 주소의 번역 방식 Address Translation Architecture

2.1 페이지 테이블 Page Table

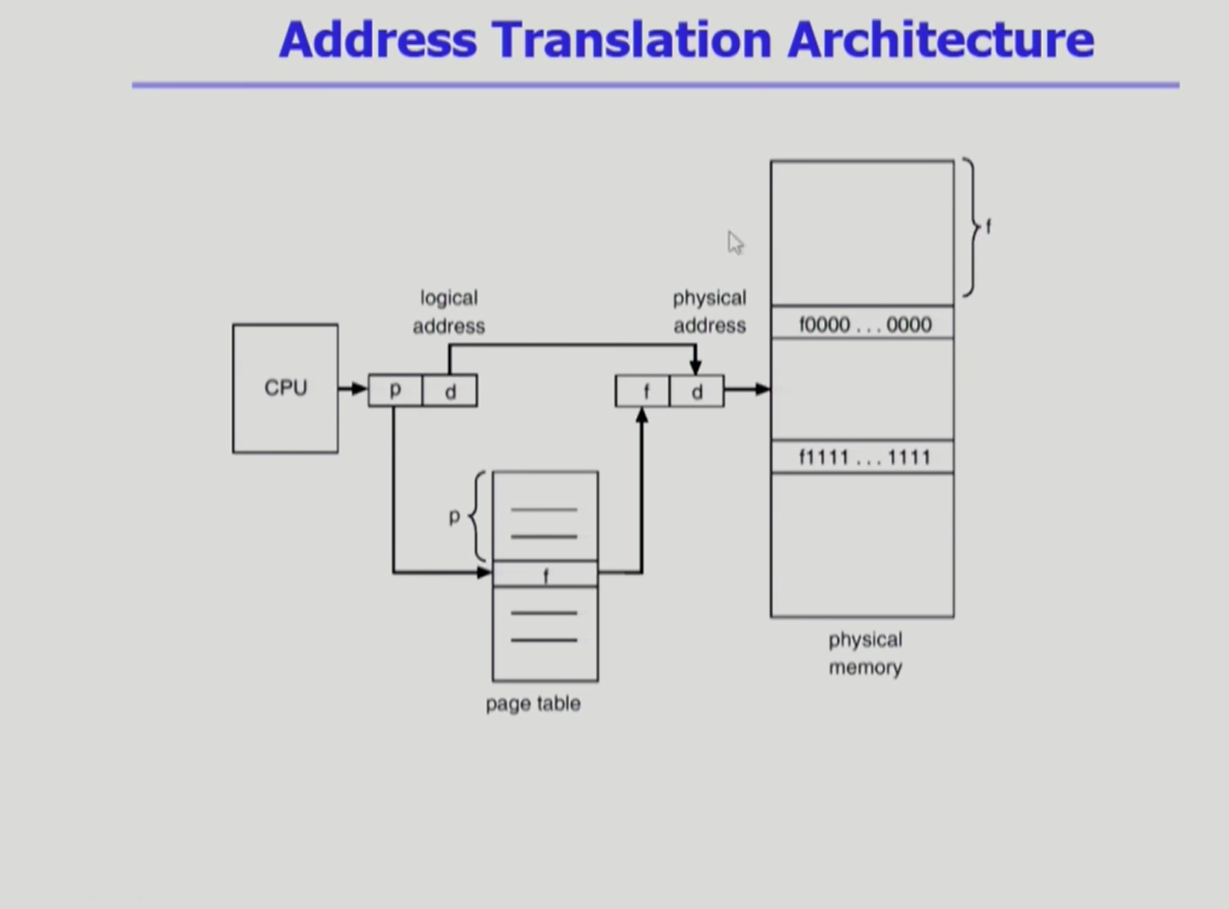

- cpu가 instruction할 데이타를 호출. Page Table은 논리 주소에 대응하는 물리 주소를 찾음. 물리 주소를 통해 실제 물리 메모리에 해당 값을 호출.

- 한편, Page Table은 현대 cpu의 입장에서는 너무 큰 용량을 필요로 함. 32bit cpu는 2^32(4gb)만큼의 주소공간을 가질 수 있다. 페이지는 하나당 4kb. 4gb/4kb=1M으로 페이지가 1M개 만큼이 있으며, 1M 개의 페이지를 인덱스로 나열한 주소공간을 Page Table은 가지고 있어야 한다. (index로 되어 있기 때문에 주소공간의 값은 변할 수 없다)

- 한편, 페이지 테이블을 구성하고 있는 엔트리는 4b만큼을 용량으로 한다. 그러므로 1M개 * 4b는 총 4mb로, 페이지 테이블은 4mb를 가진다.

- 기존에 물리 메모리와 논리 메모리의 주소를 번역하던 MMU는 레지스트리가 단 두 개이다. 그러나 페이지 테이블은 4mb이다. 너무 큰 용량으로 인해 페이지 테이블은 MMU와 같은 별도의 하드웨어를 구성하기 어렵다. 결국 테이블은 물리 메모리에 저장된다. cpu는 데이타에 접근하기 위하여 1) 페이지 테이블 2) 페이지 테이블이 가리킨 주소, 총 두 번 물리 메모리에 접근한다.

- MMU는 PageTable을 가리키기 위한 장치로 활용한다. MMU가 가지는 레지스터 두 개는 각각 page table의 물리 주소와 page table의 크기를 할당받는다.

2.2 TLB Translation Look-aside Buffer, Associative Register

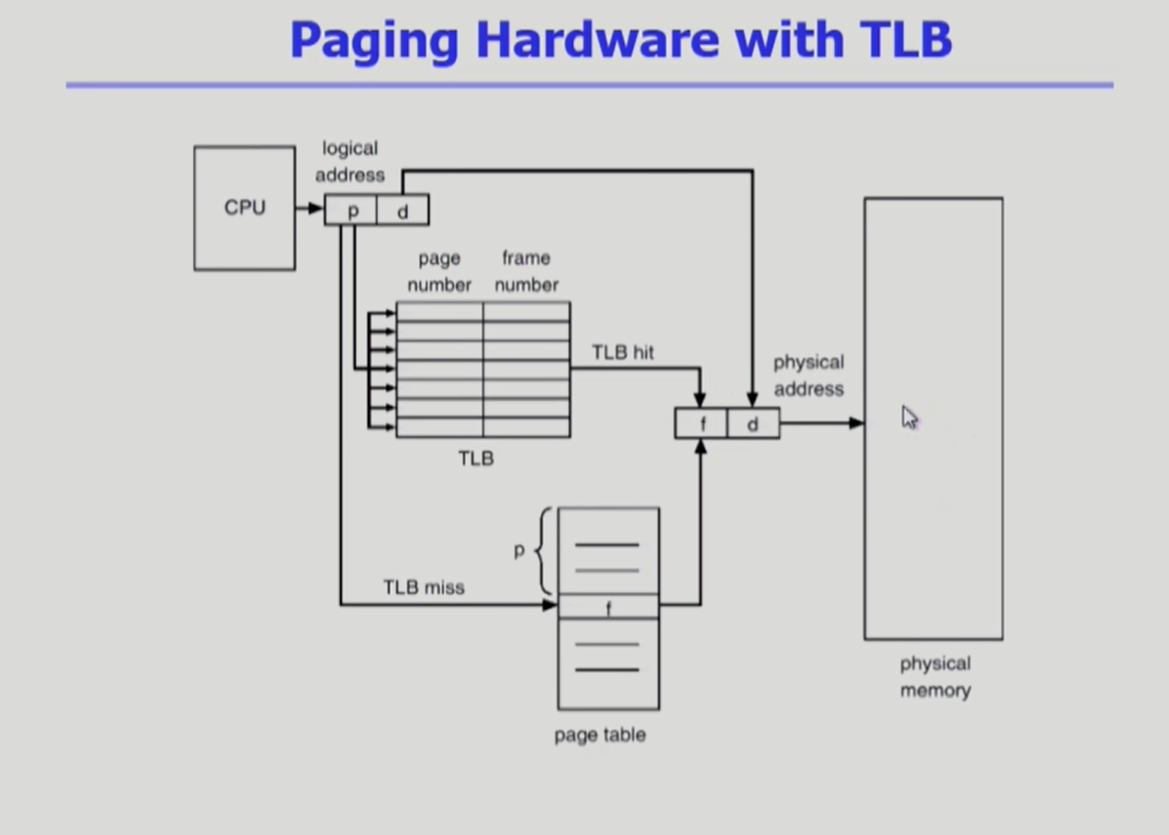

- 페이지 테이블은 두 가지 주요 단점이 존재. 큰 용량, cpu가 메모리에 두 번 접근하는 비효율성(논리 주소(페이지 테이블) 접근, 물리 주소 접근). 이 두 개를 해소하기 위하여 페이지 테이블을 위한 일종의 캐쉬 메모리를 하드웨어로 가짐. 이를 TLB라 함.

- TLB는 페이지 테이블에서 자주 호출되는 주소를 가지고 있다. cpu의 주소 탐색 과정은 다음과 같다. cpu -> 논리 주소 -> TLB -> pageTable -> 물리 주소. 만약 TLB에서 원하는 물리 주소를 확인하면, 페이지 테이블(물리 메모리)에 접근하지 않고, 바로 물리 주소에 접근한다.

- cpu가 페이지 테이블에서 주소를 찾을 때, 페이지를 기준으로 분류하여 검색한다. 하지만 TLB는 페이지를 기준으로 하지 않아 탐색 시간이 오래 걸릴 수 있다. 그러므로 parallel search 탐색 방식을 지원한다.

- TLB는 페이지 테이블의 캐쉬 메모리이기 때문에 페이지 테이블의 위치를 필요로 한다. TLB는 물리 메모리에 바로 접근하기 때문에 물리 주소를 가지고 있다. 그러므로 TLB의 엔트리 하나는 페이지 테이블과 물리 메모리 주소 두 개를 가지고 있다.

3. Two-Level Page Table

3.1 이중 페이지 테이블이란?

- 페이지 테이블은 현대의 cpu에서 4mb를 필요로 한다.

- 페이지 테이블은 물리 메모리 전체의 인덱스를 가져야 하기 때문에 용량이 고정되어 있다. 그리고 물리 메모리는 프로세스 마다 다르게 사용될 수 있기 때문에, 프로세스 마다 각 각 하나씩 가진다.

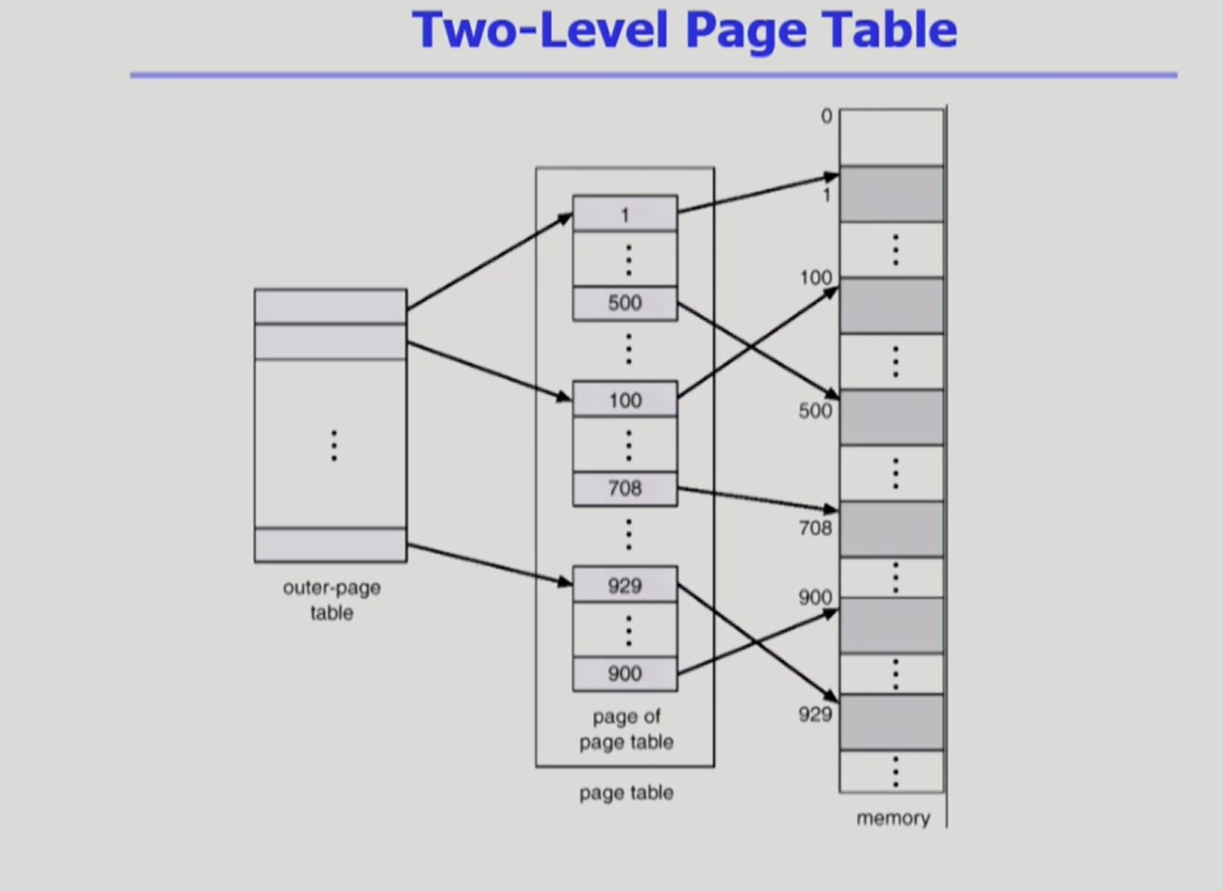

- 한편, 모든 페이지를 사용하지 않는다. 실제 프로세스의 사용을 살펴보면 사용하지 않는 페이지가 매우 많다고 한다. 사용하지 않는 페이지를 null처리 하기 위한 기법이 바로 Two - Level Page Table이다.

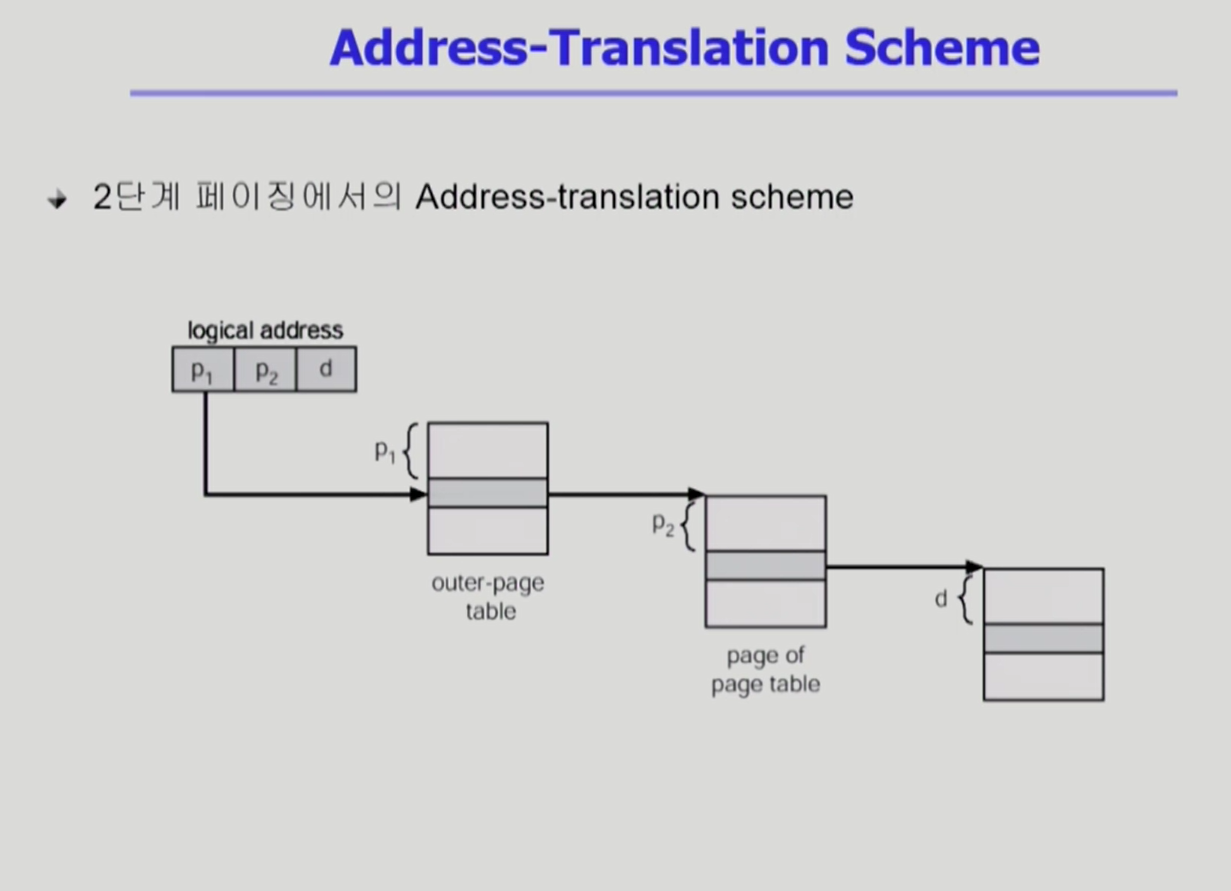

- 외부 페이지 테이블 outer page table을 하나 만든다. 그리고 그 페이지는 내부 페이지 테이블 page of page table을 가진다. 그리고 사용하지 않는 page of page table을 null로 한다.

3.2 32bit cpu의 주소 공간의 분할

- 페이지 테이블은 outer-page table, page of page table, 총 두 개를 가진다. 각 각 p1, p2이라 한다. p2의 페이지 테이블의 엔트리는 물리 주소를 가리킨다.

- page of page table의 엔트리 : 페이지는 4kb이다. 그리고 1b 단위로 주소 공간을 가진다. 그러므로 4kb/1b=4b, 그러니까 4000개 만큼의 주소공간을 필요로 한다. 4b개는 2^12로서 32bit의 주소 공간 중 12bit를 차지한다.

- page of page table : Page table은 특별한 지위를 가지지만, 물리메모리에 저장되는 하나의 페이지이다. 그러므로 한 프레임(4kb) 만큼 용량을 점유한다. 그리고 하나의 엔트리는 4byte만큼의 용량을 차지한다. 그러므로 하나의 page of page table은 1000개를 주소공간으로 가진다. 그러므로 10bit을 차지한다.

- outer page table : 12bit와 10bit가 남은 10bit을 가진다.

4. 페이지 테이블의 두 개의 bit

- 페이지 테이블을 보조하기 위하여 두 개의 bit가 존재한다.

4.1 Valid bit

- 페이징 기법은 필요로 하는 페이지만 물리 페이지에 적재한다.

- 페이지 테이블은 물리 메모리에 적재된 페이지에 대하여 Valid(v)로 표시하며, 물리 메모리에 없는 페이지를 Invalid(i)로 표시한다. swap out된 경우는 i이다.

- v는 접근 가능하며 i는 접근이 불가능하다.

4.2 Protected bit

- 페이지의 권한을 나타낸다.

- read-only 와 read/write로 나뉜다.

5. Inverted Page Table

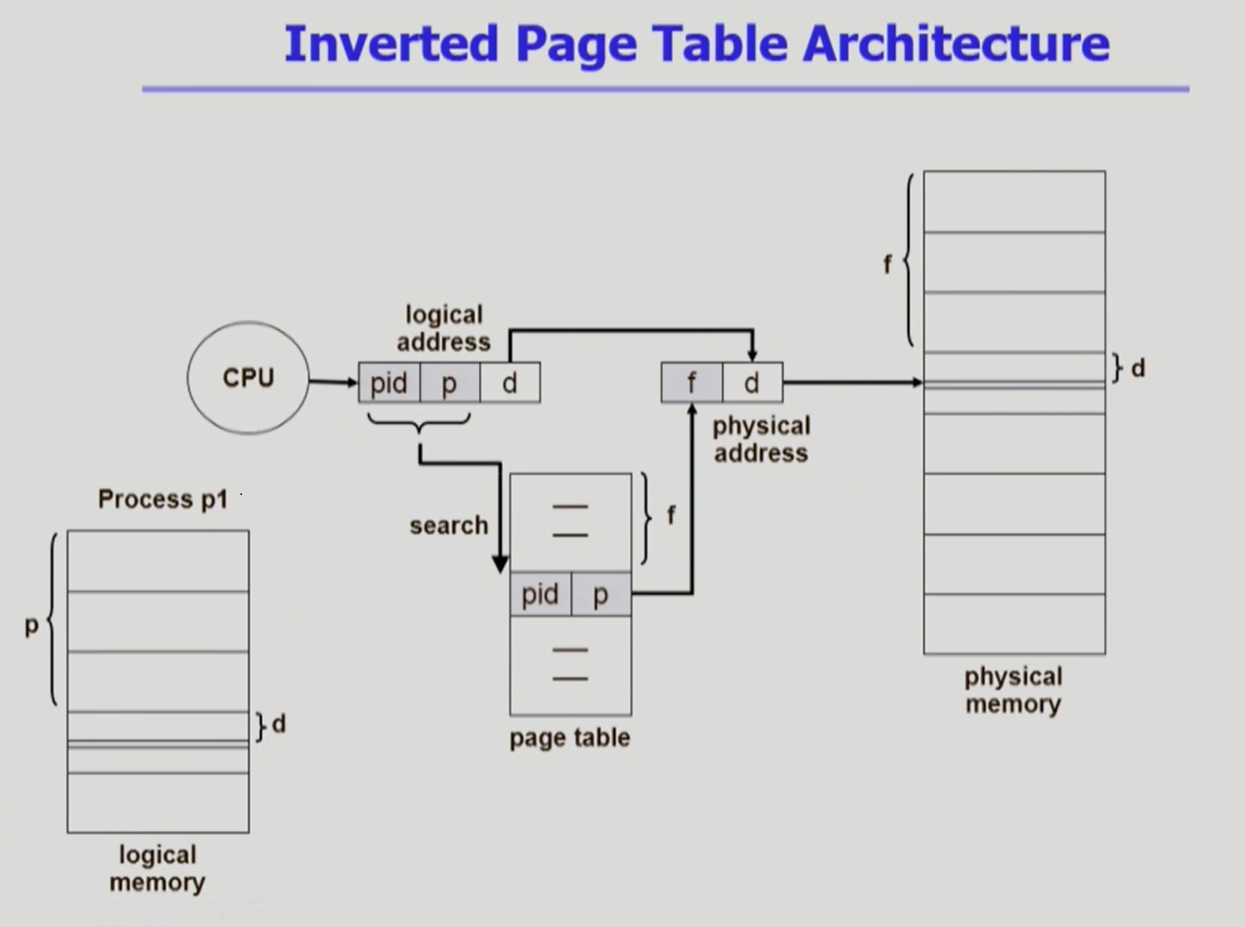

- 페이지 테이블이 프로세스 별로 있기 떄문에 메모리 효율성 문제가 있음.

- 페이지 프레임을 기준으로 페이지 테이블의 엔트리를 구성. 엔트리는 프로세스의 번호(pid)와 page 번호를 가짐.

- cpu는 페이지 테이블에서 pid와 p를 찾음. 그러면 그것의 offset을 찾을 수 있음. 해당 offset의 위치가 물리 메모리이므로, 프레임의 offset의 값과 페이지 내의 오프셋을 기준으로 물리 메모리를 접근.

- 페이지 테이블 전체를 탐색해야 하는 문제가 발생. associative register를 활용.

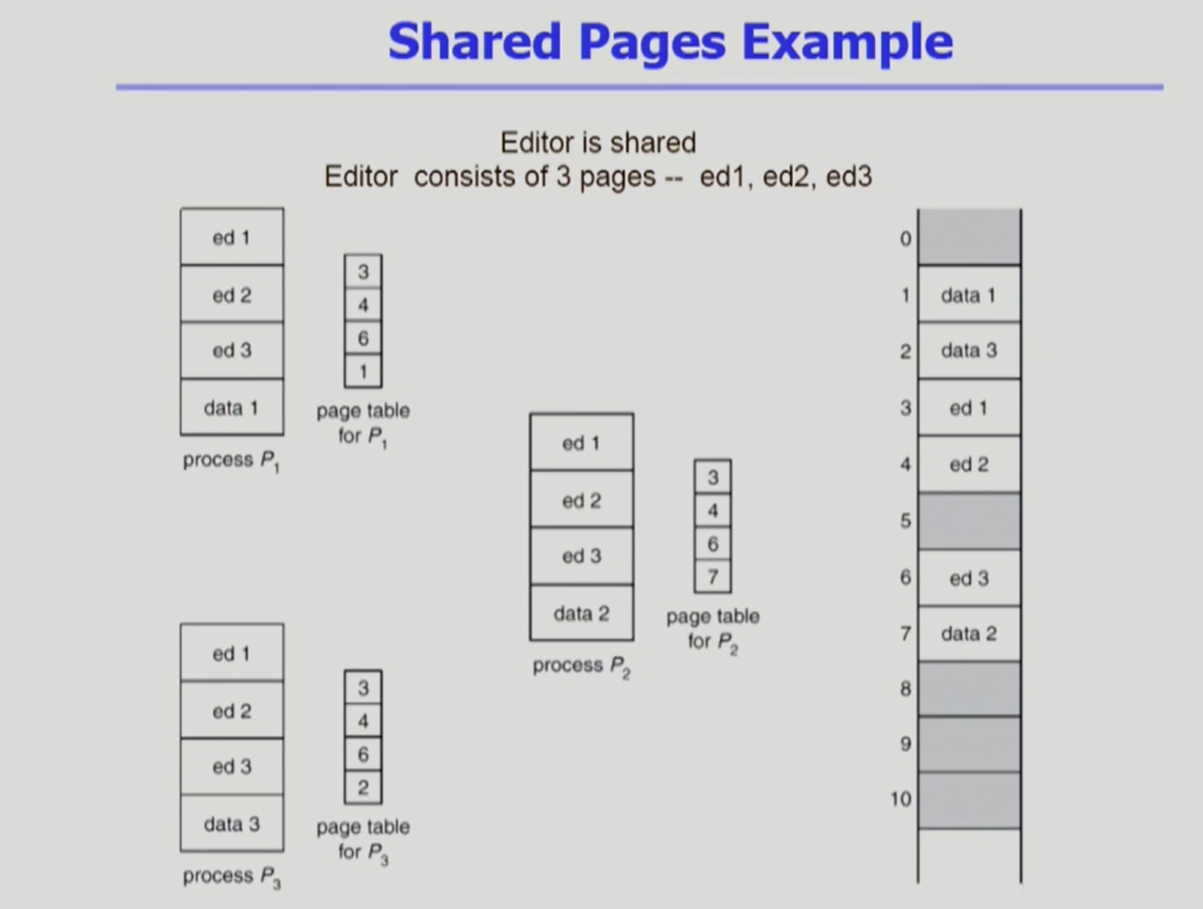

6. Shared Page

- 프로세스가 공유하는 데이타를 공유. 대체로 read-only인 code를 공유.

- Shared page에 사용하는 데이타의 논리주소가 모든 프로세스의 논리주소와 동일해야함.