ARM Processors

- RISC 구조를 가지는 32비트 프로세서군을 가르키는 용어

- 내부 구성이 간단하여 동작속도가 빠르면서도 전력 소비가 작음

- 휴대폰, 게임기 등의 모바일 기기 부문에서 많이 사용

- 프로세서 코어를 설계해서 마이크로프로세서를 제조하는 다른 여러 회사(ex. 삼성전자, ST Micorelectronics, NXP 등)에 프로세서 코어의 설계 내용을 IP(Intellectual Property)형태로 판매함

Cortex Processors

- ARMv7 아키텍처의 코어를 가지는 프로세서

- A(application), R(real time), M(microcontroller) Series

- 각 시리즈 별로 1~10(또는 그 이상)의 숫자를 부여, 큰 숫자일수록 고성능

- Cortex-A series

- 가장 고성능의 프로세서 -> MPU

- 복잡한 운영 환경, 고성능이 요구되는 어플리케이션의 구현에 적함

- Architecture: ARMv7-A

- Instruction set : ARM, Thumb-2

- 프로세서 종류 : Cortex-A8, Cortex-A9

- PMP나 스마트폰, 넷북과 같은 기기에 많이 사용

- Cortex-R series

- Real time 동작이 요구되는 high-end embedded system용

- Architecture : ARMv7-R

- Instruction set : ARM, Thumb-2

- 프로세서 종류 : Cortex-R4, Cortex-R4F, Cortex-R4F

- 임베디드 제품에서 필요한 복잡한 알고리즘 제어와 실시간 작업처리가 가능

- Cortex-M series

- 8bit, 16bit MCU 시장을 타겟으로한 프로세서

- 마이크로컨트롤러 및 FPGA에 최적화된 프로세서

- Architecture : ARMv7-M

- Instruction set : Thumb-2 only

- 프로세서 종류 : Cortex-M0, Cortex-M1, Cortex-M3

- 자동차나 전자분야 등 가격에 민감한 임베디드 어플리케이션 분야에 사용

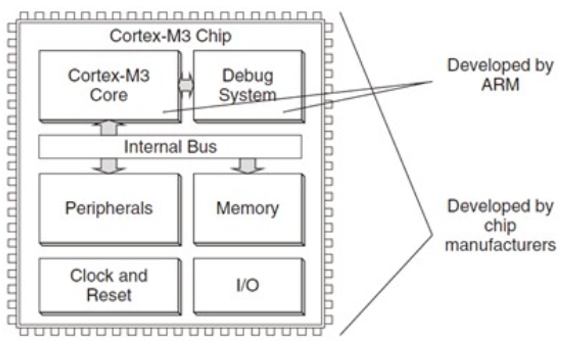

Cortex-M3 Processor vs Cortex-M3-Based MCU

- "Cortex-M3 프로세서"

ARM사에서 설계한 프로세서 코어 - "Cortex-M3 기반의 마이크로 컨트롤러"

프로세서 코어를 바탕으로 여러 가지 주변 장치를 추가하여 완성된 마이크로 컨트롤러

Structure of Cortex-M3 Processor

Processor Core

- ARMv7-M 아키텍쳐를 기반

- Thumb-2 명령어 세트 사용 : 16bit, 32bit 명령어가 결합

- 명령어 버스와 데이터 버스가 분리된 구조

- 명령어 인출 및 데이터 읽기/쓰기의 동시 수행

- 3단 파이프라인 구조를 가짐

- 2개의 동작 모드

- Thread 모드, Handler 모드

- 2개의 메모리 접근 레벨

- Privileged(특권) 접근레벨, User(사용자) 접근레벨

- 인터럽트 서비스 루틴 진입과 탈출의 시간이 빠른다.

NVIC, MPU and Bus Interface

- NVIC(Nested Vectored INterrupt Controller)

- 프로세서에 내장된 인터럽트 제어기 -> 인터럽트 처리를 효율적으로(인터럽트 핸들링)

- 중첩된 인터럽트를 쉽게 처리할 수 있는 구조

- MPU(Memory Protection)

- 특권 접근레벨과 사용자 접근 레벨 시에 메모리 액세스에 대한 제한을 둘 수 있다.

- 일반적으로 운영체제가 MPU를 설정하여 특권 접근레벨에서 사용하는 데이터(ex. 운영체제의 커널 등)를 사용자 접근레벨의 프로그램에서 접근하지 못하도록 막아주는 형태로 사용

- Bus Interface

- 버스 인터페이스를 위해 내부에 버스 매트릭스를 가지고 있다.

- 외부로는 I-code 버스, D-code 버스 및 시스템 버스가 나온다.

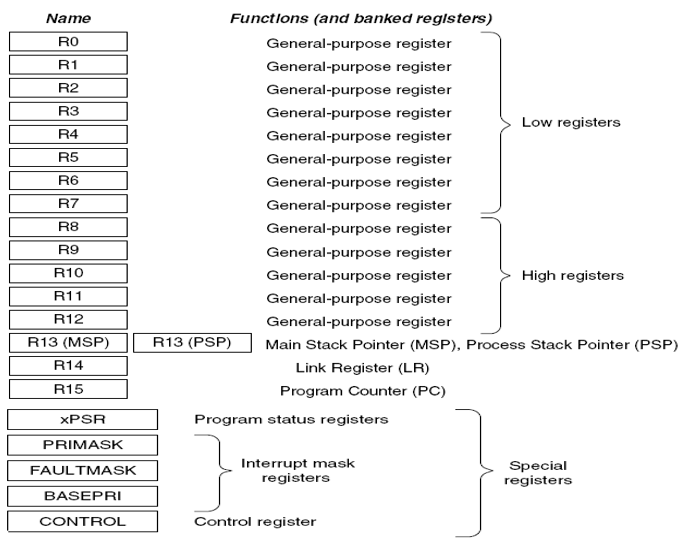

Processor Core : Registers

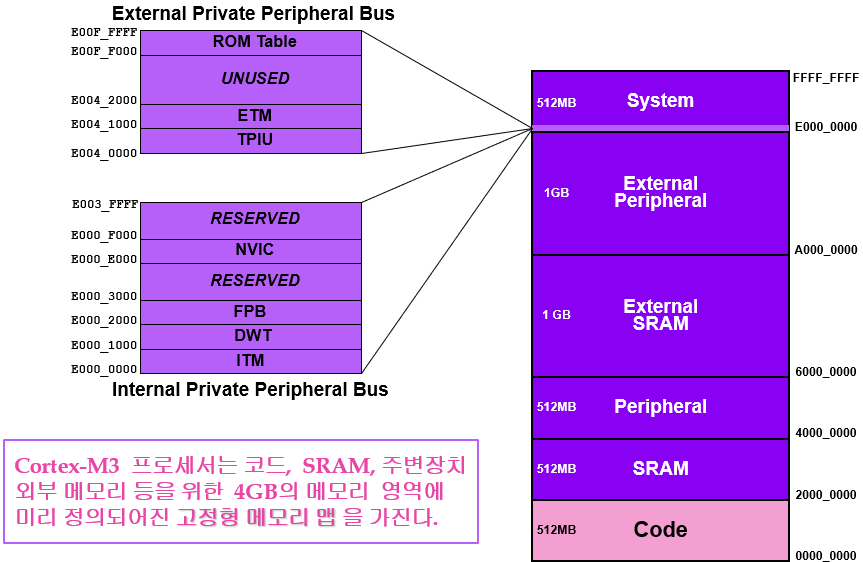

Cortex-M3 Memory Map

LPC1768 메모리와 비교해보기

Exceptions

- Exceptions(예외)

- 프로세서가 동작 도중 예상하지 못한 상황, 예외적인 상황, 또는 외부 인터럽트가 발생하는 경우

- 최대 255개까지(1~255) 가능

- System Exception과 External Interrupt로 나뉜다.

- System Exception

- Cortex-M3 프로세서 내에서 발생

- Reset, NMI, Hard fault 등

- 최대 15개까지(1번부터 15번까지) 가능

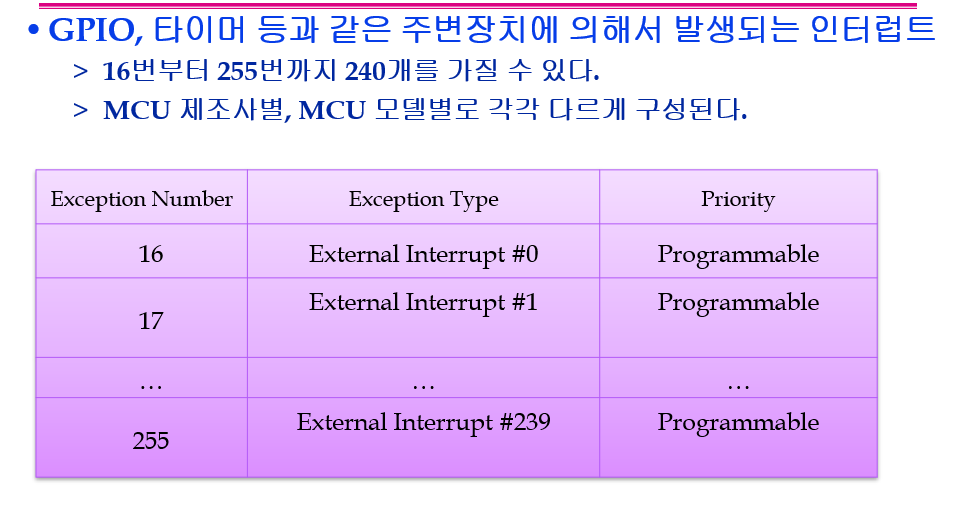

- External Interrupt

- 주벽 장치(GPIO, Timer 등)에서 발생

- 최대 240개까지(16번부터 255번까지) 가능

- MCU 제조사 별로 구성이 다르다.

NVIC : Nested Vectored Interrupt Controller

- 중첩 벡터형 인터럽트 제어기

- Cortex-M3의 Interrupt(Exception)의 제어를 담당

- 모든 Interrupt(Exception)에 대한 우선 순위를 결정하고 이를 처리

- NVIC와 Cortex-M3 Processor Core는 서로 긴밀하게 연결

- 빠른 인터럽트 처리가 가능

- 현재 실행중인 인터럽트보다 우선 순위가 더 높은 인터럽트가 발생한 경우, 현재의 동작을 멈추고 높은 순위의 인터럽트를 먼저 처리한다.

- 이때 먼저 실행 중이던 인터럽트는 우선 순위가 높은 인터럽트가 끝나면 다시 실행을 하게 된다.

- NVIC는 미리 정해진 우선 순위에 따라 자동적으로 중첩 인터럽트 동작을 수행함

- 이 경우 레지스터의 stacking 및 unstacking은 자동으로 처리됨

Vectored Interrupts

- Vector table : Cortex-M3 프로세서에서 메모리 내에 인터럽트 서브스 루틴(ISR)의 시작 주소를 저장하는 곳

- 인터럽트 발생 시에 별도의 소프트웨어가 필요없이 바로 대응되는 ISR의 시작 주소를 알 수 있다. -> Vectored Interrupt 동작이라고 한다.

- 인터럽트를 처리하는 시간이 빨라진다.