이번에는 컴퓨터구조_2에서 알아본 CPU가 어떻게 동작하는지 알아보겠습니다 !!

이전 컴퓨터구조 포스팅에 말한 대로, CPU는 ALU + 제어장치 + 레지스터 로 구성됩니다.

각각이 어떻게 작동해서 하나의 두뇌처럼 일을 하는지 알아보겠습니다✨

1. CPU 구성요소의 역할

-

연산장치

- 연산에 필요한 데이터를 레지스터에서 가져오고, 연산 결과를 다시 레지스터로 보냄 -

제어장치

- 명령어를 순서대로 실행할 수 있도록 제어하는 장치

- 주기억장치에서 프로그램 명령어를 꺼내 해독하고, 그 결과에 따라 명령어 실행에 필요한 제어 신호를 기억, 연산, 입출력 장치로 보냄

- 신호를 받으면 다음에 수행할 동작 결정 -

레지스터

- 고속 기억 장치

- 명령어 주소, 코드, 연산에 필요한 데이터, 연산 결과 등을 임시로 저장

범용 레지스터와 특수목적 레지스터로 구분 (IR, MAR, MBR, PC 등이 특수목적에 해당됨)

2. CPU 동작 과정과 명령어 사이클

1) 동작 순서보기

- 주기억장치는 입력 장치에서 입력받은 데이터 또는 보조기억장치에 저장된 프로그램을 읽어옴

- CPU는 프로그램을 실행하기 위해 주기억장치에 저장된 프로그램 명령어와 데이터를 읽어와 처리하고 연산 결과를 다시 주기억장치에 저장

- 주기억장치는 처리 결과를 보조기억장치에 저장하거나 출력장치로 보냄

+) 제어장치는 1~3 과정에서 명령어가 순서대로 실행되도록 각 장치를 제어

✔️ CPU가 주기억장치에서 한 번에 하나의 명령어를 인출하여 실행하는데 필요한 일련의 활동을 **명령어 사이클**이라고 한다.

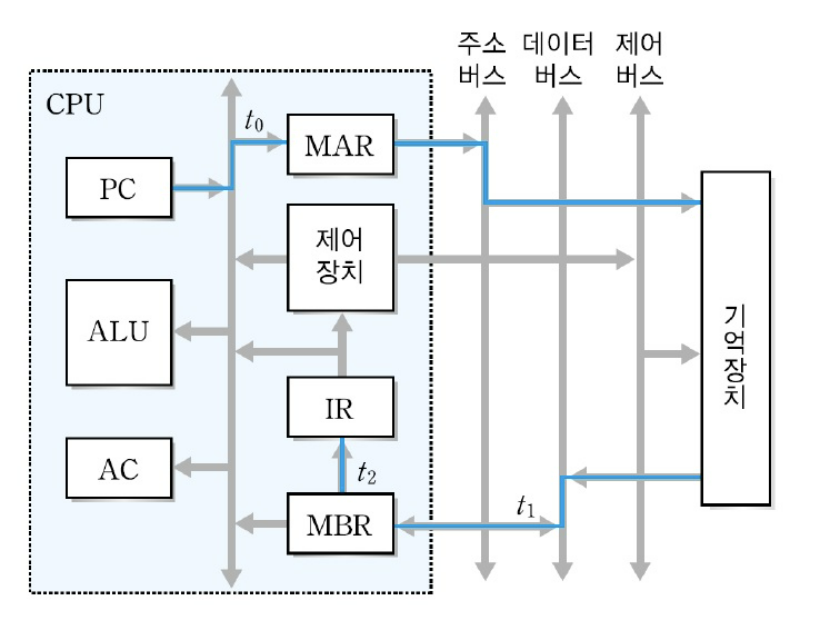

2) 명령어 인출 사이클

- PC에 저장된 주소를 MAR로 전달

- 저장된 내용을 토대로 주기억장치의 해당 주소에서 명령어 인출

- 인출한 명령어를 MBR에 저장

- 다음 명령어를 인출하기 위해 PC 값 증가시킴

- 메모리 버퍼 레지스터 (MBR)에 저장된 내용을 명령어 레지스터에 전달

T0 : MAR <- PC

T1 : MBR <- M[MAR], PC <- PC+1

T2 : IR <- MBR3) 명령어 실행 사이클

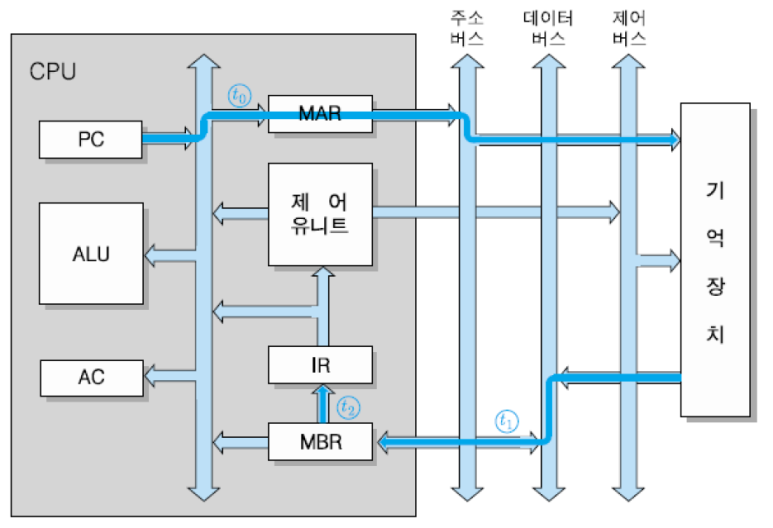

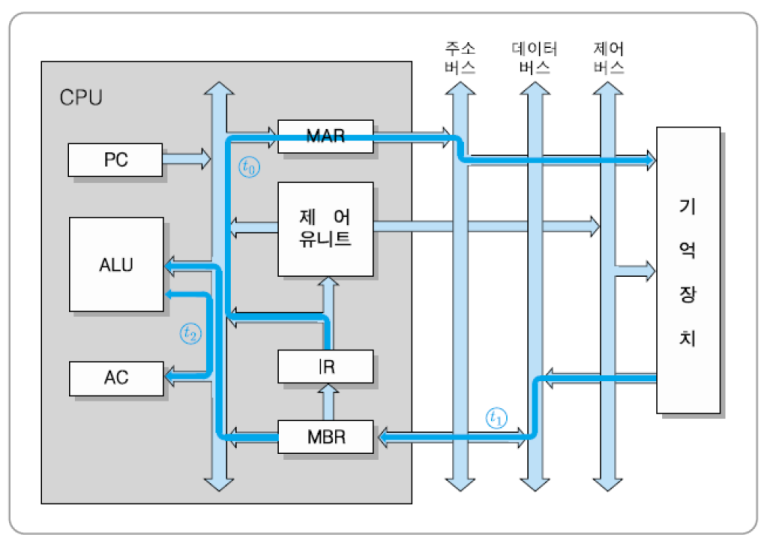

- 명령어 레지스터 IR에 있는 명령어의 주소 부분을 MAR로 전송합니다.

- 그 주소가 지정한 기억장소로부터 데이터를 인출하여 MBR로 전송합니다.

- 그 데이터를 AC에 적재합니다.

T0 : MAR ← IR(Addr)

T1 : MBR ← M[MAR]

T2 : AC ← AC + MBR[Reference]

https://blog.naver.com/PostView.naver?blogId=ben4109&logNo=222284380523

https://velog.io/@kimmy/CS-CPU-%EC%9E%91%EB%8F%99-%EC%9B%90%EB%A6%AC

https://gyoogle.dev/blog/computer-science/computer-architecture/%EC%A4%91%EC%95%99%EC%B2%98%EB%A6%AC%EC%9E%A5%EC%B9%98%20%EC%9E%91%EB%8F%99%20%EC%9B%90%EB%A6%AC.html