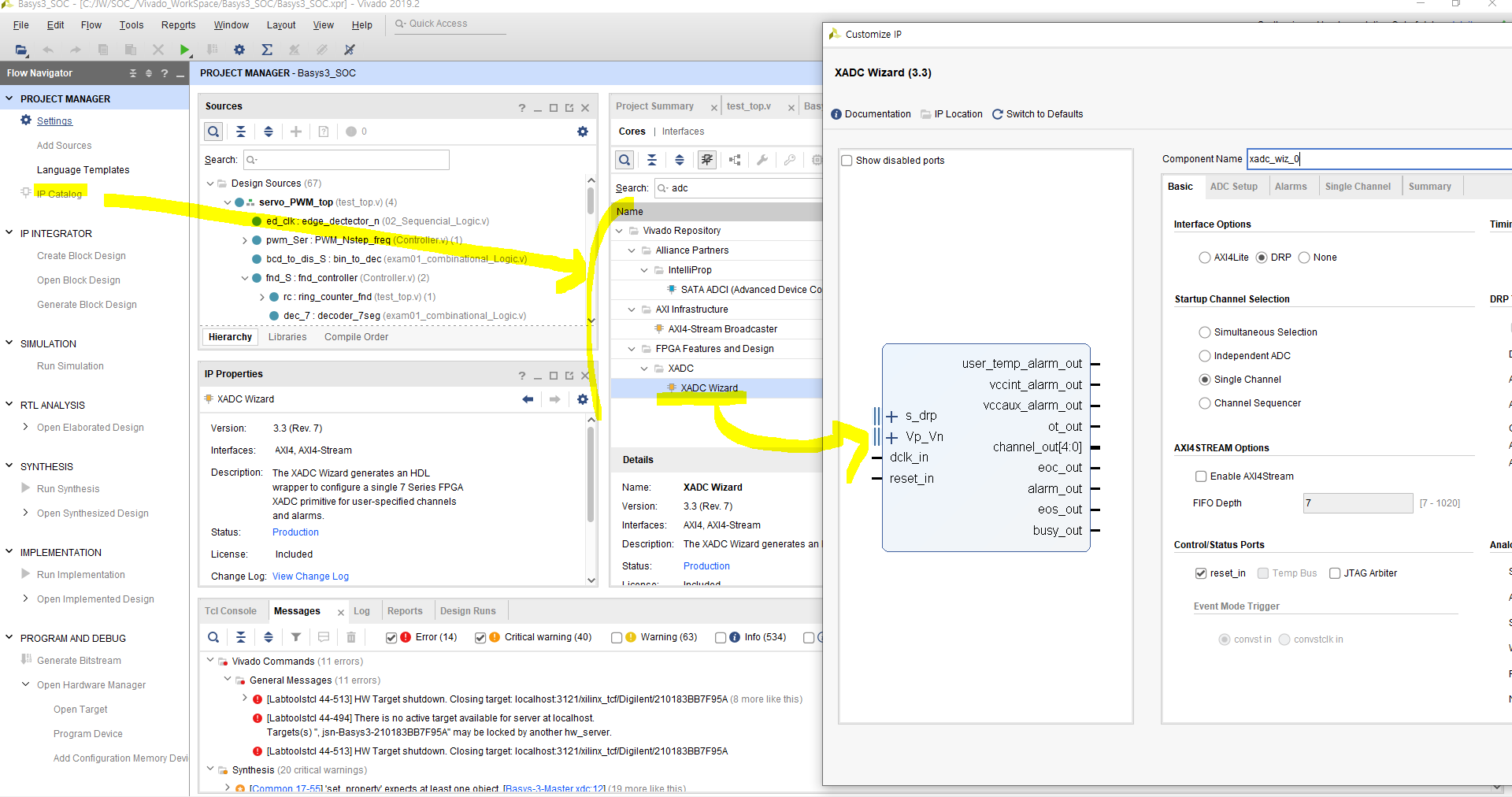

Verilog에서는 Digital로 Analog회로 만드는것은 불가능하기떄문에 Basys-3의 XADC를 활용함!

가변저항의 값(아날로그)을 XADC를 활용해 Digital값으로 변경

사전지식

- 가변저항은 길이와 관계가 있다. 가변저항의 손잡이부분을 돌리면 저항의 길이가 짧아지고 길어지기 떄문에 이 손잡이를 돌리면서 저항의 크기를 조절할 수 있다.

가변저항 실습

- Basys-3의 ADC를 활용한 가변저항 제어

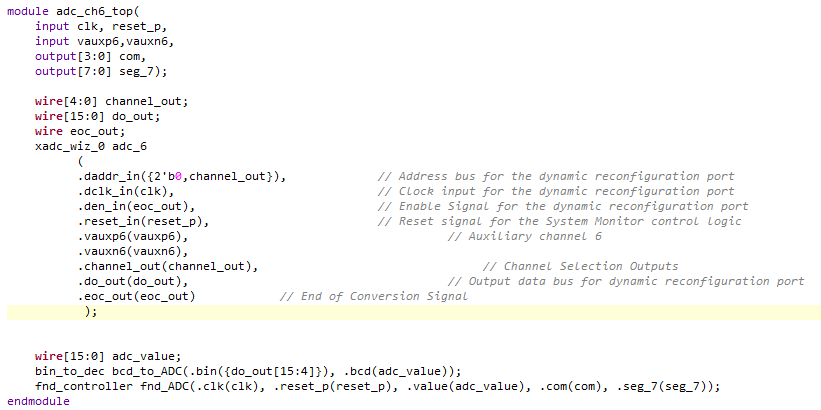

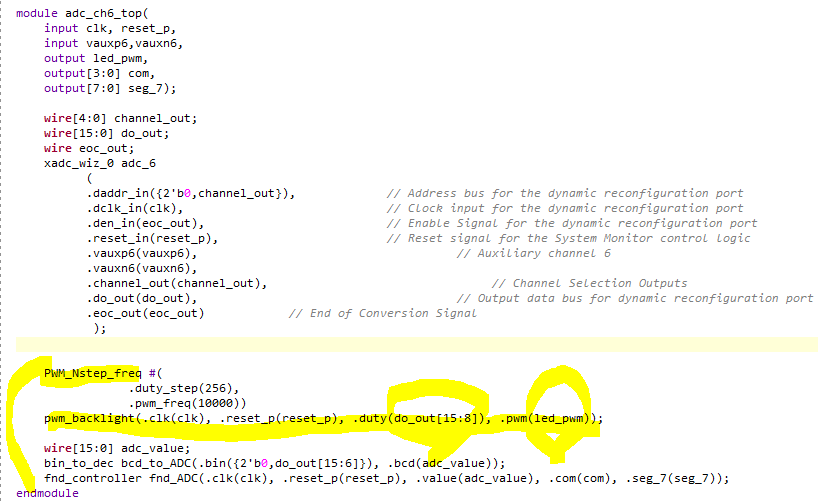

먼저dclk_in과reset_in은clk과reset_p이 들어간다. 이 예제에서는 가변저항의 전압을 아날로그 신호로 받습니다. 이 신호를eoc_out이 디지털 신호로 전환해주고 이 작업이 완료되면den_in에서 완료가 되었다고 신호를 보냅니다(아날로그 -> 디지털 전환 작업이 완료되면 enable신호가 1이됩니다.)enable신호를 받게되면do_out에서 전환된 값을 출력합니다. 그리고channel_out이 활성화되면서 채널을 선택하여 출력된 값을 선택한 채널로 내보내게 됩니다. 이channel_out에서 출력한 신호는 현재 우리가 한개의 채널을 쓰고 있지만 다양한 채널들이 있습니다 그래서channel_out을 이용해서 원하는 채널을 선택하여do_out에서 출력 된 값이 전달됩니다. 그리고channel_out에 전달된 값을daddr_in에 저장합니다. 그리고 앞에 2개의 비트를 0으로 받은 이유는daddr_in은 7비트이지만channel_out은 5비트이기 때문입니다. 그리고 최종적으로daddr_in에 저장된 값이JXADC핀을 통해 외부로 출력할 수 있습니다.

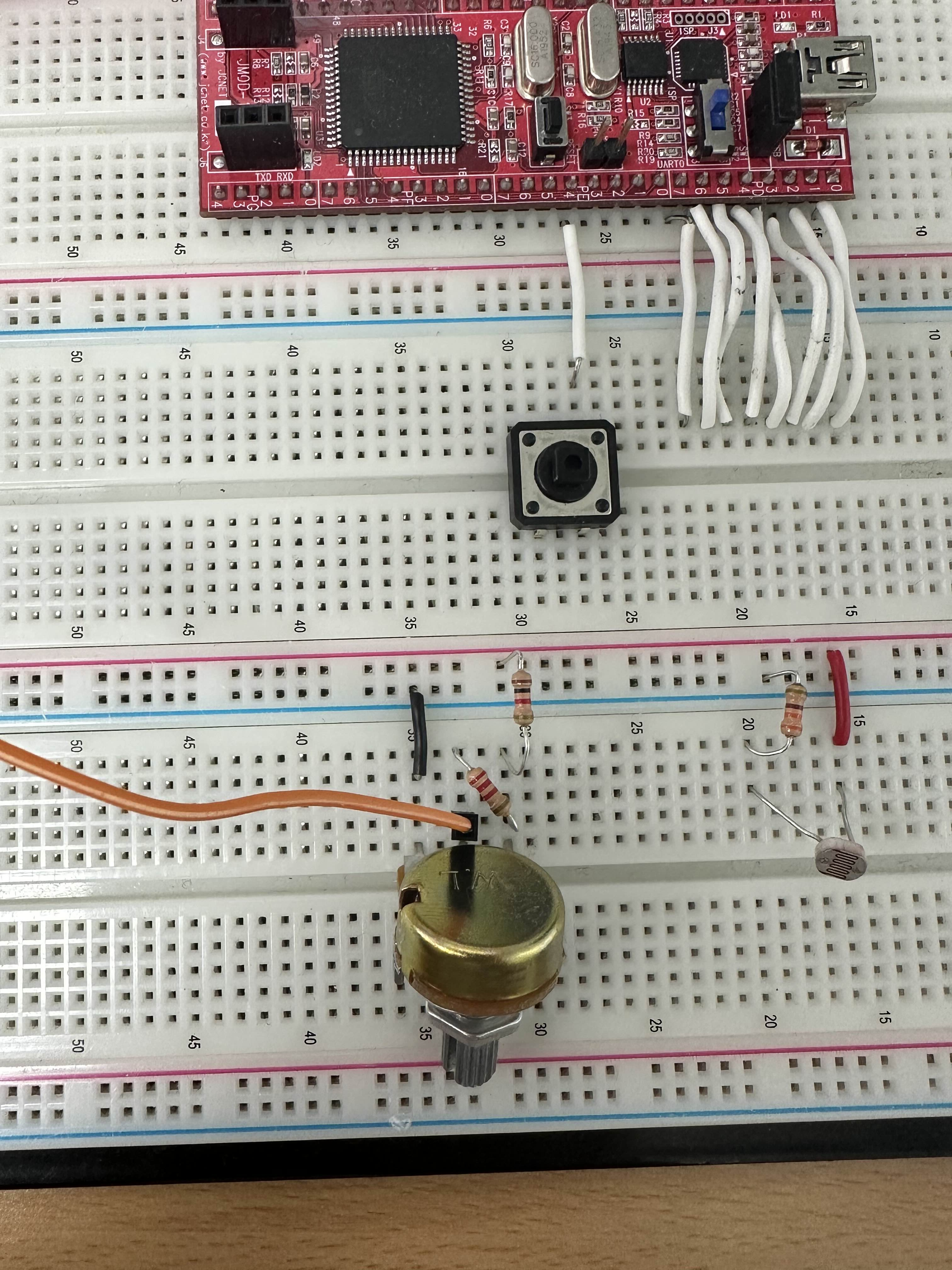

실습사진

조도센서의 값(아날로그)을 XADC를 활용해 Digital값으로 변경

- 조도센서 : 조도센서는 주변 밝기를 측정하여 입력 값으로 보내는 센서입니다.(조도 : 단위 면적당 단위 시간에 받는 빛의 양) 빛의 양이 얼마인지 측정하는 센서로 빛 센서라고도 부릅니다. 조도센서는 조도에 따라 저항의 값이 변화합니다. 저항은 전류를 방해하는 힘인데요. 빛의 밝기에 따라 조도센서는 조도센서 내의 저항값을 결정합니다. 빛의 양과 저항값은 반비례 관계로, 주위가 밝으면 조도 센서의 저항값이 감소하고 주위가 어두우면 조도 센서의 저항이 증가합니다. 조도센서는 황화카드뮴으로 만들어졌는데요. 황화카드뮴은 카드뮴의 화학물로 갈색의 결정성 분말입니다.빛을 많이 받게되면 저항이 작아지고, 빛을 적게 받으면 저항이 커지는 성질을 가지고 있습니다. 그래서 조도센서를 황화카드뮴의 화학식인 CdS를 따서 CdS 센서라고도 부릅니다.

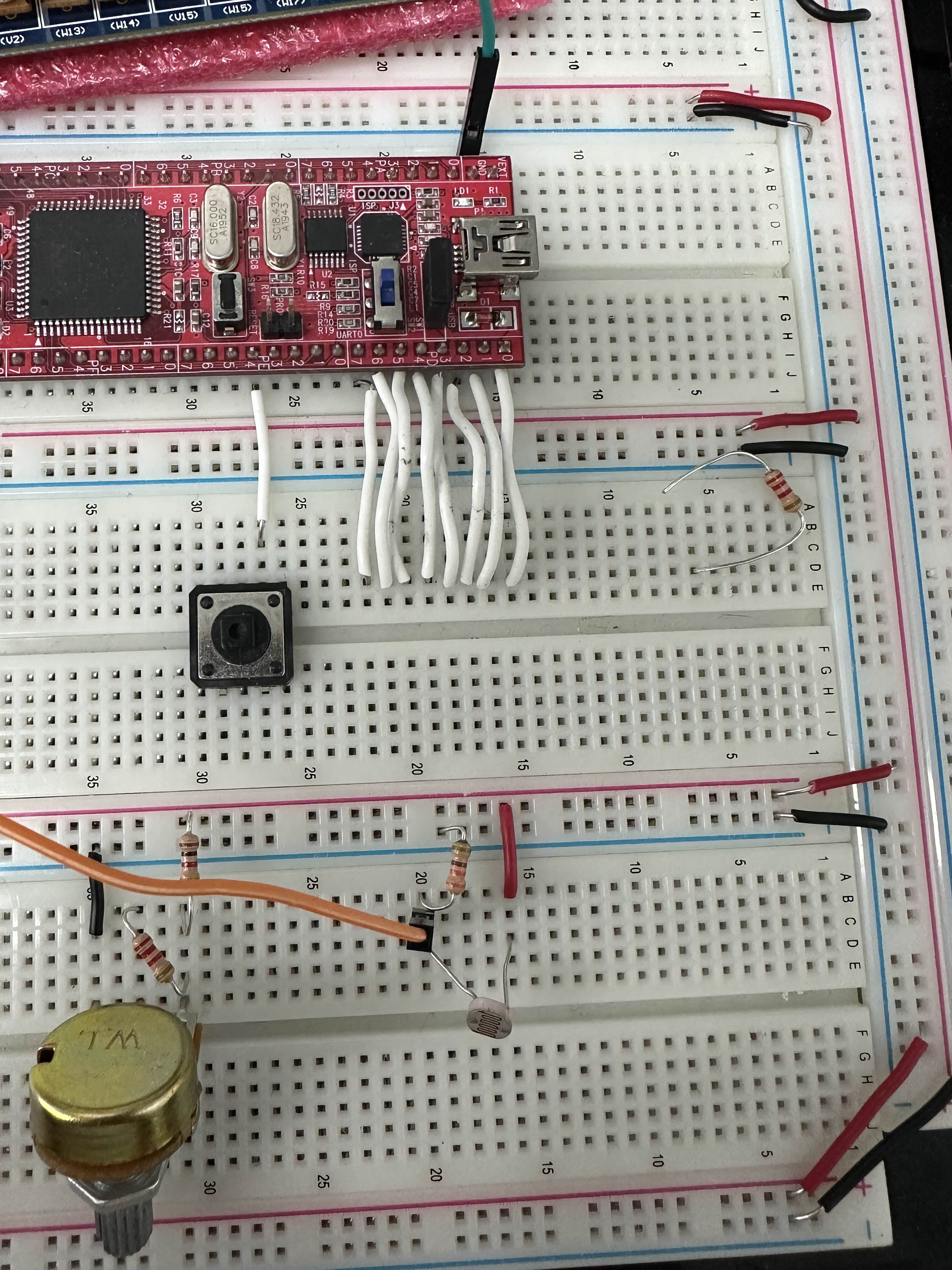

실습사진

- 위 실습 사진은 조도센서로 받은 저항 값을

PWM의duty로 전달하여Basys-3의 LED의 밝기를 조절할 수 있습니다.