SL 은 입력에따라 출력이 정해지지는 않는다. 이전출력의 값에 따라 현재출력이 달라진다.

- 왜? 메모리기능을 가지고있기 때문. 즉! 메모리기능이 존재하면 순서논리회로(SL)이다.

- CL뒤에 F/F이 붙으면 SL

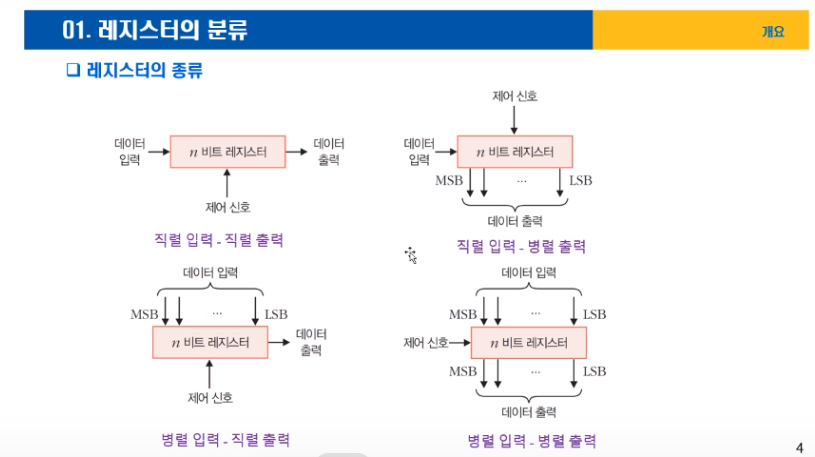

레지스터

- 레지스터

- 직렬입력은 통신에서 사용 : 선을 줄이면 비용 감소

- 레지스터로 사용하면 병렬입력-병렬출력사용

실습 및 시뮬레이션

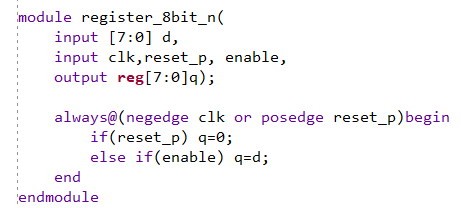

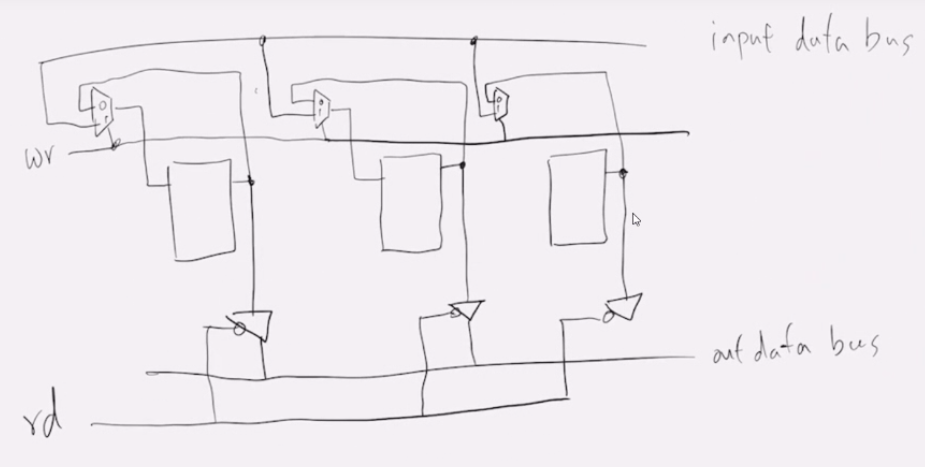

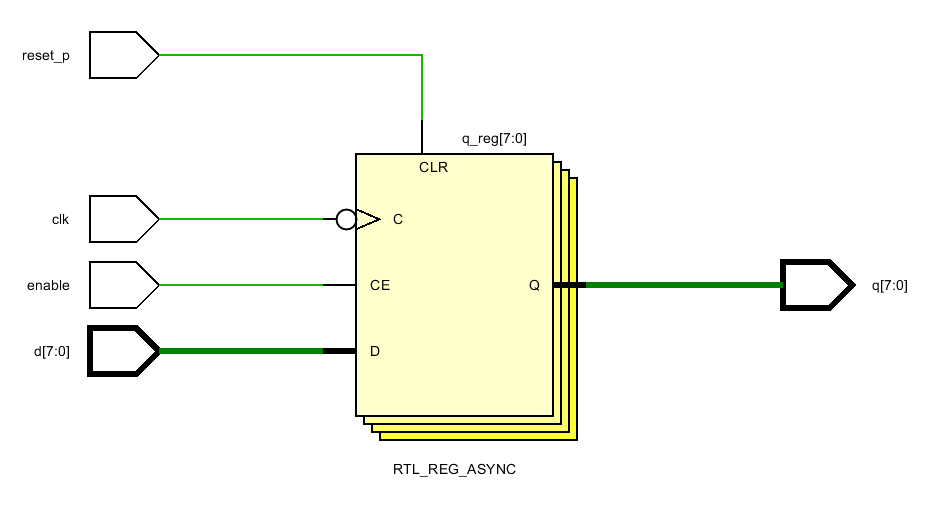

- 8bit register_elaborated Design

- 이는 최종적으로 우리가 설계할

병렬입력 - 병렬출력(PIPO)레지스터입니다. 이는 마지막에 최종적으로 설명하겠습니다.

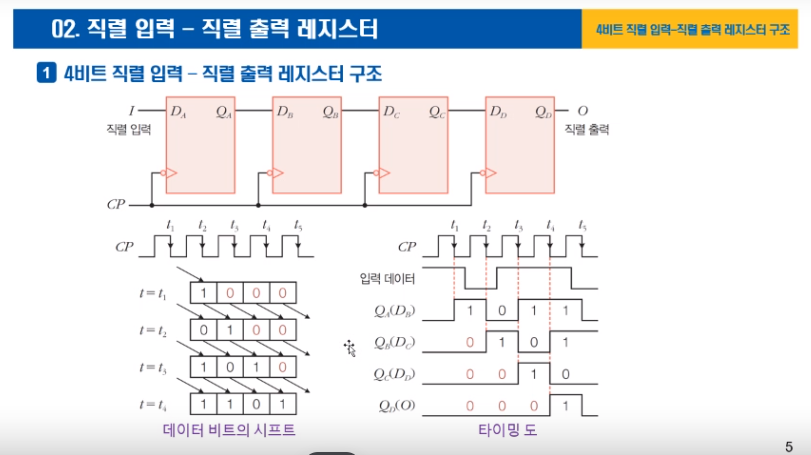

직렬입력-직렬출력(SISO)

Verilog Code 및 시뮬레이션

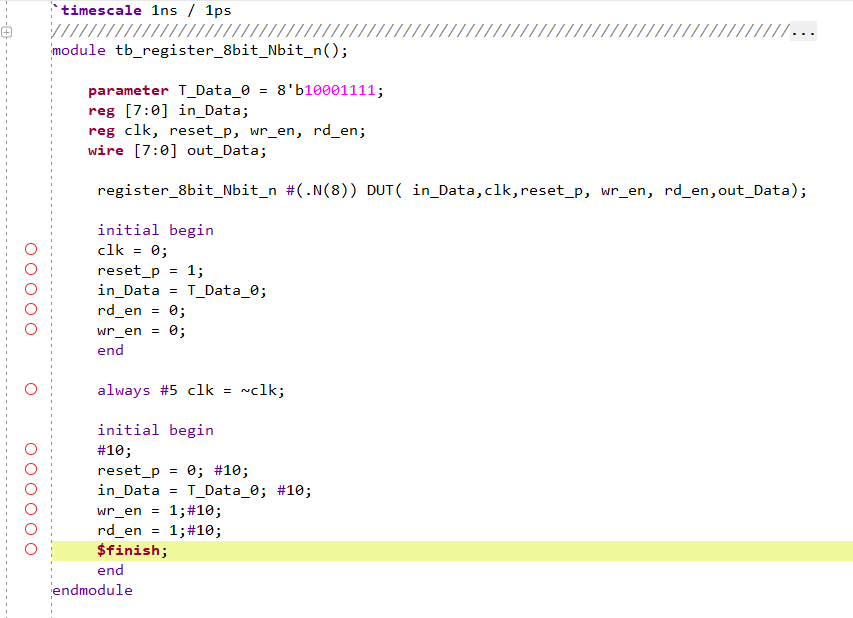

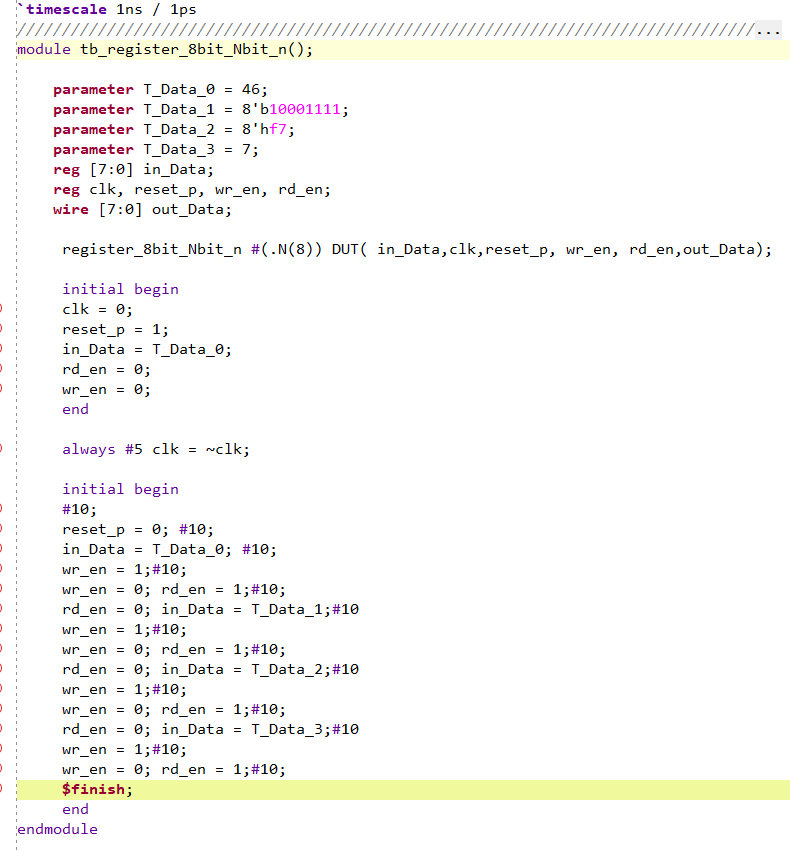

테스트벤치를 사용한 시뮬레이션을 사용하는 방법

테스트벤치 사용이유 : 일일히 시뮬레이션에서 주기 값을 설정하고 하는것이 귀찮기도 하고 원하는 결과를 얻기 위해 시간이 다소 걸리기때문에 원하는 결과를 빠르게 얻기 위하여 테스트벤치에서 설정을 하여 시뮬레이션의 결과를 확인합니다.

1. 테스트벤치의 생성은 Source창에서 "+"버튼을 누르고 simulation source를 생성하여 테스트벤치를 생성해줍니다.

2. 생성된 파일을 클릭하여 보면 내용이 비어있는 module이 생성되고 여기에 시뮬레이션의 주기와 인스턴스 모듈을 추가하여 시뮬레이션을 실행할 수 있습니다

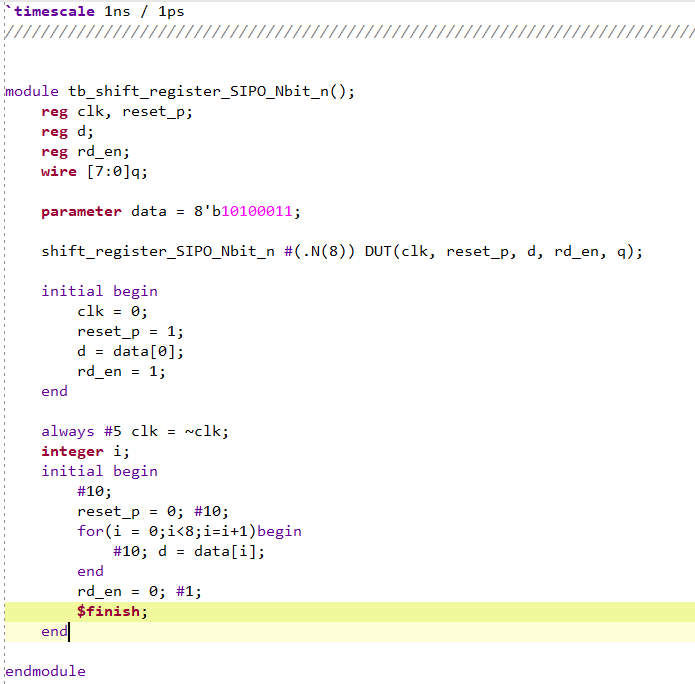

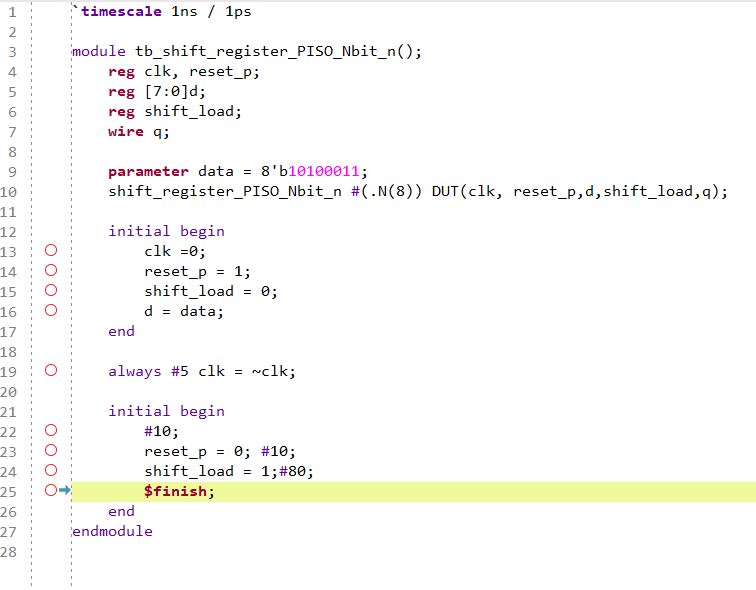

3. 시뮬레이션의 출력은wire, 입력은 reg로 선언하고 parameter data는 입력 d에 들어가는 값을 정의한것이다!. 그리고 인스턴스로 선언한 모듈에서 parameter값 N을 선언하여 비트수를 정의하고 처음 initial문을 사용해 시뮬레이션의 초기값을 설정합니다.

4. reset을 1로 설정하여 입력 d값을 설정해줍니다. 이후 always #5 로 5ns마다 clk을 토글 시켜 clk주기를 만들어줍니다.

5. 또다시 initial문을 사용합니다. 이때의 initial문은초기값 설정이후 시뮬레이션을 진행할때의 동작을 정의합니다. 10ns의 딜레이 이후 reset값을 으로 변견하고 for문을 사용해서 입력 d로 data에 저장된 값을 할당합니다. 그러면 d의 값에는 0101이라는 data값이 들어오게됩니다. 이후 인스턴스화한 모듈의 동작을 실행하여 시뮬레이션 결과를 도출합니다.

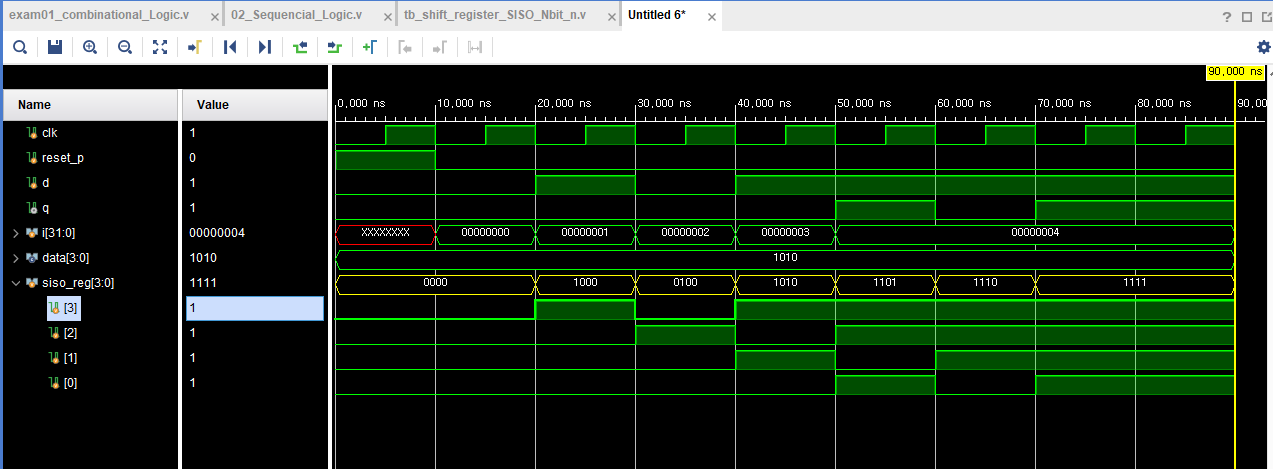

- 위 Verilog Code(테스트벤치, SISO모듈)를 보면 4비트 SISO레지스터를 인스턴스의 parameter로 작성하였습니다. 또한

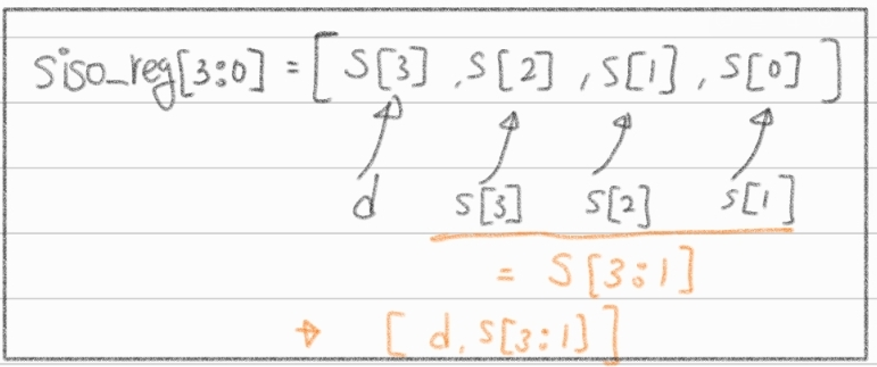

data라는 값에 입력 d에 들어갈 4비트 값을 설정해주었습니다. 처음에 reset 값을 1로 주어 초기화작업을 진행하고 이후 5ns마다 clk값이 토글되게 clk을 설정하였습니다. 이후 10ns의 딜레이를 주고난뒤 입력d에 반복문을 사용해data값을 한비트씩 입력해주었습니다. 결과를 확인해보면 clk의 하강엣지에서 입력d에data가 0번째 비트부터 한비트씩 들어가는 것을 확인 할 수 있습니다. 그러면siso_reg <= {d,siso_reg[N-1:1]};로 인해서siso_reg에는0000으로 초기화되었다가 최상위비트. 즉, 3번째 비트에는 d값이 들어가고 나머지는siso_reg의 1,2,3번째 비트가siso_reg의 2,1,0번째 비트로 들어가게 됩니다! 그러면d입력이 Right쉬프트되는 모습을 볼 수 있습니다!Left 쉬프트를 하게되면

data[i]로 받은d의 입력이 0번째 비트부터 입력이 들어오게된다

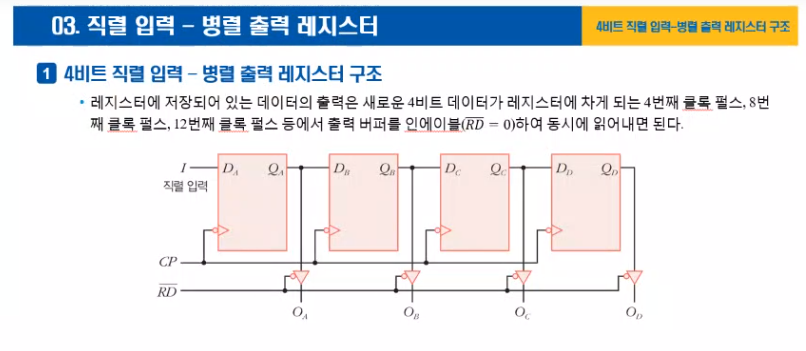

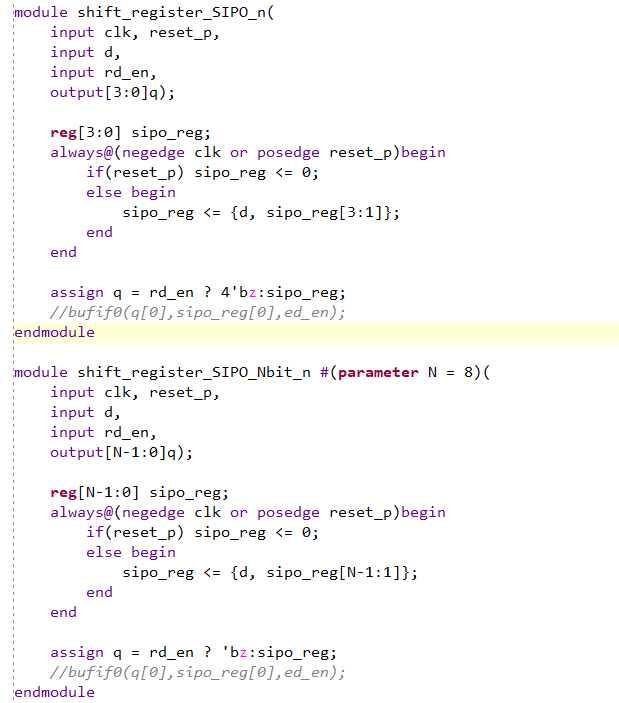

직렬입력-병렬출력(SIPO)

Verilog Code 및 시뮬레이션

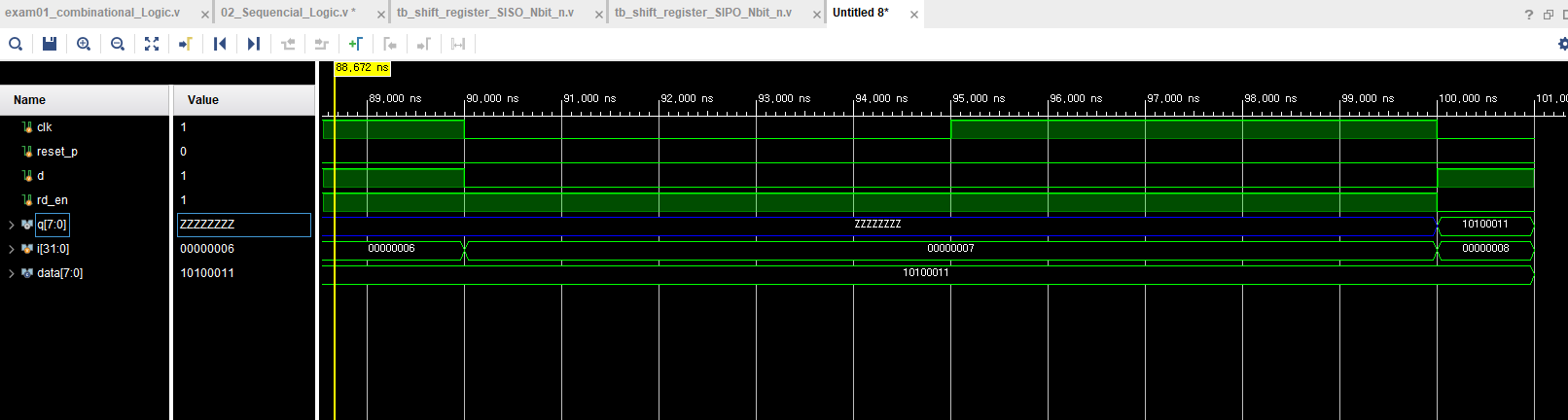

- 원리설명 : 기존의 직렬입력 직렬출력 방식의 회로도와는 다르게 버퍼가 추가되어있다. 이유는 우리가 원하는 출력을 얻기 위해서 한비트씩 입력을 받아올텐데 테스트벤치에서 data라는 8비트의 값을 출력한다고 할 때 한 비트씩 값을 받아서 10100011이라는 값이 출력 값으로 나올때 rd_en을 0으로 하여 출력으로 10100011이라는 값을 출력한다! 즉. 출력에 10100011 이라는 값이 나올때까지 출력은 High임피던스 상태가 출력되지만 출력에는 clock이 돌면서 10100011이라는 값이 출력으로 나오기 까지 기다리고있는것이라고 생각하면 될 것 같다. 그렇다면 우리는 clock주기를 알기 때문에 다음과 같은 결과를 도출할 수 있지만 만약 모른다고 할때는 카운터를 추가해서 설계하여 rd_en을 토글시켜주는 방식으로 설계할 수 있습니다.

즉! 직렬입력 이기에 data값을 반복문으로 한비트씩 받는다. 그래서 8비트 데이터를 모두 출력

q가 받을 때까지 rd_en을 1로 하여 High임피던스 값을 출력하고 data를 모두 받으면 그때rd_en을 1로 하여q값을 출력합니다.

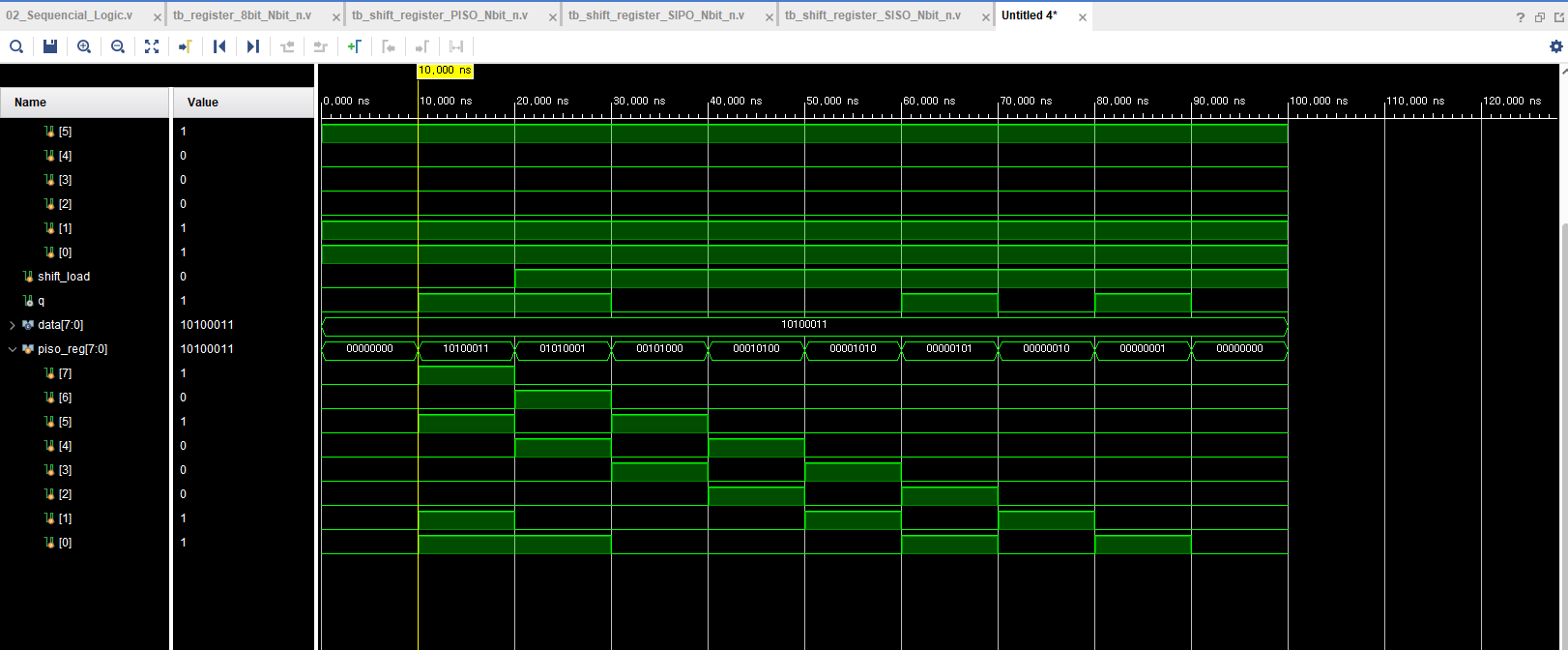

병렬입력-직렬출력(PISO)

- 테스트벤치

- 시뮬레이션결과

- 내일 자료받고 다시.

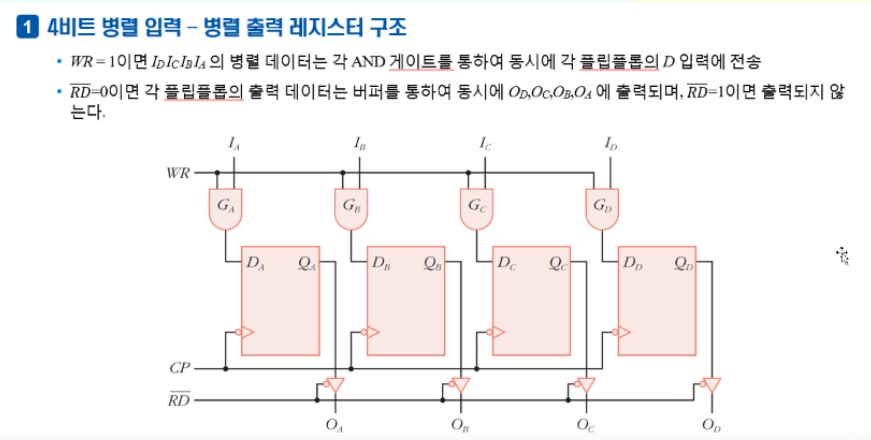

병렬입력-병렬출력(PIPO)

- 우리가 SIPO에서 버퍼를 사용해서

enable신호를 받아서 저장된 값을 출력할지 임피던스 값을 출력할지 정했다. PIPO에선 입력을 받는enable신호와 저장된 데이터를 출력하기위한enable신호가 존재하기에 데이터 값을 읽어 출력하는 신호를rd_enable, 입력받을 병렬 데이터는 AND게이트를 통해 동시에 각 F/F에 전송하도록 설계합니다.Verilog Code 및 시뮬레이션

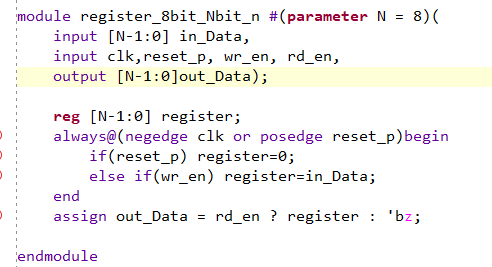

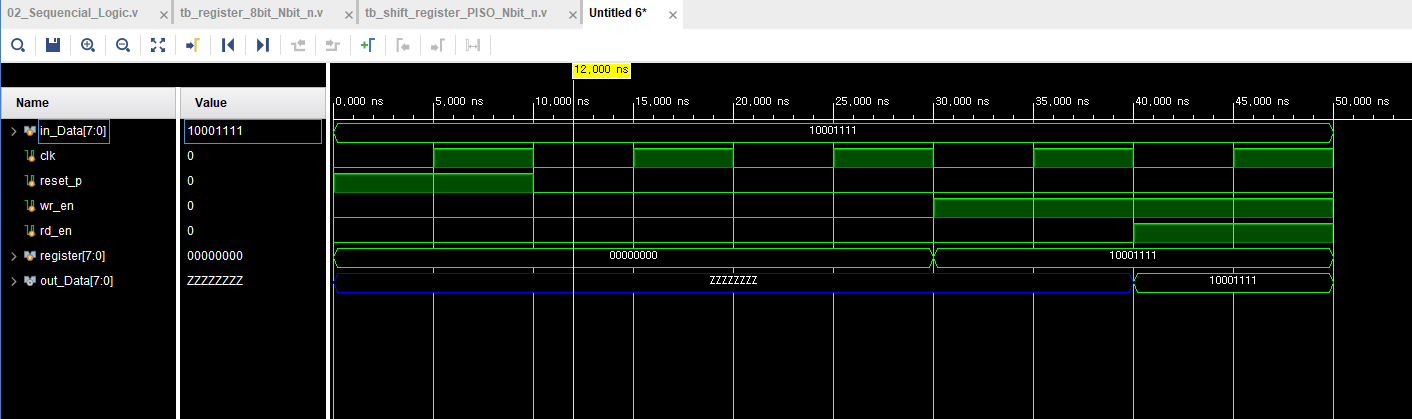

- 실습1

- 실습2

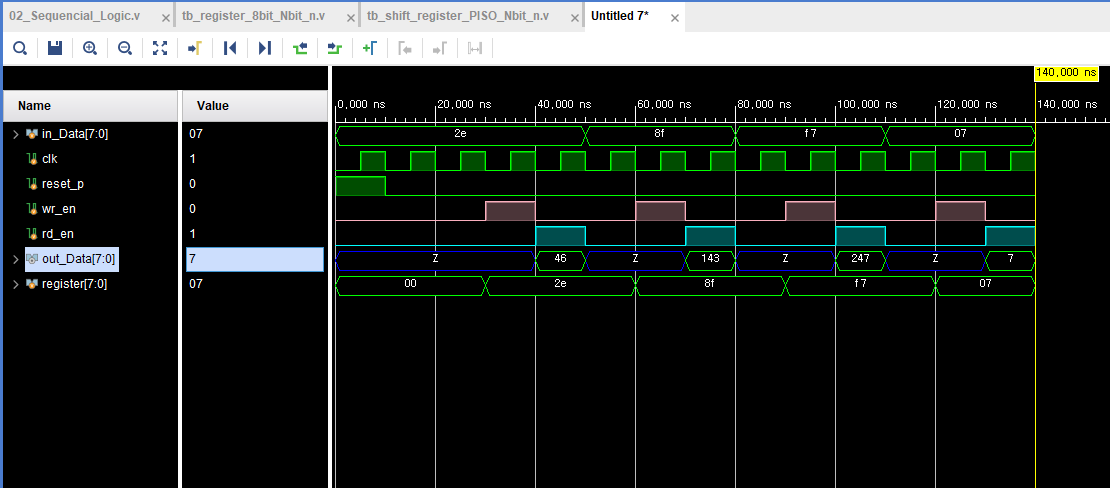

- 원리 설명 : 코드를 보면

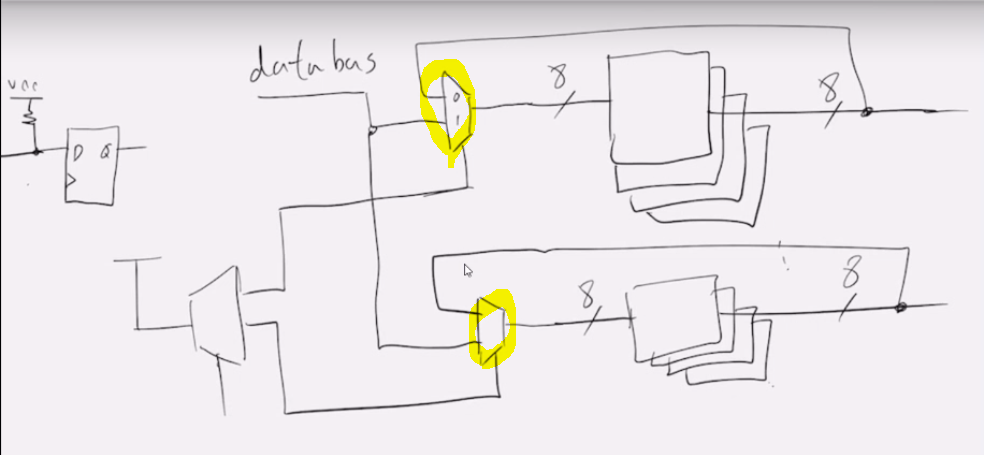

입력(in_Data)에 8비트 입력이 들어가도wr_en이 1이될때register에 입력이 저장이됩니다. 하지만 이때rd_en이 0 이라면출력(out_Data)에는 High임피던스 값이 출력이됩니다. 이때rd_en이 1이된다면 출력에는register에 저장된 값이 출력으로 나오게됩니다. 즉,enable신호에 따라서 값이 저장이되고 출력이되는 레지스터의 기능을 수행합니다. 실습 2는 입력 값에 데이터를 clk의 딜레이를 주고enable신호를 변경해주면서register에 입력된 값을 저장하고 출력하는 실습.data 버스는 양방향으로 묶어서 입력 출력으로 사용

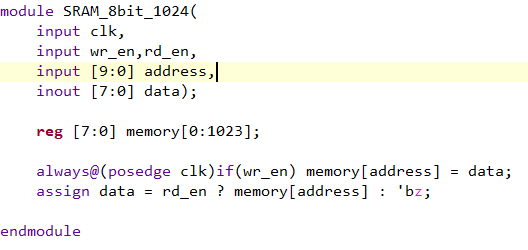

SRAM-8bit

- inout 문 : input, output 2가지로 사용이 가능하다. 입력으로 사용 할 때 임피던스 출력을 기본으로한다. 출력으로 사용할 때 외부 입력을 끊어줘야한다.

reg [7:0] memory[0:1023];

8비트 데이터를 저장하는 메모리를 1024개를 만듬! 이때 메모리를 배열로 선언 베릴로그에서는 배열을 위와같이 선언- 입력주소와 출력주소 같이 쓰게 된다면 버퍼가 필요하다. 왜냐하면 입력받은 데이터를 바로 출력하면 버퍼가 필요 없겠지만, 읽어온 데이터를 바로 출력하지 않고 저장을 했다가 출력을 한다면? 입력받은 주소와 출력주소는 달라야할 것이다. 예를 들면 100이라는 주소로 입력받은 데이터를 200이라는 주소에 저장을하면 출력 할때는 200이라는 주소를 받아서 출력을하면 될 것이다. 이렇기 때문에 버퍼가 필요!!