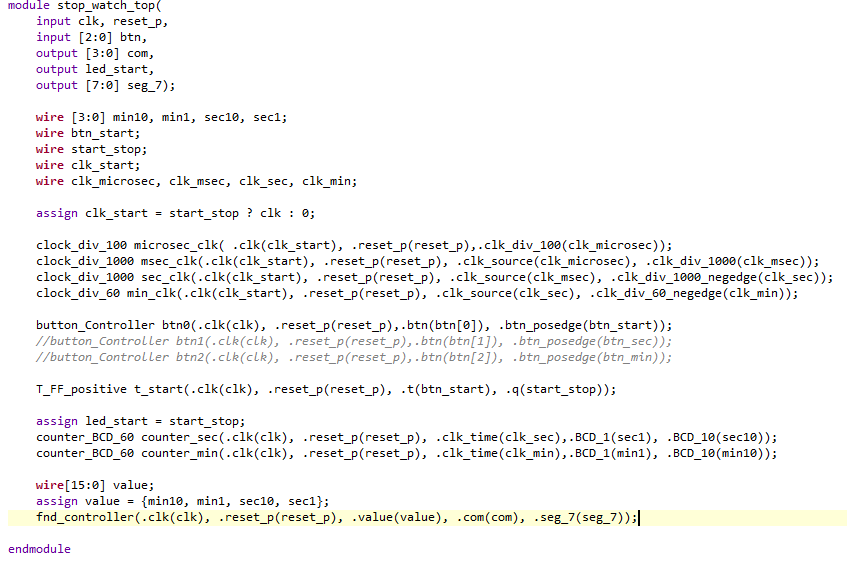

StopWatch

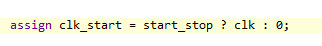

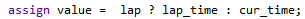

- 스톱워치의 버튼을 누르면 시간이 멈춰야하기때문에 시간을 카운트하는데 필요한 clk을 0으로 두면 clk을 멈춰 시간이 멈추게 할 수 있다. 주기를 초단위로 카운트해주는 clock_div의 주기는 스탑워치기능을 해야하므로 버튼을 누르면 주기가 멈춰야하므로 사진의 clk_start를 주기로 해줘서 T F/F의 출력 즉 버튼이 눌렸을 때 start_stop의 값에 따라 clk, 0이 들어간다.

실행결과

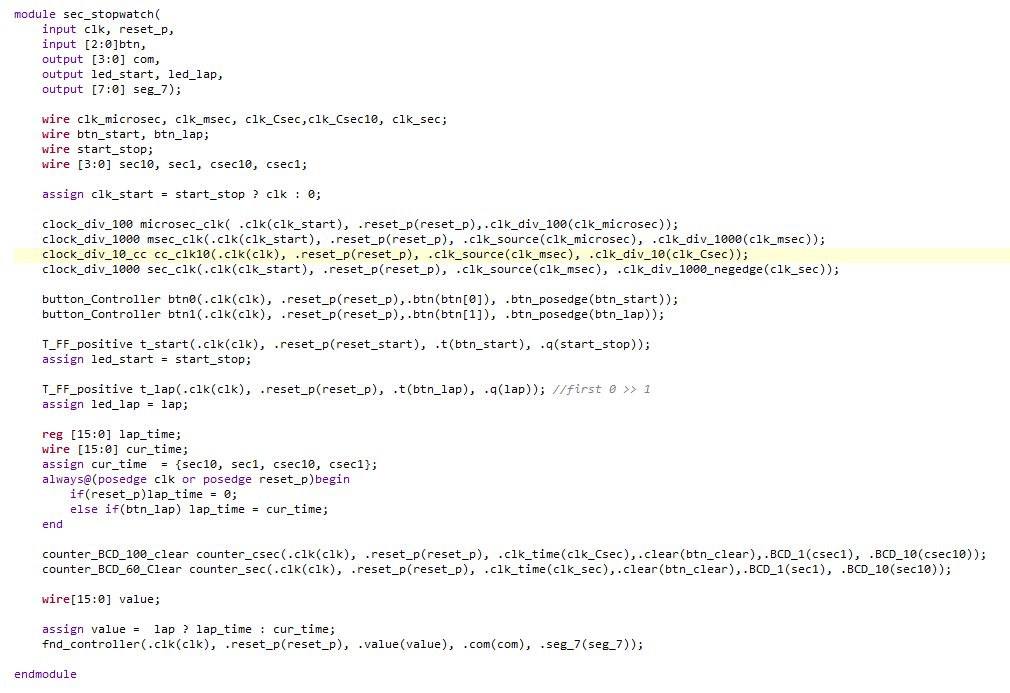

LapTime 기능

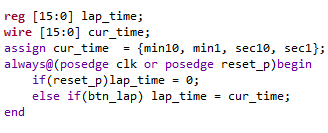

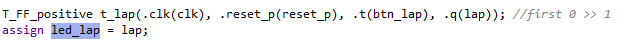

- lap버튼을

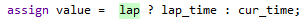

T F/F의 입력으로 받고 출력을lap으로 하여lap버튼이 눌렸을때 led가 들어오게 한다.lap이 눌렸을때 현재 타이머에 나오는 시간을 우리는value의 값(min_10,min_1, sec_10, sec_1)을fnd_Controller로 넘겨서 FND에 표시한다. 또한 이value의 값을cur_time이라는 변수에 저장해둔다. 그러면btn_lap 1일때 즉,lap버튼이 눌렸을때reg로 선언된lap_time에 시간값을 저장해둔cur_time의 값을 할당한다. 이렇게 되면lap버튼을 눌렀을 때 시간이 저장되고value가lap이 눌렸을때는lap_time이value로 들어가서 FND에lap_time에 저장된 타이머 값이 나오게 되고lap버튼이 눌리지 않았으때는cur_time에 카운트되는 카운트 값이 FND에 표시된다. 이때cur_time에는lap버튼이 눌렸다고 주기가 멈추지 않기 때문에 계속Timer가 진행되며 이 타이머 값을 FND에 표시한다.

Lap Btn Clear

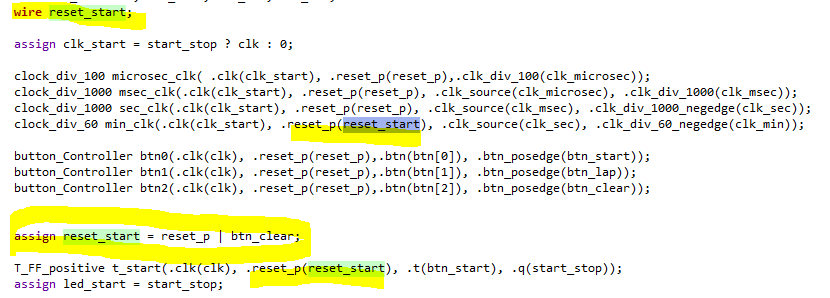

lap버튼을 누르고 클리어를 해주는 기능을 추가했다. 원래reset버튼이 존재하지만reset버튼은 시스템을 초기화하는 기능이므로clear기능을 따로추가해준다!clear버튼을 누르면lap버튼을 누르고lap_time에 저장된 시간을 FND에 표시해주고 클리어 버튼을 누르면 초기화가 된다. 하지만 이렇게되면clock은 초기화가 되지않고BCD카운터만 초기화되기 때문에 60주기clock_div_60또한 초기화 시켜줘야한다. 그렇다면clock_div_60의 리셋 에는reset_p와btn_clear두개를or연산 시켜 mux로 만든reset_start를 연결시켜준다면clear버튼을 누르면 60주기clock_div_60까지 초기화 될 것이다!- 이전엔

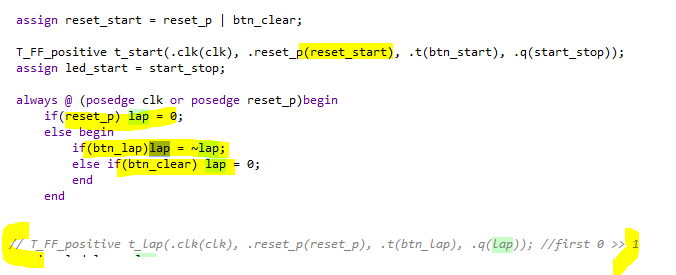

lap버튼을 누르면T F/F의 입력으로 들어가lap기능을 실행했습니다. 하지만 위에서 작성한clear버튼을 실행시키면clear가 되면서 스탑워치 카운터도 멈추지만lap기능을 그대로on되어 있습니다. 이를 해결하기위해T F/F의 인스턴스를 사용하는 것이 아닌T F/F의 기능을 가져와reset_p가 눌렸을때lap = 0이되고,lap버튼이 눌리면lap을 반전시킵니다. 이렇게되면 사진처럼lap의 값에따라lap_time이 들어가거가,cur_time이 들어가는 기능을 그대로 사용할 수 있습니다. 그리고clear가 눌렸을때lap = 0이되면서lap도 기능이off됩니다.

Csec(센티세크) StopWatch

- FND 2개의 7seg에는 10ms 시간이 지나면 1씩 상승되고 나머지 2개의 FND에는 sec가 카운트됩니다.

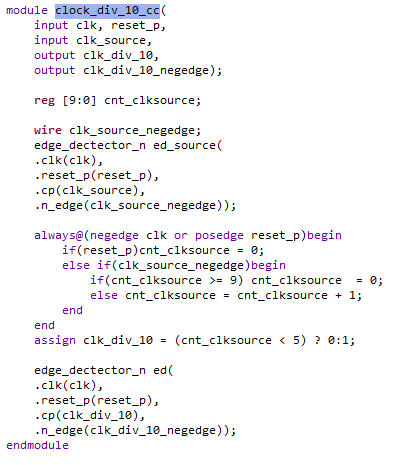

- 원리설명 : 우리가

ms를 타이머에 표현을 해야하는데ms는1000ms = 1sec이다. 4개의 FND에 표현하려면10ms를 100번 카운트해야 1초가 올라갈 것이다. 이를 위해서는 10주기 클럭 카운터가 필요합니다.Clk_msec주기를clk_source로받아서 10번 카운트를 진행합니다.clk_div_10로ms가 5이상이면 1이고 이하면 0을 출력하는데 이를counter_BCD_100_claer에clk_time과 연결하면10ms가 카운트 되었을때 1씩 카운트하여 99까지 증가하여 10ms를 100번 카운트해 1초를 카운트합니다.